關鍵詞:TD-SCDMA;基帶處理;DSP;FPGA

引言移動通信,通信工程師的家園,通信人才,求職招聘,網絡優化,通信工程,出差住宿,通信企業黑名單 {4g1F+m Y F%y&K$h

和傳統的CDMA系統相比,第三代移動通信的最大特點在于能支持多種速率的業務,從話音到分組數據,再到多媒體業務,并能根據具體的業務需要,提供必要的帶寬,數據處理量非常大。然而,對不同速率業務的基帶處理,所需的存儲量、運算量以及處理延時差異很大。因此,采用何種硬件結構才能有效地處理各種業務是本文所要探討的問題。 mscbsc 移動通信論壇擁有30萬通信專業人員,超過50萬份GSM/3G等通信技術資料,是國內領先專注于通信技術和通信人生活的社區。%?5v){/j$|#R9q

本文首先介紹TD-SCDMA系統無線信道的基帶發送方案,說明其對多媒體業務的支持及實現的復雜性。然后,從硬件實現角度,進行了DSP和FPGA的性能比較,提出DSP+FPGA基帶發送的實現方案,并以基站分系統(BTS)的發送單元為例,具體給出了該實現方案在下行無線信道基帶發送單元中的應用。

TD-SCDMA基帶發送方案8n*[7X0o'j4}9X3r+N

TD-SCDMA系統的基帶處理流程如圖1所示。其中,傳輸信道編碼復用包括以下一些處理步驟:CRC校驗、傳輸塊級聯/分割、信道編碼、無線幀均衡、第1次交織、無線幀分割、速率匹配、傳輸信道復用、比特擾碼、物理信道分割、第2次交織、子幀分割、物理信道映射等,如圖2所示。

圖1 TD-SCDMA基帶處理框圖

圖2 傳輸信道編碼復用結構

在圖2中,每個傳輸信道(TrCH)對應一個業務,由于各種業務對時延的要求不同,所以其傳輸時間間隔(TTI)是不同的,TTI可以是10ms、20ms、40ms或80ms。 | 國內領先的通信技術論壇&D'a&d0S2i4B'z實現方案 移動通信,通信工程師的家園,通信人才,求職招聘,網絡優化,通信工程,出差住宿,通信企業黑名單$\5T S.|2m

本文提出了DSP+FPGA線性流水陣列結構的實現方案:使用DSP與大規模FPGA協同處理基帶發送數據。該處理單元以DPS芯片為核心,構造一個小的DSP系統。

在基帶處理單元中,低層的信號預處理算法處理的數據量大,對處理速度的要求高,但運算結構相對比較簡單,因而適于用FPGA進行硬件實現,這樣能同時兼顧速度及靈活性。相比之下,高層處理算法的特點是所處理的數據量較低層算法少,但算法的控制結構復雜,適于用運算速度高、尋址方式靈活、通信機制強大的DSP芯片來實現。 mscbsc 移動通信論壇擁有30萬通信專業人員,超過50萬份GSM/3G等通信技術資料,是國內領先專注于通信技術和通信人生活的社區。'p2s-L(T7i(^'O9U9s*W

DSP處理器利用其強大的I/O功能實現單元電路內部和各個單元之間的通信。從DSP的角度來看,FPGA相當于它的協處理器。DSP通過本地總線對FPGA進行配置、參數設置及數據交互,實現軟硬件之間的協同處理。DSP和FPGA各自帶有RAM,用于存放處理過程所需要的數據及中間結果。除了DSP芯片和FPGA外,硬件設計還包括一些外圍的輔助電路,如Flash EEPROM、外部存儲器等。其中,Flash EEPROM中存儲了DSP的執行程序;外部存儲器則作為FPGA的外部RAM擴展,用于存放數據處理過程中所需的映射圖樣。 | 國內領先的通信技術論壇#\9[ S3V!b5g9v

基帶處理單元的需求估計 mscbsc 移動通信論壇擁有30萬通信專業人員,超過50萬份GSM/3G等通信技術資料,是國內領先專注于通信技術和通信人生活的社區。$}6p;Q,c1~ x5P2`%f

基帶處理單元的需求估計主要包含以下兩個方面:

1.各個業務傳輸通道的數據處理:以對稱情況下無線信道承載的最高業務速率384kbps為例進行分析。傳輸塊大小為336bit,24塊級聯,加上CRC,系統在1個10ms幀內所要處理的最大數據量為8448bit:根據3GPP協議TS 25.222規定的下行數據基帶處理流程(見圖2),并按固定位置復用的方式進行處理,每個數據位必須經過最多13個環節的處理過程,估算平均每環節上每比特的處理要求為23條指令。則10ms內必須完成的處理指令數是:8448×13×23=2525952條。對應的處理能力要求是252MIPS。 3w$M5q!L8U0R6{"t%L%y

2.消息處理:包含消息的解釋、對應控制參數的計算、發給對應的FPGA。估計不超過一條承載64kbps業務的無線信道的基帶數據處理的需求。 3N1]8|1E+l

綜合考慮上述兩個方面,則整個基帶數據處理的等效需求是: )p*u%_ g/l2w)~

(8448+2400)×13×23/10ms=324MIPS

以TMS320C5510為例,其主時鐘能工作在160MHz或200MHz,運算速度達400MIPS。基于C的軟件開發環境和匯編級并行處理的優化程序,優化后的并行執行效率一般為80%,等效的處理能力為320MIPS。可見,若將整個基帶數據處理交給該DSP芯片完成,其處理能力無法滿足整個處理單元的需求,而且,隨著視頻電話、手機電視等大數據量業務的應用,數據處理需求量將更大。因此,在基帶處理的實現方案中,數據量小的業務,如隨路信令、AMR語音業務可由DSP處理;而數據量大的業務,如64kbps、144kbps和384kbps速率的業務,大部分處理環節由FPGA完成。具體實現如下:

?DSP作為主控單元,完成數據提取、消息解析和部分基帶數據處理功能,如第二次交織和成幀等;

?FPGA則在DSP的調度下完成基帶數據處理環節中大部分比較耗時的處理功能,如:CRC校驗、信道編碼、速率匹配等,在接收端可用于Viterbi譯碼、聯合檢測等。 移動通信,通信工程師的家園,通信人才,求職招聘,網絡優化,通信工程,出差住宿,通信企業黑名單.k"i9~!]*?:j*R"?

在384kbps業務信道加隨路信令的處理中,384Rbps業務數據由DSP通過同步高速接口,以DMA方式遞交給FPGA,在FPGA中處理;而隨路信令因其數據量小,在FPGA處理384kbps業務數據時,隨路信令數據在DSP中同時處理。此方法減少了數據處理時間,提高了處理速度。

結語 'x'A,A6?(H/T;}

本文介紹了一個軟硬件結合的設計方案。硬件電路的實際測試表明,該結構不僅在高速率業務的處理時延上符合規范要求,而且對不同類型的業務處理有較強的適應能力,滿足TD-SCDMA系統對多媒體業務傳輸的支持。移動通信,通信工程師的家園,通信人才,求職招聘,網絡優化,通信工程,出差住宿,通信企業黑名單$X8C+S;h9p5|

參考文獻:

1. 李小文,李貴勇,陳賢亮等.第三代移動通信系統、信令及實現. 北京:人民郵電出版社,2003-1www.mscbsc.com#l%H0z)S:V/o%R5` C0s(I

2. 3GPP TS 25.221 : "Physical Channels and Mapping of Transport Channels onto Physical Channels ".[EB/OL]. [2002-12]

3. 張宗橙. 糾錯編碼原理和應用. 北京:電子工業出版社,2003-4]]>

興趣。縱觀世界,現在飛速發展最快的就是電信行業,推成出新的為每一個人帶來了驚喜。也正是由于這

樣的快速發展使得大家對新知識的渴望越來越高。

找工作,很難,找合適工作更難,一般在你面對應聘時都會碰到同樣問題:“你做過什么?”很多人都是

吃虧在沒有得到足夠的實踐經驗上。那么這個時候你最需要的就是一個讓你邊學邊做的東西。

現場可編程門陣列(FPGA),學電子類專業的人也許聽過,甚至很大多數的人都會問:“是啥東西”。其

實這就是現在以及未來電子發展的最大“莊家”。它已經成為電子,通信類專業技術人員所必須掌握的一

項技能。

FPGA/CPLD的應用領域最初為通信領域,但目前,FPGA已完全擺脫了傳統的通信領域而開始大規模向消費

類等領域進軍,除了通信領域的交換機、網絡安全設備、基站等,越來越多的消費類產品采用了

FPGA/CPLD,包括手持學習機、游戲機、網絡播放器、 DTV接收卡、便攜測距儀、數字視頻設備、平板電

視、數字錄像機、魚群跟蹤器等。毫無疑問,靈活可升級性、可編程性和價格的降低成為在消費類產品中

廣泛采用可編程器件的推動力。除此之外,FPGA在自動化控制、汽車電子等領域也越來越多的得到使用。

在不遠的將來,很可能在您所看到的每一個電子設備當中,都有FPGA的存在。

此外,在電子設計領域,中國每年對于FPGA設計人才的需求缺口巨大,FPGA設計人才的薪水也是行業內最

高的。正因為如此,越來越多的高校在教學環節中,把FPGA技術及Verilog語言編程做為重點課程講解,

并安排學生在實驗室中圍繞FPGA做各種創新型設計及畢業設計。這也是目前國內高等/職業教學的大趨勢

-即關注于學生實踐能力的培養,以方便學生的畢業就業。

目前我國教育體制仍以應試教育為主,但教育本身已經處在從應試教育向素質教育轉變的過程中,以電類

專業為例,越來越多的學校開始注重培養學生的專業技能與實際動手能力,在理論教學的過程中插入更多

的實驗課。

目前,美國已有集成電路人才40多萬,中國臺灣地區也有7萬多,而中國內地僅有1萬左右。可見中國渴望

有更多的FPGA人才涌現出來。有人會問“那IC設計又是什么呢?”“FPGA與IC設計有什么聯系呢?”廣義的

講,IC就是半導體元件產品的統稱。自1958年美國德克薩斯儀器公司(TI)發明集成電路(IC)后,隨著硅

平面技術的發展,二十世紀六十年代先后發明了雙極型和MOS型兩種重要的集成電路,它標志著由電子管

和晶體管制造電子整機的時代發生了量和質的飛躍,創造了一個前所未有的具有極強滲透力和旺盛生命力

的新興產業集成電路產業。

回顧集成電路的發展歷程,我們可以看到,自發明集成電路至今40多年以來,"從電路集成到系統集

成"這句話是對IC產品從小規模集成電路(SSI)到今天特大規模集成電路(ULSI)發展過程的最好總結,

即整個集成電路產品的發展經歷了從傳統的板上系統(System-on-board)到片上系統(System-on-a-

chip)的過程。在這歷史過程中,世界IC產業為適應技術的發展和市場的需求,其產業結構經歷了三次變

革。而FPGA就是IC設計中的一個專業化產物。于是,IC產業結構向高度專業化轉化成為一種趨勢,開始形

成了設計業、制造業、封裝業、測試業獨立成行的局面,近年來,全球IC產業的發展越來越顯示出這種結

構的優勢。如臺灣IC業正是由于以中小企業為主,比較好地形成了高度分工的產業結構,故自1996年,受

亞洲經濟危機的波及,全球半導體產業出現生產過剩、效益下滑,而IC設計業卻獲得持續的增長。

IC設計一般分為前端和后端兩種。前端主要負責邏輯實現,通常是使用Verilog/VHDL之類硬件編程語言,

進行行為級的描述。而后端,主要是負責將全端的設計變成真正的Schematic & layout ,流片,量產。前

端就像是做藍圖的,可以功能性,結構性的東西。而后端則是將藍圖變成真正的高樓。所以學習FPGA有幾

點是你必須掌握的,學好 Verilog/VHDL硬件編程語言。

另外值得一提的是IC設計之類的職位薪水都是相當可觀的。但是人才缺口巨大,導致很多企業的對人才的

渴望很高,導致高薪也不一定能招到合適人選。

目前,我正在著手于FPGA技術的推廣,以讓全國的電子設計愛好者都能了解到這一技術。如果對FPGA技術

感興趣的朋友可以加FPGA技術交流群,有什么問題我們一起討論,行業內的信息我們可以一起共享,讓我們一起成長。

]]>

關鍵詞:TD-SCDMA;基帶處理;DSP;FPGA

引言

和傳統的CDMA系統相比,第三代移動通信的最大特點在于能支持多種速率的業務,從話音到分組數據,再到多媒體業務,并能根據具體的業務需要,提供必要的帶寬,數據處理量非常大。然而,對不同速率業務的基帶處理,所需的存儲量、運算量以及處理延時差異很大。因此,采用何種硬件結構才能有效地處理各種業務是本文所要探討的問題。 | 國內領先的通信技術論壇9I2~'f;l+p4n)C(n"C

本文首先介紹TD-SCDMA系統無線信道的基帶發送方案,說明其對多媒體業務的支持及實現的復雜性。然后,從硬件實現角度,進行了DSP和FPGA的性能比較,提出DSP+FPGA基帶發送的實現方案,并以基站分系統(BTS)的發送單元為例,具體給出了該實現方案在下行無線信道基帶發送單元中的應用。

TD-SCDMA基帶發送方案移動通信,通信工程師的家園,通信人才,求職招聘,網絡優化,通信工程,出差住宿,通信企業黑名單 V(e:d'W*?2S$F.V

TD-SCDMA系統的基帶處理流程如圖1所示。其中,傳輸信道編碼復用包括以下一些處理步驟:CRC校驗、傳輸塊級聯/分割、信道編碼、無線幀均衡、第1次交織、無線幀分割、速率匹配、傳輸信道復用、比特擾碼、物理信道分割、第2次交織、子幀分割、物理信道映射等,如圖2所示。

圖1 TD-SCDMA基帶處理框圖

圖2 傳輸信道編碼復用結構

在圖2中,每個傳輸信道(TrCH)對應一個業務,由于各種業務對時延的要求不同,所以其傳輸時間間隔(TTI)是不同的,TTI可以是10ms、20ms、40ms或80ms。:p2q,V h-y0m/_實現方案 &u2r0G3a-Z,^9U

本文提出了DSP+FPGA線性流水陣列結構的實現方案:使用DSP與大規模FPGA協同處理基帶發送數據。該處理單元以DPS芯片為核心,構造一個小的DSP系統。

在基帶處理單元中,低層的信號預處理算法處理的數據量大,對處理速度的要求高,但運算結構相對比較簡單,因而適于用FPGA進行硬件實現,這樣能同時兼顧速度及靈活性。相比之下,高層處理算法的特點是所處理的數據量較低層算法少,但算法的控制結構復雜,適于用運算速度高、尋址方式靈活、通信機制強大的DSP芯片來實現。

DSP處理器利用其強大的I/O功能實現單元電路內部和各個單元之間的通信。從DSP的角度來看,FPGA相當于它的協處理器。DSP通過本地總線對FPGA進行配置、參數設置及數據交互,實現軟硬件之間的協同處理。DSP和FPGA各自帶有RAM,用于存放處理過程所需要的數據及中間結果。除了DSP芯片和FPGA外,硬件設計還包括一些外圍的輔助電路,如Flash EEPROM、外部存儲器等。其中,Flash EEPROM中存儲了DSP的執行程序;外部存儲器則作為FPGA的外部RAM擴展,用于存放數據處理過程中所需的映射圖樣。

基帶處理單元的需求估計

基帶處理單元的需求估計主要包含以下兩個方面: 7W3i3@0g5Z$_9p$v

1.各個業務傳輸通道的數據處理:以對稱情況下無線信道承載的最高業務速率384kbps為例進行分析。傳輸塊大小為336bit,24塊級聯,加上CRC,系統在1個10ms幀內所要處理的最大數據量為8448bit:根據3GPP協議TS 25.222規定的下行數據基帶處理流程(見圖2),并按固定位置復用的方式進行處理,每個數據位必須經過最多13個環節的處理過程,估算平均每環節上每比特的處理要求為23條指令。則10ms內必須完成的處理指令數是:8448×13×23=2525952條。對應的處理能力要求是252MIPS。 mscbsc 移動通信論壇擁有30萬通信專業人員,超過50萬份GSM/3G等通信技術資料,是國內領先專注于通信技術和通信人生活的社區。9D L.p)~$P)U

2.消息處理:包含消息的解釋、對應控制參數的計算、發給對應的FPGA。估計不超過一條承載64kbps業務的無線信道的基帶數據處理的需求。

綜合考慮上述兩個方面,則整個基帶數據處理的等效需求是:

(8448+2400)×13×23/10ms=324MIPS

以TMS320C5510為例,其主時鐘能工作在160MHz或200MHz,運算速度達400MIPS。基于C的軟件開發環境和匯編級并行處理的優化程序,優化后的并行執行效率一般為80%,等效的處理能力為320MIPS。可見,若將整個基帶數據處理交給該DSP芯片完成,其處理能力無法滿足整個處理單元的需求,而且,隨著視頻電話、手機電視等大數據量業務的應用,數據處理需求量將更大。因此,在基帶處理的實現方案中,數據量小的業務,如隨路信令、AMR語音業務可由DSP處理;而數據量大的業務,如64kbps、144kbps和384kbps速率的業務,大部分處理環節由FPGA完成。具體實現如下: mscbsc 移動通信論壇擁有30萬通信專業人員,超過50萬份GSM/3G等通信技術資料,是國內領先專注于通信技術和通信人生活的社區。;C0j6H!C4k"t%y&x:u

?DSP作為主控單元,完成數據提取、消息解析和部分基帶數據處理功能,如第二次交織和成幀等;

?FPGA則在DSP的調度下完成基帶數據處理環節中大部分比較耗時的處理功能,如:CRC校驗、信道編碼、速率匹配等,在接收端可用于Viterbi譯碼、聯合檢測等。 ,q4H8t r&I#g2o3y.h+q

在384kbps業務信道加隨路信令的處理中,384Rbps業務數據由DSP通過同步高速接口,以DMA方式遞交給FPGA,在FPGA中處理;而隨路信令因其數據量小,在FPGA處理384kbps業務數據時,隨路信令數據在DSP中同時處理。此方法減少了數據處理時間,提高了處理速度。

結語 MSCBSC 移動通信論壇9D-Y0D"U9S9](`2W

本文介紹了一個軟硬件結合的設計方案。硬件電路的實際測試表明,該結構不僅在高速率業務的處理時延上符合規范要求,而且對不同類型的業務處理有較強的適應能力,滿足TD-SCDMA系統對多媒體業務傳輸的支持。

]]>

我也打算投入FPGA的方向。并為之努力。

下學期就開始,打算先從VHDL和ISE環境學起(我們實驗室用的是XILINX)。

二。第一個問題:FPGA方向獨立嗎?有沒有必要再精通ARM或DSP?

上嵌入式課時老師說嵌入式(主要指ARM),DSP,FPGA,只要精通一個就可以無憂矣。

導師分給自己的項目就是用C6000的芯片,不過,自己不想搞DSP。師兄說,那個好像通信專業更有優勢,我們計算機專業沒有專業優勢,找工作也不沾光。

一心想走FPGA方向,但目前的了解,在工程中FPGA技術是否可以獨立于ARM和DSP還未可知,經常在ARM或DSP的板子上看FPGA當配角。雖然知道FPGA像個畫板,畫什么是什么,但應該很少有人把ARM核寫在FPGA上,出于成本考慮的話(初學者,童言無忌,有誤請一一指正)。

三。第二個問題:FPGA的學習要點,如何就算精通?

感覺,首先要把環境學好。欲善其事,先利其器。

然后,VHDL語言本身好學,就像C/C++。語言本身不是問題,編程的經驗才是重點。這也可以多通過多練習和在工程中學習而得到成長。

其他的,實在卻沒有什么想法了。只是想多實踐,幫師兄們多用FPGA做些驗證。

不知道,過來人有什么好的想法和經歷經驗可以分享?

四。第三個問題:目前FPGA行業狀況如何?

學FPGA的技術不止是熱愛(我熱愛硬件的相關技術,包括ARM或DSP或C51等等,如果不是時間精力所限,盡可以都多學學~~),更現實的目標是畢業后找到不錯的工作,能夠把這個喜歡的方向延續下去。

不知道FPGA行業里實際在做些什么什么工程或事情,希望了解者舉幾個例子,說說一二。

另外就是,FPGA方向有哪些不錯的公司。清楚的仁兄就給推薦下。以后也好多留意它們做的事情,和要求等,向那個方向努力。

五。致謝

本來這個帖子這么多問題,應該設為“求助”貼才合適。但我有意設成了討論的主題,是希望有所了解的仁兄都能來說說自己的想法,大家各抒己見,終能使新人老手在思考中有所小悟,少走些彎路或清楚些未來的道路。我也談了自己的想法,如前所言“初學者,童言無忌”,有什么不妥的大家一起討論。

]]>

DDS(直接數字頻率合成)技術是解決這一問題的最好辦法,DDS技術從相位的概念出發進行頻率合成,采用數字采樣存儲技術,可以產生點頻、線性調頻、ASK、FSK等各種形式的信號,并且其幅度和相位一致性都很好,具有電路控制簡單、方便靈活、可靠性高、相位精確、頻率分辨率高、頻率切換速度快、輸出信號相位噪聲低、易于實現全數字化設計等突出的優點。

在雷達系統中采用DDS技術可以靈活地產生不同載波頻率、不同脈沖寬度、不同脈沖重復頻率等參數的信號,為雷達的設計者提供了全新的思路。

1 DDS技術的基本原理

DDS是一種全數字化的頻率合成器,由相位累加器、正弦波形ROM存儲器、D/A轉換器和低通濾波器構成,如圖1所示。

|

|---|

輸出信號波形的頻率表達式為:

式中,fclk為參考時鐘頻率,Δφ為相位增量,表現以多大的間隔對信號相位進行累加,也稱為頻率控制字,N為相位累加器的位數。

由式(1)看出,DDS的頻率分辨率即最低頻率為:

所以,只要N足夠大,DDS可得到很小的頻率間隔,要改變DDS的輸出信號的頻率,只要改變Δφ即可。

可見,當參考時鐘頻率給定后,輸出信號的頻率取決于頻率的控制字,頻率分辨率取決于累加器的位數,相位分辨率取決于ROM的地址線位數,幅度量化取決于ROM的數據字長和D/A轉換器的位數。

2 基于FPGA的DDS軟件編程產生線性調頻信號

利用專用DDS芯片是目前比較流行的信號產生方法,專用DDS芯片把所有功能集中在一塊芯片上,需要設計者依次為平臺進行開發[3]。而基于FPGA(現場可編程門陣列)的DDS軟件編程則根據DDS技術的基本原理,充分利用了FPGA作為大規模芯片的資源優勢和高速運算能力,除了能產生專用DDS芯片所具備的單頻連續波、非連續波、各種形式的線性調頻信號以外,還可以借助FPGA龐大的資源優勢和內部存儲器,使非線性調頻等更復雜的信號更容易實現。

2.1 系統構成

在具體實現過程中主要采用一塊基于FPGA的雷達信號處理卡,既可以采集來自雷達接收機的中頻、視頻信號并對其進行數字信號處理,又可以自身模擬產生雷達中頻、視頻信號進行數字信號處理或不處理直接送往雷達信號處理機。雷達信號處理卡的硬件電路結構圖如圖2所示。

|

|---|

FPGA采用Xilinx公司的10萬門FPGA芯片XC2S100E,其配置芯片為Xilinx公司的1Mbit容量PROM芯片XC18V01,以主動串行方式對FPGA進行上電配置,A/D、D/A轉換器分別為ADI公司12位高速A/D數轉換芯片AD9224與14位高速D/A轉換芯片AD9764。SRAM采用Cypress公司的256k×16bits SRAM芯片CY7C1041。

設計中利用FPGA實現32位/33MHz的PCI接口邏輯,進行實時信號采集和傳輸控制,由于FPGA具有層次化的存儲器系統,其基本邏輯功能塊可以配置成16×1、16×2或32×1的同步RAM,或16×1的端口同步RAM。因此,可以在FPGA內部配置高速雙口SAM用來作為信號傳輸的數據緩沖器。同時,為了節省FPGA的內部邏輯資源,在FPGA外圍配置了適當的SRAM用來存儲數據。

結合本處理卡的結構特點,硬件采用FPGA與高速D/A方案產生線性調頻信號,在FPGA內部實現DDS電路,FPGA輸出全數字線性調頻信號送往高速D/A轉換器得到最終的模擬線性調頻信號,由于本處理卡采用PCI總線結構,因此可通過計算機實時修改線性調頻信號的參數設置,改善了人機接口,提高了系統的靈活性。

2.2 FPGA軟件編程實現線性調頻信號的原理

圖1所示的DDS電路產生的是固定頻率的正弦波信號,信號頻率受相位增量Δφ控制,若要產生線性調頻信號,則必須實時改變Δφ,使Δφ根據頻率步進量fstep而線性變成,因此,基于FPGA軟件編程實現線性調頻信號時,需要在FPGA內部實現頻率累加器、相位累加器、正弦波形ROM存儲器等電路,FPGA軟件編程實現線性調頻信號的原理圖如圖3所示。

|

|---|

產生線性調頻信號時,每來一個時鐘脈沖,軟件編程控制頻率累加器產生線性增加的瞬時頻率,然后經過相位累加器運算輸出線性調頻信號的瞬時相位,以此相位值尋址正弦值存儲表,通過查表得到與相位值對應的幅度量化值;在下一個周期來臨時,頻率累加寄存器一方面將在上一個時鐘周期作用后所產生的新的頻率數據反饋到頻率加法器的輸入端,以使頻率加法器繼續累加,頻率累加的瞬時值與上一個周期相位累加器反饋到相位加法器輸入端的數據累加,然后再依此周期累加的相位值重新尋址正弦值存儲表,得到對應的幅度量化值。依此循環,幅度量化值經累加,并經D/A轉換器得到連續的階梯波,經低通濾波器濾除高頻分量,最后即可得到所需線性調頻信號[4]。

已知系統工作時鐘fclk、頻率累加器與相位累加器位數N,要產生中頻為F0、帶寬為B、時寬為T的線性調頻信號,其頻率步進編程見圖4。在FPGA軟件編程時只需計算起始頻率fstart和頻率步進量fstep即可。

|

|---|

起始頻率fstart和頻率步進量fstep計算公式如下:

|

|---|

VHDL語言中數值表示方法采用二進制,所以通過式(3)、式(4)計算的結果二進制數,無量綱。

經過頻率累加器輸出的是嚴格線性增長的瞬時頻率。在實際過程中,相位累加器的輸出是經過相位截斷再進行尋址,從而引入了一定的相位誤差,雖然這一誤差會影響到線性調頻信號的線性度,但是調頻斜率為相位的二次導數,相位截斷誤差本身已很小,所以對調頻線性度的影響就更小了。

2.3 FPGA的軟件編程實現線性調頻信號的部分程序

本程序完全遵照上述的FPGA軟件編程實現現行調頻信號的原理編寫,采用VHDL語言來進行描述,以下是部分源程序。

1)線性調頻脈沖信號產生(系統時鐘頻率40MHz,線性調頻脈沖信號脈寬25μs,中頻1.5MHz、調頻帶寬1MHz)

dds_fstart<=“000001100110011001100110”,//設置線性調頻信號初始頻率為1MHz,由式(3)可計算出

dds_phase_start<=“0000000000000000000000”;//設置線性調頻信號初始化初始相位為0

dds_fstep<=conv_std_vector(419,43);//設置線性調頻信號頻率步進為419.43,對應調頻帶寬為1MHz,時寬為25μs,由式(4)可計算出

|

|---|

|

2.4 與DDS專用芯片方法的比較

由于基于FPGA的DDS軟件編程同樣利用了DDS技術的基本原理,主要部分均由頻率累加器、相位累加器、相位幅度轉換器組成,所以與DDS專用芯片方法的方法一樣,所產生的信號具有可通過編程靈活控制參數、具有高的調頻線性度、頻率穩定度等DDS技術特有的優點。但是與DDS專用芯片方法相比,有自己的優勢和不足。

由輸出信號的頻率分辨率Δf=fclk/2N可知,本系統的參考時鐘頻率為fclk為40MHz,相位累加器的位數N為24位,而DDS專用芯片,如AD9854的相位累加器的位數N為48位,雖然本系統產生的線性調頻信號在精度和速度上略有不足,但已能基本滿足絕大多數系統的使用要求。若要產生更低頻率及更精確的波形,可以提高分辨率并相應減小基準時鐘,這在FPGA中實現起來相比比較容易。

另一方面,基于FPGA的系統功能完全取決于設計需求,可以復雜也可以簡單,而且FPGA芯片還可在系統現場升級,使系統具有較大的可擴展性。另外,將DDS設計嵌入到FPGA芯片所構成的系統中,只是充分利用了FPGA的系統的軟件資源,其系統的硬件成本并不會增加多少,而購買專用DDS芯片則使系統的硬件成本和體積等增加很多,因此,采用基于FPGA的DDS軟件編程技術具有較高的性價比,并提高了系統的性能和可靠性。

3 實驗結果

首先對VHDL代碼進行了時序仿真,然后將編譯綜合后的BIT文件下載到FPGA芯片中進行系統聯調。實驗表明,采用FPGA軟件編程技術較好地實現了線性調頻信號的產生,而且信號波形比較穩定。

圖5為利用Modelsim軟件對比設計所產生的信號進行仿真得到的時序仿真圖,從中可以看出,在每個觸發周期內,所產生信號的變成頻率在不斷線性增加,可較明顯地看出產生的是線性調頻信號。

|

|---|

圖6為實際調試過程中產生的一個脈寬為7μs,中頻為7.5MHz,調頻帶寬為5MHz的線性調頻脈沖信號在示波器上的截圖。從圖中可以看出,本系統所產生的線性調頻信號取得了較好的效果,能夠滿足實際工程中的應用,在雷達系統中有較好的應用前景。

本文原理以及基本系統亦可用于構成產生相位編碼脈沖信號等其他形式的復雜雷達信號形式,具有較大的可擴展性。

| 以下內容含腳本,或可能導致頁面不正常的代碼 |

|---|

| 說明:上面顯示的是代碼內容。您可以先檢查過代碼沒問題,或修改之后再運行. |

電子密碼鎖系統主要由電子鎖體、電子密匙等部分組成,一把電子密匙里能存放多組開鎖密碼,用戶在使用過程中能夠隨時修改開鎖密碼,更新或配制鑰匙里開鎖密碼。一把電子鎖可配制多把鑰匙。

語音方面的廣泛應用,使得具有語音播放的電子密碼鎖使用起來更加方便。語音密碼鎖的體積小、保密性能好、使用方便,是用在保險箱、電話或是房門上不可少的部分。

本文介紹的基于FPGA的語音密碼鎖電路具有顯示接口,顯示時可以是明文也可以是密文星號。由于FPGA具有ISP功能,當用戶需要更改時,如增加口令位數和更改口令權限管理時,只需更改FPGA中的控制和接口電路,利用EDA工具將更新后的設計下載到FPGA中即可,無需更改外部電路,這就大大提高了設計效率。而且采用FPGA設計的電子密碼鎖與單片機控制的電子密碼鎖相比結構簡單、具有更高的系統保密性和可靠性。這種基于FPGA的電子密碼鎖可以應用在辦公室、倉庫、賓館等人員經常變動的場所。

語音密碼鎖系統的設計

本設計中的語音密碼鎖具有如下功能:

①電子密碼鎖部分功能如下:

密碼輸入:按下一個數字鍵,就輸入一個數值,并在顯示器的最右方顯示出該數值,并將先前已經輸入的數據依次左移一個數字位置,當超出四位時鎖定數字鍵,不響應其輸入值。

密碼清除:按下此鍵可清除前面所有的輸入值,清除成為“- - - -”。

數字位退格:按下此鍵可清除最低的數字位,并使各位向右移。

密碼設定:按下此鍵時會將目前的數字設定成新的密碼。

激活電鎖:按下此鍵可將密碼鎖上鎖。

解除電鎖:按下此鍵會檢查輸入的密碼是否正確,密碼正確即開鎖,如果密碼錯誤次數超過三次,系統將進入鎖定狀態。

萬能密碼:為了怕使用者忘記密碼,系統維護者可考慮設計一個萬用密碼(8421),不論原先輸入的密碼是什么,只要輸入萬用密碼即可開鎖。

②語音部分功能如下:

錄音:能根據所需的內容實現語音錄制,為播放準備。

放音:根據系統所處的不同時段以及不同的按鍵值播放不同的語音提示,以方便使用者操作。

報警:在密碼輸入錯誤時,發出報警音。

硬件設計

根據整個系統的技術要求,選擇硬件電路的設計方案,整個系統原理如圖1所示。

根據整個電路的結構可分為幾個功能模塊:顯示模塊、電子鎖狀態指示燈(LED綠:密碼正確開鎖,LED紅:進入死鎖狀態,LED黃:密碼錯誤)、鍵盤模塊、語音模塊等。下面分別對各個功能模塊進行詳細的介紹。

顯示模塊

本設計主要是設計一個四位的語音密碼鎖,因此選擇了四位共陰數碼管,對輸入數字與系統狀態進行顯示,其接口如圖2所示。

鍵盤模塊如圖3所示。以上采用的是4×4矩陣式鍵盤,可劃分為:數字鍵與功能鍵。其中,功能鍵分為:輸入、退格、清除、確定、密碼設定、上鎖。

語音模塊如圖4所示。

根據所需的內容由柱式話筒MIC實現語音錄制,同時也可以由ISD2560芯片的11引腳AUX IN 通過計算機的聲卡輸出端進行語音錄制(效果差不多)。在整個系統中由主芯片對ISD2560芯片進行控制,以實現不同時段以及不同按鍵值播放不同的語音提示。

軟件設計

本設計中,采用自頂向下的層次化結構設計方法,把整個系統劃分為幾個子模塊,最后完成頂層電路的設計。子模塊可分為:時鐘模塊、顯示子模塊、鍵盤子模塊、語音子模塊。當各個功能子模塊設計完畢,頂層模塊的設計就變得簡單了,就是將各個子模塊連接起來,其電路模型如圖5所示。

結語

本設計中采用了ALTERA公司的 EP1C3T144芯片進行設計,實際測試表明系統的各項設計要求均得到滿足并且系統工作良好,該設計采用了SOPC技術和FPGA,幾乎將整個系統下載于同一芯片中,實現了所謂的片上系統,可以極大減少其它分立元件或其它芯片的使用,有效地縮小了線路板面積,增加了系統的可靠性,大大縮短了系統開發的周期。克服了傳統電子密碼鎖可靠性差、價格高的缺點,提高了系統的性價比。由于采用VHDL語言進行層次化設計,用軟件實現硬件電路,具有良好的可移植性,可隨時在線更改邏輯設計及有關參數,充分體現現場可編程器件的優越性。

FPGA是一個內含可重設組態之閘門陣列邏輯電路矩陣的設備。當工程師設定FPGA的組態時,內部電路便連接,將軟件的應用轉換為硬件布制。和處理器不同的是,FPGA采用專屬硬件來處理邏輯,而且沒有作業系統。FPGA技術提供許多優勢,包括自訂I/O計時和同步化、20 MHz控制迴圈速率、專屬硬件的穩定性,以及數字信號處理和分析。

傳統上,工程師需要擁有硬件設計工具和VHDL等程式語言的龐大知識,才能設計FPGA的功能。.CompactRIO中的FPGA使用National Instruments LabVIEW圖形化開發工具來設計程式,因此工程師可以用很短的時間,自行訂定并重設CompactRIO中的FPGA的組態。當系統功能需要改變時,開發人員只需將新的NI LabVIEW程式下載到FPGA,即可改變CompactRIO的特性。

FPGA運用于載具內I/O的彈性及效能

CompactRIO提供廣泛的I/O模組,用于連接至任何載具內感測器、致動器,以及網路。工程師可以完全自行設定每一項應用的I/O時間、同步作業、處理,以及控制速率。

I/O 感測器和信號類型 模組 通道 特殊功能

溫度 熱電偶 NI 9211 4 24位元解析度,15 S/s

RTD NI 9217 4 24位元解析度,100 S/s

聲音和震動 IEPE感測器(加速計/麥克風) NI 9233 4 24位元解析度,每個通道50 kS/s,同步, IEPE調節,反失真

張力 橋接式感測器(應力規,壓力傳感器) NI 9237 4 24位元解析度,每個通道50 kS/s,同步,全/半橋(full-/half-bridge)

電壓 ±200 mV至±10 V NI 9205 32 16位元解析度,250 kS/s

±60 V NI 9221 8 12位元解析度,800 kS/s

燃料電池(Fuel cell) ±200 mV至±10 V NI 9206 32 16位元解析度,250 kS/s, 600 V DC CAT I 隔離

CAN通訊 雙埠高速CAN介面 NI 9583 2 雙埠高速CAN模組

表一:CompactRIO的載具內I/O

取樣速率的彈性

由于FPGA直接連接至每一個I/O模組,因此工程師可以設定CompactRIO中每一個模組的取樣速率。這項功能為系統提供無與倫比的時間彈性。在一部CompactRIO系統中,工程師可以用10 S/s的速度擷取溫度量測,同時以50 kS/s的速度監督震動量測。工程師也可以直接在FPGA上進行資料取捨,在同一個I/O模組中設定不同的通道,采用不同的速率。

I/O同步化

FPGA技術應用于載具內資料擷取及測試方面的優點之一,就是能夠在任何I/O模組之間獲得決定性的硬體同步化。舉例來說,NI 9853 CAN介面模組和任何模擬或數字輸入模組都可以執行讀取動作,以獲得毫微秒(nanosecond)解析度的同步測量功能。運用這種同步化功能,測試工程師可以從一部特定的CAN設備(例如電子控制元件ECU或致動器)讀取數值,再將數值和來自同步執行的模擬或數字輸入埠的資料作比較。

40 MHz的決策

對于快速建立原型之類的控制應用而言,FPGA客制硬件的效能會以極快的速度進行密閉迴圈控制。只要使用任一種I/O模組,工程師就可以設定CompactRIO,使它對輸入的CAN、模擬或數字資料進行反應,決定速度可以高達40 MHz。過去這一類的應用需要使用高價的客制硬件,才能獲得這樣的效能。

「過去我們至少要花兩年的人力和五十萬元,才能使用自行設計的硬體開發出類似的ECU原型建立系統。就這個專案而言,設備的成本(包括機車和CompactRIO)是一萬五千元。此外,我們大約花了三個月的人力在這項專案上。CompactRIO和LabVIEW Real-Time提供我們需要的穩定性和精確計時資源,而且系統有足夠的堅固性,可以承受操作環境的高溫和高震動。」

–Drivven, Inc.總裁Carroll G. Dase

感測器層級的信號處理及分析

CompactRIO中的FPGA就像一個平行處理引擎,因此工程師可以對任何感測器信號執行高級信號處理和分析。舉例來說,解譯轉速計信號通常需要大量的處理器運算能力。工程師可以設計FPGA,讓它在硬件中解譯多種感測器信號,允許網路上的CPU去執行其它的處理作業。此外,工程師也可以使用LabVIEW數字濾波器設計工具組(Digital Filter Design Toolkit),輕松地在FPGA硬件中使用高級數字濾波器。

獨立操作及網路化操作

CompactRIO控制器內含一顆嵌入式即時處理器,用于智慧型獨立運作;包含乙太網路及序列埠,可以連接至主電腦和週邊;并且使用LabVIEW Real-Time軟體進行決定控制、資料記錄,以及分析。此外,你可以將乙太網路埠與內附的網頁及檔案伺服器結合,這樣操作者就可以輕易地取用在控制器上執行的嵌入式程式。由于它具備兩個9至35 V(操作時為6至35 V)電源供應輸入,因此工程師可以直接用載具電瓶提供CompactRIO電力。控制器內含最多512 MB的非永久存儲器,用于載具內資料記錄之用。

圖二:CompactRIO執行獨立或網路化操作,供載具內應用。

輕巧而堅固的封裝,適用任何載具內環境

CompactRIO的機械設計創造出一款能夠承受任何嚴苛的載具內測試環境(例如亞利桑那州測試場的干熱天候)的系統。CompactRIO保持輕巧的體積、低電力消耗,以及-40至70 oC的作業溫度范圍,并通過多種工業認證和規章。四個插槽的可重設組態嵌入式系統的體積是179.6 x 88.1 x 88.1公釐(7.07 x 3.47 x 3.47 吋),重量只有1.58公斤(3.47磅)。八個插槽的系統加上32個通道的I/O模組,最多可以在一部系統中提供256個I/O通道。此平臺最多可承受50g的撞擊,最高2,300 Vrms 隔離(承受力),而且具備國際性的安全性、EMC,以及環境認證。

「CompactRIO平臺的輕巧體積和堅固性使它成為載具內測試系統的理想選擇,能夠在我們的測試過程的嚴苛環境中生存下來。」

–PACCAR系統工程師 Andrew Leslie

建立客制的載具內I/O

運用CompactRIO系統的開放性,工程師可以迅速開發客制模組,以滿足特殊的載具內I/O需求。CompactRIO模組開發工具組提供授權許可、設計指南,以及LabVIEW FPGA軟體工具的存取能力,以建立客制模組。協力廠商推出載具內擷取及控制模組,為CompactRIO加入以下功能:

o GPS(全球定位系統)監督

o GPRS(通用封包廣播服務),供無線通信使用

o GSM(移動通信全球系統),供無線資料交換使用

o LIN(區域性連接網路)通信

o ARINC-429和MIL-1553航空協定,供飛行間測試

o 客制直流傳動(power-train)模組

「LabVIEW和可重設組態I/O FPGA技術使我們得以迅速開發Gxxx行動模組。最后完成的系統所提供的可靠性,若是沒有CompactRIO技術,是不可能達成的。現在客戶可以輕松地建立遠端操作及監督的移動系統,具備無線通信、計時及全球定位功能。」

- Wolfram Koerver, CEO, S.E.A. Datentechnik GmbH

利用嵌入式FPGA以及通用的程式設計環境,工程師可以使用CompactRIO和LabVIEW來建立任何載具內測試、控制及設計應用程式。FPGA的高速及同步化功能,結合堅固的外形及廣泛的I/O模組,使CompactRIO成為載具內應用的理想平臺。

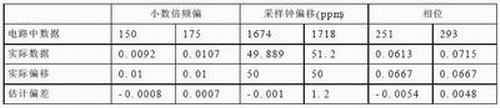

表4.1 波形圖中數據與實際數據對照表

小數倍頻率偏移和采樣鐘頻率偏移模塊是在整偏校完之后才有效,此時的小數倍頻率偏移是經過時域粗偏估計校正后的剩余部分。表4.1列出波形中的估值與實際數據的對應關系。從表中的數字對應關系可以看出,電路中估計的小數倍頻偏與實際頻偏的差在0.1%以內。采樣鐘偏移估計值與實際偏移誤差為1ppm左右,這已滿足了采樣鐘的粗調精度;相位輸出為前后符號的小數倍偏頻所引起的相位旋轉。由此單元電路,可以準確地估計出小數倍頻偏和采樣鐘偏移及其相位。

細定時同步估計的電路仿真

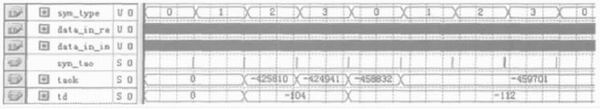

圖中的data_re_in[15..0]和data_im_in[15..0]表示經公共相位校正后的復數據實虛部;syn_in是輸入有用數據的起始位置脈沖;sym_type[1..0]是前端輸入的符號類型;taok[22..0]和td[9..0]分別為估計的符號定時偏移和其整數部分;syn_tao是taok[22..0]的有效數據起始脈沖信號。

圖4.3 符號定時偏移估計單元的電路波形圖

圖4.3中共有9個符號。由于本算法利用了4個符號的散布導頻,故圖4.3中,從第四個符號的結束處開始,在syn_tao后的taok[22..0]才是當前符號的定時偏移估計值。波形中的估值與實際數據的對應關系如表4.2所示。

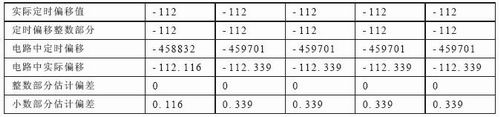

表4.2 波形圖中數據與實際數據對照表

表4.2中的定時實際偏移為-112,而不是仿真條件中的-100,這是由于在瑞利信道的仿真模型中,符號定時同步頭位置(重心位置)是在第一條徑之后12個采樣點出現的。由表中數據對應關系可知,符號定時偏移估計單元可準確地估出符號定時偏移的整數部分。由于采樣鐘偏移、算法估計誤差及電路運算誤差的影響,其小數部分不為零,這與電路的仿真結果一致。

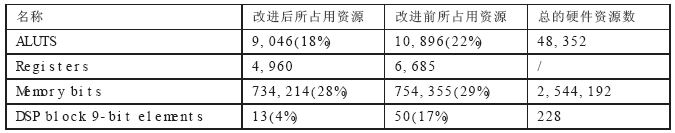

改進前后占用硬件資源比較

表4.3給出了改進前后,頻域同步所占用的硬件資源比較,其中ALUTS、Registers、Memorybits、DSPblock9-bitelements分別為自適應查找表、寄存器、存儲器和9字節DSP處理塊。通過比較可以發現,改進后的方案可以節省大量的硬件資源。

表4.3 改進前后的硬件資源對比

結束語

頻率偏移估計可以分為整數倍頻偏估計單元、小數倍頻偏、采樣鐘偏移估計單元和符號定時偏移估計單元。本文主要介紹各部分的算法方案及電路實現時所用的FPGA元件的基本結構、設計思路。最后通過對電路的仿真波形可以看出,這些頻域同步算法和FPGA電路能夠滿足多載波傳輸系統的同步要求。

]]>

關鍵詞:正交頻分復用(OFDM);正數倍頻率偏移;小數倍頻率偏移;采樣鐘頻率偏移;定時偏移

同步部分概述

正交頻分復用(OFDM)系統的一個重要問題是對頻率偏移非常敏感,很小的頻率偏移都會造成系統性能的嚴重下降。另外收發端采樣鐘不匹配,也會導致有用數據信號相位旋轉和幅度衰減,破壞了OFDM子載波間的正交性,降低系統性能。因此在OFDM系統中,頻率偏移和采樣鐘偏移估計的準確度至關重要。

OFDM接收系統的同步部分主要包括以下幾方面:頻率同步、采樣鐘同步和符號定時同步。載波頻率偏移和采樣鐘頻率偏移的存在導致了載波間干擾(ICI)和采樣點增減現象,這就需要頻率同步和采樣鐘同步。同時在解調過程中,接收機是在時域上的任意點開始接收數據的,而OFDM是基于符號的,這就需要檢測到符號的起始位置,否則會因為符號的起始位置的不合理,而導致符號間的干擾(ISI),這就是符號定時同步。

頻域同步估計方法

整數倍頻率偏移估計算法

頻率偏移△f0分成兩部分:整數倍和小數倍子載波間隔頻偏。由于在時域上已經對小數倍頻偏有一個粗略估計和校正,因此頻域內是利用內插導頻信息對整數倍頻偏和剩余小數倍頻偏進行估計校正的。

(1)

(1)

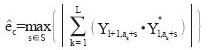

式(1)是整數倍頻率偏移估計算法表達式,它是利用連續導頻在發射端為已知固定相位的特性,使用一個長為S的滑動窗作為頻域上一個OFDM符號有效載波起始位置的估計范圍,以窗內的每一個數據作為OFDM符號有效載波的的起始位置,對前后兩個符號在假設的連續導頻位置上的復數據做相關求和,這樣就得到了S個相關值,其中最大值所對應的s即為頻域上一個OFDM符號有效載波起始位置的估計值,也即為整數倍頻偏估計值。

其中L是連續導頻個數;ak是一個符號內第k個連續導頻的序號;Yl,ak是FFT輸出的第l個符號的假設第k個連續導頻位置上的復數值;S是整數倍頻偏的估計范圍,也即為滑動窗長,s是窗口移動值,s∈S; 是S路相關和的最大值,其對應的s即為整數倍頻偏的估計值。

是S路相關和的最大值,其對應的s即為整數倍頻偏的估計值。

小數倍頻率偏移和采樣鐘頻率偏移估計算法

在OFDM系統的接收端,實際的第m個子載波的實際解調頻率為f'm=f'0+mF',這里,f'0為本地解調載波頻率,F)=F'0N,N為子載波個數,F'0為接收機壓控晶振輸出的采樣頻率。由此可以看出,在第m個子載波上,載波頻偏和采樣鐘偏移的聯合效應是大小等于△fm的子載波頻偏,這里△fm=△f0+m•△F0N,△f0=f'0-f0,△F0=F'0-F0,f0和F0分別為發射端的中心載波頻率和采用頻率。當將整偏校掉后,這里的△f0僅為小數倍的子載波間隔。

設pi為導頻點位置,pi∈P,P為導頻點位置集合;i=0,1,…,K-1,K是P的基數;△fpi為第pi個導頻點上相關結果的頻率部分,這個值以下用![]() 表示為估計結果。定義

表示為估計結果。定義![]() ,同時考慮到在第pi個子載波上的估計誤差ei,則:

,同時考慮到在第pi個子載波上的估計誤差ei,則:

![]() (2)

(2)

其中,△fpi為在第pi個導頻點上的頻率偏移和采樣鐘偏移之和,現令![]() 為所需估計的向量參數,式(2)就可以寫作:

為所需估計的向量參數,式(2)就可以寫作:

![]() (3)

(3)

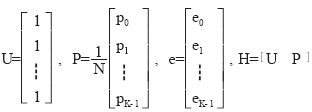

其中,

由于估計是基于![]() 的,因此將向量V稱為觀察向量,方程式(3)稱為觀察方程。線性最小平方估計就是在觀察向量給定的條件下,根據觀察方程估計向量

的,因此將向量V稱為觀察向量,方程式(3)稱為觀察方程。線性最小平方估計就是在觀察向量給定的條件下,根據觀察方程估計向量![]() 。根據最大似然估計原理,使得向量V的線性函數

。根據最大似然估計原理,使得向量V的線性函數![]() 取得最小值時,得出

取得最小值時,得出![]() 的估計值

的估計值![]() 。對式

。對式![]() 求導并使之為零,可得:

求導并使之為零,可得:

![]() (4)

(4)

公式(3)是在先得出![]() ,i=0,...,K-1的基礎上求得的,而

,i=0,...,K-1的基礎上求得的,而![]() 可以通過在導頻位置對前后兩個OFDM符號做相關運算來求。

可以通過在導頻位置對前后兩個OFDM符號做相關運算來求。

頻域符號定時偏移估計算法

時域定時的不準確就要求頻域內進一步對OFDM符號定時進行校正。由于時域內保護間隔是數據信號最后L個采樣點的完全復制,所以由FFT循環移位定理可知:符號定時的偏移所引起的子載波上相位旋轉和子載波序號k成正比。由于導頻信號插入位置已知,且其具有相位已知特性,這使得我們可以利用符號內插導頻載波間相位變化來做細符號定時同步,并與粗符號定時同步結合起來,得到一個準確的符號起始位置。

設![]() 是第j個OFDM符號定時偏移在相鄰導頻點上所引起的相位偏移之差,

是第j個OFDM符號定時偏移在相鄰導頻點上所引起的相位偏移之差,![]() 為第j個OFDM符號所估計出來的細定時。則

為第j個OFDM符號所估計出來的細定時。則![]() 和

和![]() 可表示為:

可表示為:

![]() (5)

(5)

![]() (6)

(6)

其中,L為散布導頻個數;N為一個OFDM符號中有效子載波的個數;Xj,k是第j個符號的第k個散布導頻復值;△k為兩個相鄰的子載波序號的差值。

頻域同步部分的FPGA電路實現模塊

頻域同步電路模塊各單元的工作原理如圖3.1所示。這里使用Altera公司生產的StratixⅡEP2S60的FPGA芯片來實現。

圖3.1 FFT后同步塊方框圖

FFT模塊輸出復數據經過一個OFDM符號的FIFO模塊延遲后,和當前的OFDM復數據進行相關,以實現在整數倍頻偏估計和小數倍頻率偏移算法中所需要的前后兩個符號的對應導頻相關運算,其相關結果為32位的復數據。

整數倍頻率偏移估計模塊

將相關單元輸出的復數據的實虛部符號位送到整數倍頻偏估計單元中進行整數倍頻偏估計。為了節省芯片資源,這里我們將估計整數倍頻偏的算法加以簡化,用相關后的復數據在導頻位置上的實虛部的符號位來估計整數倍頻偏值。下面的仿真的電路波形圖證明這樣實現整偏估計算法是可行的。它的輸入為相關單元輸出的復數據實虛部的符號位和此復數據的載波同步位置,輸出為整數倍頻偏估計值。

小數倍頻率偏移和采樣鐘頻率偏移模塊

首先對相關單元模塊輸出的復數據的實虛部進行歸一化,然后求歸一化單元輸出的16位復數據的相角,同時用RAM的讀地址和讀使能信號分別控制讀取存有矢量A和矢量B數據的ROM表中的數據。其中矢量A和B分別為線性最小平方估計算法中矩陣AT的第一行和第二行矢量,用此相角分別和讀出的矢量A和矢量B在一個符號內進行相乘累加,再根據保護間隔的不同,乘以相應的系數,便可分別得到小數倍頻偏和采樣鐘頻率偏移的估計值。

細定時估計模塊

考慮到定時估計范圍的問題,該模塊利用四個符號的散布導頻進行定時估計。將當前符號的散布導頻值及從RAM中讀出的前三個符號的散布導頻值按一定順序排列,并做相鄰導頻相關。將相關后的復數據的實虛部分別取絕對值累加,并將二者的累加和進行歸一化處理后進行查表,從而得出復數的相位值。這個相位即為符號定時偏移所引起的旋轉相位。再對此相位做如公式(6)的運算,這樣就得到了符號定時偏移的整數和小數部分的和,然后將其送到求整函數中,從而得到符號定時偏移的整數部分。將這個值經過并/串變換后送到前端時域同步部分,去調整FFT窗位。

電路仿真

其仿真條件為:瑞利信道,SNR為15dB,載波頻偏設為-14.9倍子載波間隔(即整數倍頻偏值為-15,小數倍頻偏值為0.1倍子載波間隔),采樣鐘偏移為50ppm,保護間隔長為512,定時符號偏移為-100個采樣點。此電路工作頻率為10MHz。輸入的16位復數據由MATLAB仿真程序產生的。

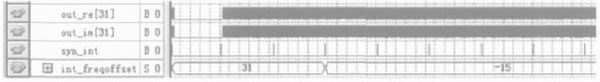

整數倍頻率偏移電路仿真

由于電路波形中無法表示小數,因此將各小數進行“擴展”,其表示皆為二進制數據,以下同。在圖4.1中,out_re[31]和out_im[31]分別是前后兩個OFDM符號中對應子載波相關結果的實虛部的符號位,int_freqoffset[5..0]和syn_int分別是整數倍頻偏估值和其有效起始位置脈沖。

圖4.1 整數倍頻偏估計部分的電路仿真波形圖

由于整數倍頻偏在每一符號的結束處才能估計出來,所以syn_int在每一個符號的結束處出現,其后即為當前符號的整數倍頻偏值。由于本算法利用了4個符號的連續導頻,故圖4.1中,從第四個syn_int后的int_freqoffset[5..0]才是當前符號的整數倍頻偏估計值。由仿真波形可看出,估出的整數倍頻偏與仿真數據中所假設的一致。故用此算法的簡化形式可以準確地估計出整數倍頻偏值。

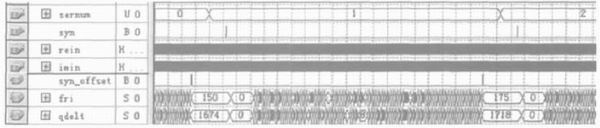

小數倍頻率偏移及采樣鐘頻率偏移估計的電路仿真

sernum[1..0]表示前級輸入的符號類型;syn為輸入復數據中的有用數據起始脈沖;rein[15..0]和imin[15..0]分別為FIFO模塊輸出復數據的實虛部;syn_offset為小數倍頻偏和采樣鐘偏移估計結果的起始位置;fri[14..0]和qdelt[14..0]為小數倍頻偏估計值和采樣鐘偏移估計值,它們由1位符號位和14位小數位組成。這里的小數位數是根據其估計范圍和估計精度要求來確定的。

在圖4.2中,小數倍頻率偏移和采樣鐘頻率偏移估計模塊使用連續導頻進行估計。在每個符號末,syn_offset高電平有效時,fri[14..0]和qdelt[14..0]才是當前符號的小數倍頻率偏移和采樣鐘頻率偏移估計值。波形中的估值與實際數據的對應關系如表4.1所示。

圖4.2 小數倍頻偏和采樣鐘偏移估計單元的電路仿真波形圖

Microsemi收購Actel與模擬企業產生協同效應

優勢:兩者的整合除了能加強在軍工、航天領域的優勢外,還將共同拓展工控、消費電子、汽車等市場,旨在改變兩者在不同行業的不利競爭局面。

待觀察方面:被收購后,Actel的反熔絲產品和SmartFusion肯定還是重點,而一些不賺錢、低利潤的產品線將可能被收縮。

今年10月,FPGA行業排名第四的Actel公司被在軍工半導體和高性能模擬/混合信號半導體領域表現突出的Microsemi公司以4.3億美元左右的價格收購了,這是近年來發生在FPGA行業唯一的一次并購案。近些年,Actel雖然創新步伐很快,但發展速度不能領先于競爭對手,這在寡頭壟斷的FPGA市場是非常不利的。綜合看來,這次整合將產生兩大協同效應:

一方面,將加強軍工、航天領域業務。Microsemi是一家在軍工、航天和高可靠性醫療等非常專業的領域中較為出名的公司,主要產品包括針對上述專業領域的保護器件、電源管理、RF/微波傳輸和功率調節器產品。Actel公司的反熔絲FPGA因具有抗輻射、穩定性好等特點,是航空航天領域的第一大FPGA企業,它在該領域占有80%的市場。據稱兩者在軍工和航天領域的客戶有80%的重疊率,而且今年Microsemi還收購了Arxan Defense Systems軟件公司、VT Silicon和White Electronic公司,這些企業的業務都集中在軍工領域,整合將加強其在這一領域的優勢。

另一方面,Microsemi產品還包括在民用領域的一些模擬/混合信號產品,如針對汽車GPS顯示屏、筆記本、LCD電視、監視器、機頂盒市場的高性能模擬/混合信號產品,其中包括背光驅動、功率管理等產品與Actel的可編程SoC(PSoC)產品目標市場相互契合,兩者可以形成更完整的方案,去拓展工控、消費電子、醫療等多個領域。其中,Actel的可編程SoC和其他FPGA接口可以作為方案中的主控部分或“黏合”部分。

Actel在FPGA行業走了一條差異化道路,其最早的FPGA產品主要針對軍工、航天領域。1999年,它進軍基于Flash的FPGA領域,而其他FPGA企業的產品則基于SRAM。Flash FPGA在功耗、安全性、可靠性和成本上更具一定優勢,其Flash FPGA包括ProASIC、IGLOO、Fusion和SmartFusion系列產品。其中,值得關注的是SmartFusion產品,這是FPGA業內獨有的集成了FPGA、ARM硬核和可編程模擬電路的可編程SoC(PSoC)產品,目標市場是工業應用如馬達控制等,預計這個產品是與Microsemi模擬技術重點融合的產品。Microsemi在半導體業的名氣并不算大,年銷售額僅為四五億美元。雖然Microsemi在全球有約1600名員工,但在中國沒有投入太多力量,因此合并后,其在中國的業務最有可能仍來自Actel。

兩者的結合體現了在高度壟斷的FPGA行業中,與模擬資源結合也不失為一條新出路。

Altera與ARM、MIPS、英特爾合作市場接受度不一

優勢:提供了業界最廣泛的嵌入式處理器選擇,并將提供統一的集成環境。

待觀察方面:ARM+FPGA的接受度將取決于該系列產品的成本,MIPS32在中國市場的接受度可能較低,英特爾Atom E600將在工控領域有較好的發展。

Altera近日發布了其嵌入式計劃,進一步展示了FPGA與微控制器行業緊密融合的趨勢。該計劃稱,到2010年第四季度末,Altera將向業界提供Qsys系統集成工具,客戶能夠將多種嵌入式CPU和FPGA進行系統級集成,這些嵌入式CPU包括Altera NiosII軟核、ARM Cortex-M1軟核、MIPS32軟核、ARM Cortex-A9硬核。Qsys系統集成工具是Altera Quartus II開發軟件的一部分。

具體來說,Altera將在2011年下半年推出的28nm FPGA的一個系列中集成ARM Cortex-A9 MPCore硬核,并會在2011年上半年推出MIPS32處理器架構的MP32軟核處理器。此前Altera已提供Nios處理器,并對飛思卡爾ColdFire軟核、ARM Cortex-M1軟核進行支持。同時,英特爾在2010秋季IDF上發布的凌動E600處理器封裝中集成了Altera的FPGA。

此次新發布嵌入式處理器的市場接受度不一,其中針對ARM Cortex-A9 MPCore硬核,中國客戶表現出極大的興趣。因為目前市場上ARM+FPGA的應用較多,而且懂得ARM應用的客戶比FPGA的客戶要多,ARM具備成熟開發環境,有大量現成的可移植代碼。如果新產品成本控制得好,例如比單片FPGA加ARM要便宜,會對FPGA市場帶來一定的沖擊。其應用將主要是通信、工業和汽車領域。

針對MP32,中國客戶的接受度會非常低。因為MP32與NiosII軟核性能差不多,但比NiosII占有的邏輯資源更多,而且授權費高達3萬美元,因此中國客戶選用的可能性較小。Altera推出此內核可能主要是為了配合一些國外客戶采用此內核來支持一些操作系統。

針對在同一封裝中集成了處理器和FPGA的英特爾Atom E600,它的主要應用是工控領域,將替代傳統X86,應該有較好的前景。

Altera推出嵌入式計劃的背景是認為有三大發展趨勢正在推動CPU+FPGA的應用:一是系統處理并行化趨勢。在并行化的兩類技術中,硬件協處理器效果最好,另一個是多核技術,但是沒有任何方式能夠提前知道哪些軟件功能需要通過硬加速的方式來實現,所以FPGA是最理想的加速器實現方案,因為它是現場可編程的。二是在很多當今的嵌入式應用中,FPGA與CPU已經進行了更高級別的集成,獲得了成本的削減。三是業界很多芯片廠商已經在采用處理器+FPGA的方式。而FPGA作為協處理器,要達到最理想的性能和效率就需要與CPU之間做緊密的耦合來減少延遲。所以,CPU+FPGA這一技術需要更緊密的結合方式。

一般在使用DS18B20通信時需

|

|

利用FPGA實現與DS18B20通信不存在被迫關閉中斷的情況,可以滿足對實時性要求嚴格的應用要求。

2 ProASICplus系列FPGA簡介

ProASICplus系列FPGA是ACTEL公司推出的基于Flash開關編程技術的現場可編程門陣列,包括從7.5萬門的APA075型到100萬門的APAl000型,具有高密度、低功耗、非易失、含有嵌入式RAM及可重復編程等特點。

因為ProASICplus系列FPGA基于Flash技術,利用Flash開關保存內部邏輯,因此不需要另外的器件。由于不需要上電配置過程,因此具備上電就立即工作的特點。不用配置器件,系統的保密性提高。

筆者在電力監控的產品中利用APA150在整個系統中充當協處理器,使主CPU從繁重的實時處理中解脫出來。

3 DS18B20簡介

3.1內部結構

DS18B20的64位序列號均不相同。

8位CRC生成器可以完成通信時的校驗。

暫存寄存器有9個字節,包含溫度測量結果、溫度報警寄存器、CRC校驗碼等內容。

3.2操作步驟

對DS18B20功能命令。

3.2.1初始化

FPGA要與DS18B20返回響應脈沖。

3.2.2ROM命令

該步驟完成FPGA與總線上的某一具體DS18B20建立聯系。ROM命令有搜尋ROM(SEARCH ROM)、讀ROM(READ ROM)、匹配ROM(MATCH ROM)、忽略ROM(SKIP ROM)、報警查找等命令(ALARM SEARCH)。

這里,FPGA只連接1個DS18B20的48位ID號。

3.2.3 DS18B20功能命令

FPGA在該步驟中完成溫度轉換(CONVERTT)、寫暫存寄存器(WRITE SCRATCHPAD)、讀暫存寄存器(READ SCRATCHPAD)、拷貝暫存寄存器(COPYSCRATCHPAD)、裝載暫存器寄存器(RECALL E2)、讀供電模式命令(READ POWER SUPPLY)。

文中不用溫度報警功能,因此在本步驟中只需完成溫度轉換,然后通過讀暫存寄存器命令完成溫度轉化的結果。

3.3操作時序

2所示。從時序圖中可以看出,對DS18B20的操作時序要求比較嚴格。利用FPGA可以實現這些操作時序。

4 FPGA與DS18B20的通信

4.1 DS18B20的操作模塊

FPGA需要完成DS18B20溫度轉換、讀取溫度轉化結果。讀

取48位ID號和讀取溫度轉換結果過程中,FPGA還要實現CRC校驗碼的計算,保證通信數據的可靠性。

以上操作反復進行,可以用狀態機來實現。狀態機的各種狀態如下:

RESET1:對DS18B20進行第三次復位。

CMDCC2:

|

|

設計中采用Verilog語言建立DS18B20 PROC(sysclk,reset,dq_pim,id,temp_data,dq_ctl)。

從仿真波形可以看出,系統上電后的10ms左右,FPGA可以讀出DS18B20的48位ID值,這樣,主CPU在系統復位后很短的時間內就可以讀取ID值,進行相應的處理。

4.2 FPGA與CPU的接口

在FPGA中,要實現對DS18B20_PROC模塊的調用及建立與CPU之間的接口。

與CPU之間的接口通過建立若干寄存器實現。溫度測量值和48位ID可以用4個16位寄存器保存。CPU通過讀取這些寄存器可以獲得溫度測量數值和48位ID值。

CPU、FPGA及DS18B20的連接原理如圖4所示。

5 結束語

在系統中,FPGA可以分擔許多主處理器的工作,提高整體實時性,降低CPU處理的嚴格實時約束,從而降低CPU軟件處理的難度。同時,由于ACTEL公司的ProASICplus系列FPGA的保密特性,可以增強產品知識產權的保護。

本設計應用在電力監控產品中。測量出的裝置內部溫度用于電量測量精度補償和報警,對保證產品測量精度和可靠運行具有重要意義。48位ID值用于產品的惟一編碼標識和以太網MAC地址,便于產品生產、維護和管理

概覽

高端設計工具為少有甚是沒有硬件設計技術的工程師和科學家提供現場可編程門陣列(FPGA)。無論你使用圖形化設計程序,ANSI C語言還是VHDL語言,如此復雜的合成工藝會不禁讓人去想FPGA真實的運作情況。在這個芯片中的程序在這些可設置硅片間到底是如何工作的。本書會使非數字化設計人員明白FPGA(現場可編程門陣列)的基礎知識及其工作原理。此信息在使用高端設計工具時同樣十分有用,希望可以為理解這一特別技術提供一些線索。

FPGA-現場可編程門陣列

每一塊FPGA芯片都是由有限多個帶有可編程連接的預定義源組成來實現一種可重構數字電路。

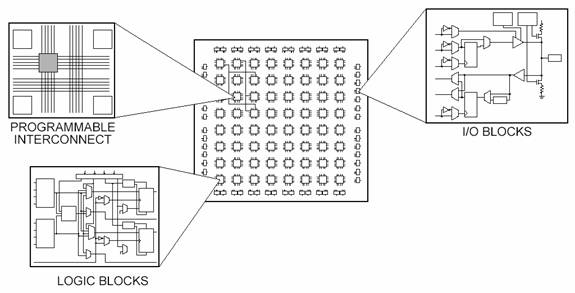

圖1.FPGA不同構成

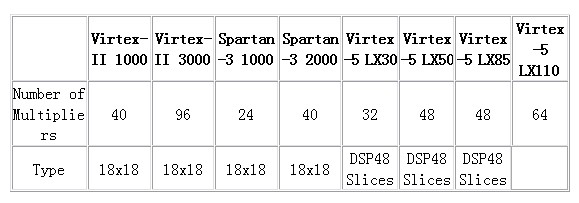

FPGA芯片說明書中,包含了可編程邏輯模塊的數量、固定功能邏輯模塊(如乘法器)的數目及存儲器資源(如嵌入式RAM)的大小。FPGA芯片中還有很多其它的部分,但是以上指標通常是為特定應用選擇和比較FPGA時,最重要的參考指標。

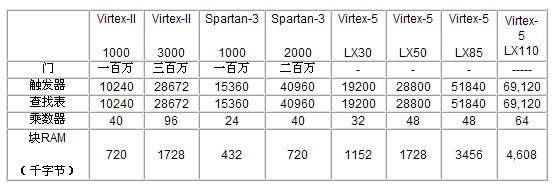

在最底層,可配置邏輯模塊(如片或邏輯單元)有著兩種最基本的部件:觸發器和查找表(LUT)。這很重要,因為各種FPGA家族之所以各不相同,就是因為觸發器和查找表組合的方式不同。例如,Virtex-II 系列的FPGA ,它的片具有兩個查找表和兩個觸發器,而Virtex-5 FPGA的片具有4個查找表和4個觸發器。查找表本身的結構也可能各不相同(4輸入或6輸入)。關于查找表工作原理的更多信息將在后面的章節中給出。

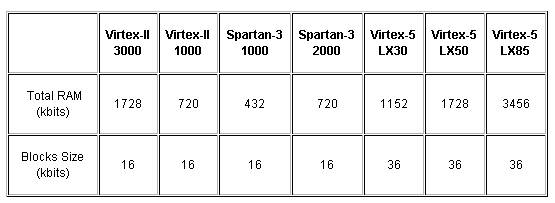

表1中列出了在NI LabVIEW FPGA硬件目標中使用的FPGA的指標。邏輯門的數量是一種將FPGA芯片與ASIC技術進行比較的傳統方法,但是它并不能真實地表述FPGA內部的獨立單元的數量。這就是Xilinx公司沒有在新型Virtex-5系列中指定邏輯門數量的原因之一。

表1.不同系列FPGA源規格

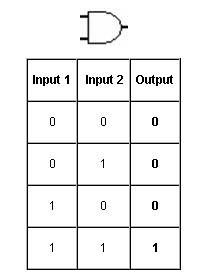

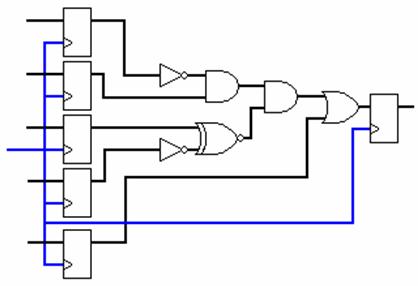

為了更好地理解這些規格的意義,將編碼考慮為合成的數字電路模式。對任何一段合成代碼,或圖形化或文本形式,都有相應的電路圖反映邏輯組件該如何連線。通過一段簡單布爾邏輯電路了解下相應的示意圖。圖2表示的是傳遞5個布爾信號并且可圖形化計算所得的二進制值的功能組。

圖2.載入5個信號的簡單布爾邏輯

在通常情況下(LabVIEW SCTL—單周期定時環路外),圖2所示相應電路圖同圖3所示相近。

圖3.為圖2中布爾邏輯的相應電路圖

雖然很難明白,但是實際上這里創建了兩個并行分支的電路。最上面的5條黑線被反饋到第一個分支,它在每個布爾操作間添加了觸發器。最下面的5條黑線構成了第二個邏輯鏈。其中一支路在每步操作之間增加了同步寄存器,另一條邏輯鏈是確保執行數據流的。本電路圖正常工作時總共需要12個觸發器和12個查找表。上端分支和每個元件將在以后章節分析。

觸發器

圖4.觸發器符號

觸發器是二進制移位寄存器,用于同步邏輯以及保存時鐘(脈沖)周期內的邏輯狀態。在每個時間(脈沖)邊沿,觸發器在輸入時鎖定1(真)或0(假)值并且保存此值直到下次時鐘(脈沖)邊沿。在正常情況下,LabVIEW FPGA在每次操作之間都設置一個觸發器,以保證有足夠的時間來執行每步操作。對此律的例外只發生在SCTL結構中寫代碼的情況。在這個特殊的環路結構中,觸發器只放置在閉環迭代的始末段,并且由編程者考慮定時因素來決定如何放置。對SCTL內代碼如何同步的更多內容將在以后章節中討論。圖5表示的是圖3的上端分支,觸發器由紅色高亮表示。

圖5.繪制由紅色高亮表示出觸發器的電路圖

查找表

圖6.雙四輸入查找表

圖6所示示意圖中的其他邏輯電路通過使用少量查找表形式的隨機存取存儲器實現。我們可以簡單地假定FPGA中系統門的數量可參考與非門(NAND)以及或非門(NOR)的數量,但實際上,所有的組合邏輯(與門、或門、與非門、異或門等)都是通過查找表存儲器中的真值表來實現。真值表是輸出對應于每個輸入值組合的預定義表(現在卡諾圖的重要性在你的頭腦中可能會慢慢淡化)。以下是對數字邏輯電路課程的快速回顧:比如,圖7是布爾邏輯與門操作過程。

這是對數字邏輯課程的快速回顧:

例如,圖7中顯示了布爾型AND操作。

圖7.布爾型AND操作

表2.布爾與門操作的真值表

你可以認為輸入值是所有輸出值的數字索引,如表3所示。

表3.布爾與門擦操作的真值查找表實現

Virtex-II和Spartan-3系列FPGA芯片有著4輸入查找表來實現真正的4輸入信號的16種組合。圖8就是一個四輸入電路實現的例子。

圖8.輸入布爾邏輯的四信號電路

表4所示為使用雙四輸入查找表實現的相應的真值表。

表4.圖8中所示相應真值表

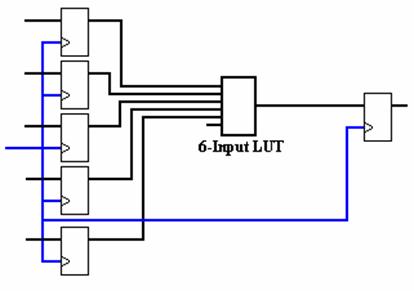

Virtex-5系列的FPGA使用雙六輸入查找表,可以通過6個不同輸入信號的64種組合來實現真值表。因為觸發器之間的組合邏輯十分復雜,所以在LabVIEW FPGA中使用SCTL也越來越重要。下一節將講述SCTL如何優化利用LabVIEW中的FPGA源。

SCTL

上幾節中使用的代碼例子假定代碼是設置在SCTL外部,并為保證執行同步數據量也同步了附加電路。SCTL是LabVIEW FPGA中一個特殊結構,生成一個更為優化的電路圖,以期望達到在一個時鐘(脈沖)周期內執行完所有邏輯電路分支。例如,若設置SCTL在40MHZ運行,則所有邏輯電路分支將在25ns內執行完畢。

如果在SCTL中設置前例中同樣的布爾邏輯電路(如圖9所示),則生成如圖10所示的相應電路示意圖。

圖9.附有STCL的簡單布爾邏輯

圖10.圖9所示布爾邏輯相應的電路圖

很明顯,這種實現方法簡單多了。在Virtex-II或Spartan-3系列FPGA中,觸發器間的邏輯需要至少2個4輸入查找表,如圖11所示。

圖11.圖10中電路圖的雙四輸入查找表實現

由于Virtex-5系列FPGA有著6輸入的查找表,用戶可以在一個查找表中實現相同數量的邏輯,如圖12所示。

圖12.圖10中雙六輸入查找表實

本例中使用的SCTL(如圖9所示)設置在40MHZ下運行,這意味著在任意觸發器之間邏輯電路必須在25ns內完成執行。電子在電路中傳播的速度決定了代碼執行的最大速度。關鍵路線是有最長傳播延遲的邏輯電路分支,它決定了該部分電路中理論最大時鐘速率。Virtex-5 FPGA上的雙六輸入查找表不僅減少實現給定邏輯電路所需要的查找表總數,而且減少電子通過邏輯電路的傳播延遲(時間)。Virtex-5系列FPGA中的6輸入查找表不僅可以減少實現特定邏輯而需要的查找表的數量,而且可以降低邏輯中電流的傳輸延時。這意味著,您可簡單地通過選擇一個基于Virtex-5的硬件指標設置相同的SCTL,追求更快的時間速度。

請查看下方白皮書的對策列表,獲取更多Virtex-5 FPGA相關信息。

乘數器和DSP片

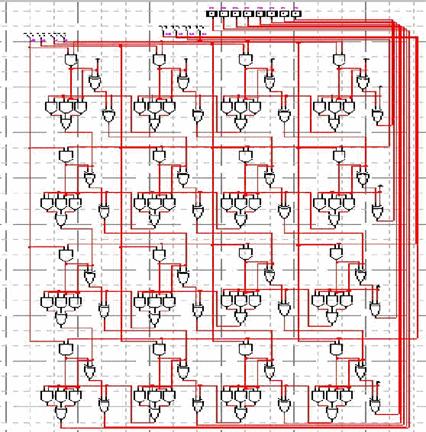

看起來簡單的兩數相乘運算在數字電路中實現起來是十分復雜的,也是極為消耗資源的。為提供相關參考,圖14所示是一種使用組合邏輯電路實現4×4字節乘數器的示意圖。

圖14.兩個4字節輸入相乘的電路圖

試想兩個32字節的數字相乘要通過2000多步操作才能得到結果。因此,FPGA預設了乘數器電路,在數學和信號處理應用中保存對查找表和觸發器使用。Virtex-II和Spartan-3 FPGA擁有18×18bit乘法器,所以兩個32字節數字相乘的運算需要三個乘法器來實現。許多信號處理算法都包括連乘運算結果的功能,因此Virtex-5等高性能FPGA都預設被稱為DSP片的乘數器累加電路.這些預設處理組件,也被稱為DSP48片,包括25×18bit乘數器以及加法器電路,盡管您可單獨使用乘數器功能。表5所示為不同FPGA系列DSP決策。

表5.不同FPGA的DSP源

塊隨機存取存儲器(RAM)

選擇FPGA時,記憶源是另一個需要考慮的關鍵因素。嵌入FPGA芯片中的用戶自定義隨機存取存儲器(RAM),對儲存數據設置或平行環路之間傳送數值很有幫助。基于FPGA系列,您可在16或36kb組件中設置板載RAM,或者使用觸發器以數組來執行數據設置;然而,對于FPGA邏輯源來說,大型數組很快就變得十分“奢侈”。由100個32字節元素數組可消耗Virtex-II 1000 FPGA中超過30%的觸發器,或者占用少于1%的嵌入式塊RAM.DSP算法通常需要追蹤整個數據塊或是復雜等式的系數,而在沒有板載存儲器情況下,許多處理功能在FPGA芯片的硬件邏輯電路中都不適用。圖16所示為使用塊RAM讀寫存儲器的圖形化功能。

同樣,你也可以使用內存塊,將一段完整周期存儲為數值和索引的順序表,為板載信號發生器存儲周期性波形數據。輸出信號的最終頻率由檢索數值的速度決定,這樣您就可用此方法動態改變輸出頻率,而不需要輸入波形中的急劇變化。

圖16.用于先進先出緩沖器的塊RAM功能

FPGA固有的并行執行要求邏輯電路獨立元件可在不用時間脈沖下驅動。在不同運行速度下的邏輯電路之間傳遞數據是很棘手的。使用先進先出(FIFO)緩沖器時,板載存儲器可用來是傳輸更加平穩。如圖16所示,用戶可以將FIFO緩沖器配置成不同大小以確保數據在FPGA芯片的非同步部件間不會丟失。表6所示為嵌入不同FPGA系列的用戶可設置快RAM。

表6.不同FPGA的記憶源

總結

隨著高端技術的發展以及新概念的深入概括,FPGA技術地采用將不斷增加。然而探究FPGA其中奧秘,感嘆這硅片中在方框圖間匯編出的變化,也是十分重要的。在發展階段,如果您懂得如何利用和優化資源,比較和選擇觸發器、查找表、乘數器和塊RAM等硬件指標是十分有幫助的。這些基本的功能塊并不是包含所有資源的完整清單,而且這篇白皮書并沒有包含對所有FPGA部件的討論。用戶可以通過下面的推薦資源,繼續學習關于FPGA和數字硬件設計的知識。

FPGA的優勢還在于,可以利用裕量連接帶寬來靈活構建直達各邏輯塊的數據通道和存儲器訪問通路。圖1所示的可編程互連結構提供了大量的布線帶寬。模塊與電路板可根據FPGA輸出帶寬、存儲器大小及延遲的需要進行設計,I/O端口可由用戶自定義。

圖1 FPGA的架構

最后,FPGA架構還擁有一個優勢,它可擴展為更大型的邏輯塊、存儲器塊與DSP塊的陣列。邏輯與主緩存的大小是一起擴展的。現有最大的FPGA峰值功耗為30W,其FPGA架構有很多空間,可以在不超過現有數據中心功率和冷卻限制的前提下,擴展為新的處理構型。

盡管FPGA架構具有許多出眾的性能,一些性能必須共同發揮作用,才能提供優于CPU協處理的解決方案。

芯片與算法基礎

大部分雙精度浮點算法的加法與乘法操作比例大約為1:1。在FPGA中,加法運算使用邏輯資源,乘法運算使用DSP塊,因此FPGA的邏輯資源與DSP塊的比例必須均衡。FPGA的另一個特點是其可編程功率技術,該技術可針對所有邏輯塊、DSP塊與存儲器塊進行編程,根據設計的時序要求將其設定為高功耗或低功耗模式。

浮點運算核已經改進,可運行于更高的時鐘速率,使用更少的DSP塊和更少的邏輯資源。采用浮點編譯器可減少不同浮點運算核之間用于連接64位數據通路的邏輯資源。

在一次浮點運算結束時,合并對浮點運算進行規格化處理(定點格式轉換至浮點格式)的步驟,可以顯著減少對后續浮點運算輸入的去規格化處理(浮點格式轉換為定點格式)。浮點運算的數學表達式的整個數據通路可熔接在一起,這會最多減少40%的邏輯資源并使時鐘速率略有提高。

浮點運算的正確組合十分重要。如果算法有許多超越運算(求指數、求對數等),FPGA可配置所需要的數目。在GPGPU設計中,會增加一些硬模塊實現上述函數,但比例比單精度浮點邏輯少得多。使用算法技巧、抽象硬件細節及針對個別FPGA資源的優化都需要函數庫。

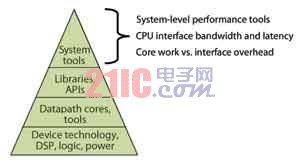

基于芯片、算法與庫基礎,圖2的系統級解決方案涉及到了工具鏈、模塊/板級設計、CPU接口以及采用合作公司專門技術的由CPU至基于FPGA的加速器的數據傳輸。

圖2 FPGA加速系統級解決方案的基礎

FPGA(Field Programmable Gate Array),是PAL、GAL、PLD等可編程器件進一步發展產物,其邏輯功能由內部規則排列邏輯單元陣列完成。邏輯單元陣列內部包括可配置邏輯模塊、輸入輸出模塊和內部連線(Interconnect)三個部分。工程師可軟件編程實現FPGA內部邏輯模塊和I/O模塊重新配置,以實現自定義邏輯。

FPGA技術有很多優勢,包括自定義I/O硬件定時和同步、高度可靠性、數字信號處理和分析等。這些優勢為快速增長汽車電子測試技術提供了靈活低成本解決方案。基于FPGA技術汽車電子應用主要包括車載數據采集和對電子控制單元(ECU)硬件環(HIL)仿真。

1) 車載數據采集

車載數據采集系統(IVDAS)作為最常見汽車電子測試應用之一,主要用于記錄和分析汽車內多種傳感器信號,同時對測試系統可靠性、便攜性和開發性等具有較高要求。車載應用涉及技術指標包括采樣率、信號調理、處理和分析等。例如,采樣率范圍從GPS數據記錄15Hz到碰撞試驗200kHz不等,FPGA可以直接連接到數字和模擬I/O,并可對各通道定義不同采樣率和觸發。,基于FPGA技術系統可以同時解決這些車載測試應用,避免定制硬件或多個測試系統需要。即單個FPGA平臺既可用于低速、高精度GPS或溫度記錄;又可快速編程實現用于有高采樣率要求碰撞試驗;也可將不同采樣率以并行方式共存于同一個測量應用中,比如,配置FPGA實現10Hz溫度采集同時進行50kHz振動測試;并可實現任何I/O之間同步,比如,實現CAN總線數據和數字或模擬I/O信號間納秒級同步測量。沒有FPGA技術,則很難實現單個系統同時滿足這些不同車載數據采集需求。

應用FPGA技術,還可對任何傳感器信號進行高級信號處理和分析。很多信號處理系統中,底層信號預處理算法要處理大量數據,對處理速度要求很高,但算法相對簡單,便可用FPGA進行編程實現。此外,可很方便FPGA上實現對所采集信號作數字濾波運算、快速傅立葉變換(FFT)、加窗等多種信號處理和分析。傳感器級信號處理和分析功能將使FPGA技術更適合于車載數據采集應用。

2) ECU硬件環仿真

硬件環仿真作為設計流程中重要組成部分,是對虛擬運行環境中設備進行非常逼真實際I/O模擬。其最顯著優點是可以對實際情況進行模擬,而不會產生實際危險。您可以真實世界中不能實現極端條件下對控制裝置進行測試-理論上汽車可以達到最高行駛速度下進行測試。功能強大高逼真度硬件環實時仿真縮短開發周期加快了產品上市時間,還測試期間無需使用實際硬件而降低了設備成本以及相關維護成本。ECU是用于汽車發動機和傳動系控制電子裝置,它接收傳動速度、曲軸和凸輪軸速度以及油門位置等信號,對此信息進行處理后,以產生用于控制發動機信號和傳動系參數。作為汽車最核心部件之一,ECU設計中任何一個微小差錯都會導致車毀人亡。這使硬件環仿真成最終運用之前對ECU進行測試標準方法。

一個典型硬件環系統(見圖1)包括用于引擎模型仿真控制器,該控制器運行實時環境下并仿真引擎上各種動態特性;I/O模塊用來接收ECU輸出信號并將引擎仿真后信號反饋給ECU,使用FPGA技術可以創建自定義I/O來滿足仿真條件下對各種信號需求,例如用于爆震、火花、發動機位置傳感器,燃油噴射器以及歧管壓力同步信號,和開關、溫度、腳踏板、油門和汽車行駛速度等異步信號;此外還包括測試數據記錄和測試步驟等。構成一個完整系統,還需要一臺主機運行操作界面,并配合相應測試管理軟件和后續數據分析軟件。

硬件環測試往往要求系統極高速度下運行,多個輸入/輸出設備之間精確定時和同步就顯極為重要。例如,您可以FPGAI/O向控制器輸出一個可變磁阻傳感器信號,并確保控制器適當時間和正確電流下打開和關閉燃油噴射器。與傳統定制系統相比,基于FPGA技術系統實現精確且同步波形生成和獲取方面具有明顯優點,它可以實現多個I/O高速下進行同步,并快速完成信號數據與輸入/輸出信息間轉換。

實現對ECU硬件環仿真,FPGA還可應用于對ECU快速原型設計中,從硬件層面驗證控制算法和模型效果,同時FPGA并行性允許將多個快速控制循環集成同一個系統中。例如,Drivven公司應用FPGA可重復配置性能,實現了對Yamaha YZF-R6發動機控制系統原型設計,而避免了設計過程中購買多個定制硬件需要,降低了成本。

圖形化FPGA編程

FPGA技術有很多優點,比如可自定義邏輯、高可靠性等,可廣泛應用于車載測試和ECU設計流程中。但工程師對FPGA進行編程時,往往需要掌握硬件設計語言如VHDL之類知識。而圖形化開發工具,比如National Instruments (NI)高效圖形化開發環境LabVIEW,則是專為需要建立靈活可擴展性測試測量和控制應用系統工程師和科學家設計,以滿足他們以最小成本、最快速度開發系統需求。

LabVIEW直觀圖形化開發特性,可使工程師把更多精力集中功能開發上,而代碼撰寫上,進而大幅縮短開發時間和成本。LabVIEW又是一個開放性軟件平臺,一些特定應用,提供多種工具包和模塊來提升和加速系統開發。比如,LabVIEW FPGA模塊,工程師就無須硬件描述語言和硬件設計相關專業知識,便可WINDOWS操作系統上,圖形化開發自定義FPGA邏輯代碼并下載到FPGA硬件目標,來實現創建自定義硬件。如圖2所示,使用LabVIEW FPGA實現CAN數據和數字或模擬信號間納秒級同步測量。當測試要求改變時,可下載新代碼到FPGA,而無需新定制硬件。同時,提供VHDL語言接口,為方便工程師直接使用現成VHDL代碼。LabVIEW Real-Time模塊則用于針對實時硬件目標開發時間確定性應用程序。此外,LabVIEW附加仿真接口工具包實現了LabVIEW和MathWorks Simulink(r) 軟件(運用該軟件您可以將您算法模型從Simulink(r)導入LabVIEW中)之間無縫連接。總之,圖形化開發軟件LabVIEW將極大提高工程師工作效率。

使用LabVIEW FPGA軟件和可重復配置硬件技術,可創建高性能控制和采集系統。下面舉兩個例子,有關基于FPGA技術硬件平臺汽車電子中應用。

用戶解決方案1:便攜式車載數據采集系統

車載數據采集信號類型包括溫度信號(熱電偶、RTD)、聲音和振動信號(帶IEPE激勵加速度傳感器或麥克風)、壓力和載荷信號(應變計或稱重傳感器)、位置信號(LVDT或線性電位計)、速度信號(編碼器)、控制總線信號(CAN,J1350,ODBII),以及視頻信號等。這些信號都是用于汽車性能評價。

德國Goepel Electronic公司面臨上述信號類型、環境條件復雜、有大量數據存儲要求,用于車載測試分析和線診斷便攜式測試設備時,選擇了NI CompactRIO嵌入式控制系統,LabVIEW FPGA模塊和LabVIEW Real-Time模塊。很短時間內開發了CARLOS (in-car logging system),加上CompactRIO平臺低成本解決方案,大大節省了預算。

CompactRIO硬件平臺(見圖3)是一個基于FPGA技術嵌入式系統。FPGA芯片是CompactRIO體系結構核心,直接和相應車載模塊相連。車載模塊可直接和車用傳感器、執行器和網絡相聯,并提供信號調理、隔離和汽車總線。該平臺包含一個嵌入式實時處理器,可用于獨立工作、確定性控制、車載數據記錄和分析等。CompactRIO具有小型、堅固機械封裝、可承受50g沖擊和-40℃到70℃工作溫度范圍等特點,提供雙電壓輸入(9-35V),可直接從車上電池取電。這些都使CARLOS適用于復雜車載測試環境和有限測試空間。

該系統已成功用于實驗室、風洞和試驗場上汽車測試,可長時間記錄數據。另外,可選擇相應車載模塊和內置應用程序,實現不同測試需求。比如實現冬季或夏季試驗中發動機熱管理系統評價,只需選擇溫度等信號對應車載模塊和已開發好LabVIEW應用程序即可;同時,該程序提供報警、用LabVIEW報告生成工具包實現數據寫入EXCEL表格、或直接寫進數據庫、歷史數據查看等功能。此外,基于FPGACompcatRIO開放試架構允許用戶擴展系統或進一步開發自定義測試系統。

用戶解決方案2:用于BMW V12汽油發動機硬件環仿真

MicroNova公司基于NI LabVIEW FPGA模塊和NI PXI-7831R可重復配置I/O模塊上,開發了一種全新、靈活可編程引擎硬件環仿真系統(見圖4),該系統能夠直接對BMW 12缸概念車汽油噴射器進行仿真,這是世界上第一種能夠對這種情況進行仿真系統。

該引擎硬件環仿真系統可以與曲軸角度同步記錄所有汽油噴射時間和點火角度,并將這些數據提供給控制器作為仿真輸入。同時模擬、數字以及脈寬調制器接口采集輸入信號并輸出相應變量數據。而碰撞信號仿真則是多達六個獨立傳感器,用戶定義碰撞函數,產生基于轉速輸出信號。

NIPXI平臺為該系統提供了完整硬件模塊選擇,同時PXI高級定時和觸發特性保證了汽車信號間同步采樣達到微秒級觸發精度。而基于PXI平臺可重復配置I/O模塊更是保證了高精度、靈活采集引擎高速傳感信號。使用了LabVIEW開發FPGA,可以很方便改變相應組合邏輯,并針對不同氣缸數目各種引擎應用不同軟件配置,大大節省了開發成本、提升了性能。同時,使用了LabVIEW仿真接口工具包,可以很快速將MathWorks Simulink(r)下開發仿真模型整合到LabVIEW平臺中,節省了大量開發時間。總之,益于PXI平臺和基于FPGA可重復配置I/O組件模塊化特性和靈活性,MicroNova公司很短時間內便開發出了高性能ECU硬件環仿真系統,成功應用于BMW 12缸最新概念車型驗證。

本文小結

FPGA技術帶來了汽車電子測試技術創新,憑借開發基于FPGA硬件單個系統可以解同汽車設計和測試應用,而無需多個定制測試設備。基于LabVIEW圖形化FPGA編程則進一步縮短了開發時間。NI CompactRIO和基于PXI可重復配置I/O模塊都是基于FPGA硬件平臺,用戶可以開發適用于涉及汽車總線、不同信號類型車載測試應用,還可用于汽車ECU設計流程中快速原型驗證和硬件環仿真測試

ARM架構是面向低預算市場設計的第一款RISC微處理器,基本是32位單片機的行業標準,它提供一系列內核、體系擴展、微處理器和系統芯片方案,四個功能模塊可供生產廠商根據不同用戶的要求來配置生產。由于所有產品均采用一個通用的軟件體系,所以相同的軟件可在所有產品中運行。目前ARM在手持設備市場占有90以上的份額,可以有效地縮短應用程序開發與測試的時間,也降低了研發費用。

|

DSP(digital singnal processor)是一種獨特的微處理器,有自己的完整指令系統,是以數字信號來處理大量信息的器件。一個數字信號處理器在一塊不大的芯片內包括有控制單元、運算單元、各種寄存器以及一定數量的存儲單元等等,在其外圍還可以連接若干存儲器,并可以與一定數量的外部設備互相通信,有軟、硬件的全面功能,本身就是一個微型計算機。DSP采用的是哈佛設計,即數據總線和地址總線分開,使程序和數據分別存儲在兩個分開的空間,允許取指令和執行指令完全重疊。也就是說在執行上一條指令的同時就可取出下一條指令,并進行譯碼,這大大的提高了微處理器的速度。另外還允許在程序空間和數據空間之間進行傳輸,因為增加了器件的靈活性。其工作原理是接收模擬信號,轉換為0或1的數字信號,再對數字信號進行修改、刪除、強化,并在其他系統芯片中把數字數據解譯回模擬數據或實際環境格式。它不僅具有可編程性,而且其實時運行速度可達每秒數以千萬條復雜指令程序,遠遠超過通用微處理器,是數字化電子世界中日益重要的電腦芯片。它的強大數據處理能力和高運行速度,是最值得稱道的兩大特色。由于它運算能力很強,速度很快,體積很小,而且采用軟件編程具有高度的靈活性,因此為從事各種復雜的應用提供了一條有效途徑。根據數字信號處理的要求,DSP芯片一般具有如下主要特點:

(1)在一個指令周期內可完成一次乘法和一次加法;

(2)程序和數據空間分開,可以同時訪問指令和數據;

(3)片內具有快速RAM,通常可通過獨立的數據總線在兩塊中同時訪問;

(4)具有低開銷或無開銷循環及跳轉的硬件支持;

(5)快速的中斷處理和硬件I/O支持;

(6)具有在單周期內操作的多個硬件地址產生器;

(7)可以并行執行多個操作;

(8)支持流水線操作,使取指、譯碼和執行等操作可以重疊執行。

當然,與通用微處理器相比,DSP芯片的其他通用功能相對較弱些。

FPGA是英文Field Programmable Gate Array(現場可編程門陣列)的縮寫,它是在PAL、GAL、PLD等可編程器件的基礎上進一步發展的產物,是專用集成電路(ASIC)中集成度最高的一種。FPGA采用了邏輯單元陣列LCA(Logic Cell Array)這樣一個新概念,內部包括可配置邏輯模塊CLB(Configurable Logic Block)、輸出輸入模塊IOB(Input Output Block)和內部連線(Interconnect)三個部分。用戶可對FPGA內部的邏輯模塊和I/O模塊重新配置,以實現用戶的邏輯。它還具有靜態可重復編程和動態在系統重構的特性,使得硬件的功能可以像軟件一樣通過編程來修改。作為專用集成電路(ASIC)領域中的一種半定制電路,FPGA既解決了定制電路的不足,又克服了原有可編程器件門電路數有限的缺點。可以毫不夸張的講,FPGA能完成任何數字器件的功能,上至高性能CPU,下至簡單的74電路,都可以用FPGA來實現。FPGA如同一張白紙或是一堆積木,工程師可以通過傳統的原理圖輸入法,或是硬件描述語言自由的設計一個數字系統。通過軟件仿真,我們可以事先驗證設計的正確性。在PCB完成以后,還可以利用FPGA的在線修改能力,隨時修改設計而不必改動硬件電路。使用FPGA來開發數字電路,可以大大縮短設計時間,減少PCB面積,提高系統的可靠性。FPGA是由存放在片內RAM中的程序來設置其工作狀態的,因此工作時需要對片內的RAM進行編程。用戶可以根據不同的配置模式,采用不同的編程方式。加電時,FPGA芯片將EPROM中數據讀入片內編程RAM中,配置完成后,FPGA進入工作狀態。掉電后,FPGA恢復成白片,內部邏輯關系消失,因此,FPGA能夠反復使用。FPGA的編程無須專用的FPGA編程器,只須用通用的EPROM、PROM編程器即可。當需要修改FPGA功能時,只需換一片EPROM即可。這樣,同一片FPGA,不同的編程數據,可以產生不同的電路功能。因此,FPGA的使用非常靈活。可以說,FPGA芯片是小批量系統提高系統集成度、可靠性的最佳選擇之一。目前FPGA的品種很多,有XILINX的XC系列、TI公司的TPC系列、ALTERA公司的FIEX系列等。

ARM作為嵌入式開發最常用的處理器,是嵌入式工程師必須掌握的一門知識。ARM體系架構在嵌入式學院<嵌入式工程師職業培訓班>的二期課程中將會結合嵌入式linux應用開發、嵌入式linux系統移植進行詳細介紹,另外華清遠見的短期培訓業務中也分別有針對ARM、DSP、FPGA的培訓課程。

區別是什么?:ARM具有比較強的事務管理功能,可以用來跑界面以及應用程序等,其優勢主要體現在控制方面,而DSP主要是用來計算的,比如進行加密解密、調制解調等,優勢是強大的數據處理能力和較高的運行速度。FPGA可以用VHDL或verilogHDL來編程,靈活性強,由于能夠進行編程、除錯、再編程和重復操作,因此可以充分地進行設計開發和驗證。當電路有少量改動時,更能顯示出FPGA的優勢,其現場編程能力可以延長產品在市場上的壽命,而這種能力可以用來進行系統升級或除錯。

關鍵詞:單片機;數字信號處理器;現場可編程門陣列

<!--關鍵CH(結束)←--><!--→標題EN(開始)-->

<!--關鍵EN(結束)←-->1 FPGA概述

1.1 FPGA的基本結構

FPGA是高密度的PLD,其集成度可達3萬門/片以上。圖1是Xilinx公司的FPGA,它由三種編程單元和一個用于存放編程數據的靜態存儲器構成。這三種可編程單元是IOB(Input/Output Block可編程輸入/輸出單元),CLB(Configurable Logic Block可編程邏輯單元)和IR(Interconnect Resource互連資源)。它們的工作狀態全部由編程存儲器中的數據設定。CLB提供用 戶所需要的邏輯功能。由于這三部分都是可編程的,所以改變芯片的功能除了靠改變各CLB之間的連接,也可以通過改變各個CLB所實現的邏輯功能來完成。 FPGA中的編程信息將存儲在專用的靜態RAM中;RAM觸發器的每一位,存儲一個編程信息。系統上電時,編程信息就由外部傳入到這些存儲單元中, FPGA就可以按照這些信息來形成內部的構造和連接,以實現所需要的功能。

FPGA中有大量實現組合邏輯的資源,可以完成較大規模的組合邏輯電路設計,而其中相當數量的存儲電路(觸發器)又可完成復雜的時序邏輯電路設計。通過使用各種EDA工具,用原理圖或硬件描述語言,可以很方便地將復雜的電路在FPGA中實現。像典型的數字系統分頻器,數字鐘,數字頻率計等等都可用 FPGA完成。

FPGA的開發系統包括軟件和硬件兩個部分。開發系統軟件指專用的編程語言和相應的匯編程序或編譯程序。開發系統硬件部分包括計算機和編程器。編程器是對FPGA進行寫入和擦除的專用裝置,能夠提供寫入或擦除操作所需要的電源電壓和控制信號,并通過串行接口從計算機接收編程數據,最終寫進FPGA之中。

90年代初Lattice首先推出了一種新型可編程邏輯器件———ISP—PLD(In-SystemProgrammable PLD在系統可編程邏輯器件),將原屬于編程器的寫入/擦除控制電路及高壓脈沖發生電路集成于FPGA中,這樣,在編程時就不必使用編程器,而且由于只需外加5V電壓,所以不必將FPGA從系統中取出,從而實現“在系統”編程。

FPGA設計主要分為設計輸入、綜合、功能仿真(前仿真)、設計實現、時序仿真(后仿真)、配置下載六個步驟。設計輸入包括硬件描述語言HDL、狀態圖與原理圖三種方式。對于簡單的設計,可以使用原理圖或A-BEL進行設計;對于較復雜的設計,可以用行為描述語言(如VHDL語言)和原理圖或二者結合進行設計。功能仿真用來驗證設計的邏輯功能;在設計的過程中,對部分功能或整個設計均可進行仿真。設計實現是指從設計輸入文件到位流文件(只對FPGA而言)。在該過程中,經軟件自動地對設計文件進行映射、布局、布線,產生相應的位流數據文件。時序仿真是在設計實現后,針對器件的布局、布線方案進行時延仿真和分析定時關系。

2 FPGA與單片機

FPGA等大規模可編程邏輯器件可以取代現有的全部微機接口芯片,實現微機系統中的存儲器、地址譯碼等多種功能。利用FPGA可以把多個微機系統的功能電路集成在一塊芯片上。

在功能上,單片機與FPGA有很強的互補性,單片機具有性能價格比高、功能靈活、易于人機對話以及良好的數據處理等特點,而FPGA具有高速、高可靠性以及開發便捷、規范等優點。單片機可用總線方式和獨立方式與FPGA接口。由于其通信工作時序是純硬件行為,對于MCS-51單片機,只需一條單指令就能夠完成所需讀寫時序,也就是最常用的MOV@DPTR,A和MOVA,@DPTR。另外,在FPGA中通過邏輯切換,可使單片機與SRAM或ROM接口,這種方式類似于微處理器系統的DMA工作方式,首先由FPGA與接口的A/D等器件進行高速數據采樣,并將數據暫存于SRAM中,采樣結束后,通過切換,單片機可以與SRAM以總線方式進行數據通信。

目前許多實驗電路板都將FPGA與單片機有機地結合在一起,從而可以完成許多復雜的設計任務。通常單片機負責鍵控、顯示、計算、通信、簡單控制和系統協調,而FPGA負責高速、高精度和高穩定性等指標的實現,也就是說,由單片機負責功能上的設計,FPGA負責指標上的設計。圖2就是一個典型的單片機與 FPGA通信的例子,通過EDA設計(原理圖或硬件描述語言)和單片機匯編語言或C語言的設計,由PC機發命令碼給FPGA,并將FPGA系統上測得的頻率顯示在PC機的屏幕上。這里的單片機起的是通信橋梁作用。

數字信號處理(DSP)在許多領域有著廣泛的用途,如雷達、圖像處理、數據壓縮、數字電視和數字通信機等。一般情況下,采取兩種方案進行數字信號系統的設計,一種是用固定功能的DSP器件或FPGA器件,另一種是采用DSP處理器,如TMS320微處理器。

兩種方法中,固定的DSP器件或FPGA器件可以提供很好的實時性能,但其靈活性較差,不適合在實驗室或技術開發環境中的應用;DSP成本低且速度較快,但由于軟件算法在執行時的順序性,限制了它在高速和實時系統中的應用。目前,大規模可編程邏輯器件為數字信號處理提供了第三種解決方案,FPGA與DSP 相結合,能夠在集成度、速度和系統功能方面滿足DSP應用的需要。由于FPGA器件內部提供了RAM,雙口RAM和FIFO—RAM,所以利用FPGA設計DSP系統,同時具備DSP處理器的靈活性和固定功能的DSP芯片的實時性。

3.1 DSP的特點及其與FPGA相比的優劣

DSP是一種具有特殊結構的微處理器。其內部采用程序和數據分開的哈佛結構,具有專門的硬件乘法器,廣泛采用流水線操作,提供特殊的DSP指令,可以用來快速實現各種數字信號處理算法。DSP適用于條件進程,特別是較復雜的多算法任務。在運算上,它受制于時鐘頻率,而且每個時鐘周期所做的有用操作的數目也受到限制。從效果上看,采用DSP軟件更新速度快,可靠性、通用性和靈活性都很強,但DSP受到串行指令流的限制。

FPGA當中有很多自由的門,將這些自由的門連接起來可以形成乘法器、寄存器以及地址發生器等等。這些只要在框圖級完成,許多塊可以從簡單的門到FIR(有限沖激響應)和FFT(快速傅立葉變換)在很高的級別完成。但它的性能受門數及運算速度的限制。

超過幾MHz取樣率,一個DSP僅僅能完成對數據非常簡單的運算,而這樣簡單的運算用FPGA將很容易實現,并能達到很高的取樣速率。在比較低的取樣速率時,整體上很復雜的程序可以使用DSP,而這對于FPGA是很困難的。

在實時視頻處理的應用中,由于其對系統要求極高,只具備簡單功能的DSP無法完成。而FPGA利用并行處理技術實現視頻處理算法,并且只需單個器件就能完成期望的性能。在中值濾波器的應用中,DSP處理器需要67個周期執行算法,而FPGA只需工作在25MHz頻率下,因為FPGA能并行實現該功能,實現上述功能的DSP必須工作在1.5GHz頻率下。在此應用中,FPGA解決方案的處理能力可達到100MHzDSP處理器的17倍。

3.2 FPGA+DSP方案的運用

上面提到,運用DSP受到串行指令流的限制,而利用FPGA的算術邏輯單元與外部存儲器相結合,可以解決線路板面積有限和有些數據處理需要大量存儲空間的矛盾;利用FPGA并行流水的特點解決了數據實時處理和有限DSP處理速度之間的矛盾,而FPGA運行模式的控制和接收上位機的命令、向上位機輸出目標數據的工作由DSP來完成,從而達到了系統的最佳配置。圖3是FPGA+DSP結構典型的例子。

FPGA+DSP的最大特點是結構靈活,有很強的通用性,適用于模塊化設計,從而能夠提高算法的效率;又由于其開發周期較短,系統易于維護和擴展,適用于實時信號處理。在實時信號處理中,低層信號預處理算法所處理的數據量大,對處理的速度要求高,但運算結構相對比較簡單,適用于FPGA硬件實現,這樣同時兼顧速度和靈活性。高層處理算法的特點是所處理的數據量較低層算法少,但算法的控制結構復雜,適用于用運算速度高、尋址方式靈活、通信機制強大的DSP 芯片來實現。

應用將一些能實現基本數字信號處理功能的DSP模塊嵌入FPGA的芯片是數字電路設計的一個趨勢。有些公司已經計劃把基于ASIC的微處理器或DSP 芯核與可編程邏輯陣列集成在一塊芯片上。FPGA提供的性能已經超過1280億MAC/s(乘法累加運算/秒),大大高于傳統的DSP性能。 QuickLogic公司推出的QuickDSP系列,提供了嵌入式DSP構件塊和可編程邏輯器件。除了以前的可編程邏輯和存儲模塊,還包括專用的乘加模塊;這些合成的模塊可以實現DSP功能。

為了保證順利完成試驗目的,測試系統必須具備高度的可靠性,比如,確保在汽車碰撞試驗中將傳感器測量數據和圖像數據記錄下來。另外,測試環境比較復雜,比如燃料電池測試中的電池堆共模電壓可能超過千伏,需要有良好的對地隔離性能。考慮測試空間、預算等因素,廠商也希望能夠用一個集成的高度可靠的測試系統替代這些不同的分立測試設備,可根據具體應用定義功能,同時又能滿足測試環境和技術指標的要求。

因為現場可編程門陣列(FPGA)技術具有自定義邏輯功能和高可靠性的特點,所以,工程師可將FPGA技術融入測試系統,解決上述車載測試困難,同時滿足低成本、系統可擴展性和復雜的測試環境要求。本文將探討FPGA相關技術在車載測試中的應用。

FPGA技術一個平臺 多種應用

FPGA(Field Programmable Gate Array),是PAL、GAL、PLD等可編程器件進一步發展的產物,其邏輯功能由內部規則排列的邏輯單元陣列(Logic Cell Array)完成。邏輯單元陣列內部包括可配置邏輯模塊(Configurable Logic Block)、輸入輸出模塊(Input Output Block)和內部連線(Interconnect)三個部分。工程師可通過軟件編程實現FPGA內部的邏輯模塊和I/O模塊的重新配置,以實現自定義的邏輯。

FPGA技術有很多優勢,包括自定義I/O硬件定時和同步、高度可靠性、數字信號處理和分析等。這些優勢為快速增長的汽車電子">汽車電子測試技術提供了靈活的低成本解決方案。下文以車載測試為例進行討論。

不同車載測試的技術指標也不同,包括采樣率、信號調理、處理和分析。比如,采樣率范圍從GPS數據記錄的15Hz到碰撞試驗的200kHz不等。而FPGA直接連接到數字和模擬I/O,可對各通道定義不同的采樣率和觸發。所以,可應用FPGA技術實現單個系統解決所有這些車載測試應用,避免定制硬件或多個測試系統的需要。即單個FPGA平臺既可用于低速、高精度GPS或溫度記錄;又可通過快速編程實現用于有高采樣率要求的碰撞試驗;也可將不同采樣率以并行方式共存于同一個測量應用中,比如,在配置FPGA實現10Hz溫度采集的同時進行50kHz的振動測試;并可實現任何I/O之間的同步,比如,實現CAN總線數據和數字或模擬I/O信號間納秒級的同步測量。沒有FPGA技術,則很難實現單個系統同時滿足這些不同的車載測試需求。

應用FPGA技術,可對任何傳感器信號進行高級信號處理和分析。在很多信號處理系統中,底層的信號預處理算法要處理大量的數據,對處理速度要求很高,但算法相對簡單,可用FPGA進行編程實現。此外,可很方便地在FPGA上實現對所采集的信號作數字濾波運算、快速傅立葉變換(FFT)、加窗等多種信號處理和分析。傳感器級信號處理和分析功能使FPGA技術已成功應用于高速數據采集處理卡和高速圖像采集處理卡的研發。

此外,利用FPGA可自定義邏輯功能開發定制板卡,用于發動機控制單元(ECU)的快速原型設計和硬件在環仿真(HIL)等研究。FPGA可實現硬件層面極快的閉環控制循環速率。通過FPGA編程對CAN、模擬或數字的信號輸入作出快速響應,同時FPGA的并行性允許將多個快速控制循環集成在同一個系統中。例如,Drivven公司應用FPGA的可重復配置性能,實現了Yamaha YZF-R6發動機控制系統的原型設計,而避免了在設計過程中購買多個定制硬件的需要,從而降低了成本;MicroNova同樣使用基于具有高可靠性、可定制邏輯功能的FPGA硬件平臺實現了世界上第一個V12汽油發動機的硬件在環仿真。

圖形化FPGA編程

FPGA技術有很多優點,比如可自定義邏輯、高可靠性等,可廣泛應用于車載測試和開發定制板卡。但工程師在FPGA編程時,往往需要掌握硬件設計語言如VHDL之類的知識。而圖形化開發工具,比如National Instruments (NI)的高效圖形化開發環境LabVIEW,則是專為需要建立靈活的可擴展性測試測量和控制應用系統的工程師和科學家設計的,以滿足他們以最小的成本、最快速的開發系統的需求。

LabVIEW直觀的圖形化開發特性,可使工程師把更多的精力集中在功能開發上,而不是代碼撰寫上,進而大幅縮短開發時間和成本。LabVIEW又是一個開放性的軟件平臺,對于一些特定的應用,提供多種工具包和模塊來提升和加速系統開發。比如,LabVIEW FPGA模塊,工程師就無須硬件描述語言和硬件設計相關專業知識,便可在WINDOWS操作系統上,通過圖形化開發自定義的FPGA邏輯代碼并下載到FPGA硬件目標,來實現創建自定義硬件。如圖1所示在FPGA上實現CAN數據和數字或模擬信號間納秒級的同步測量。當測試要求改變時,可通過下載新的代碼到FPGA,而無需新的定制硬件。同時,提供VHDL語言接口,為方便工程師直接使用現成的VHDL代碼。LabVIEW Real-Time模塊用于針對實時硬件目標開發時間確定性的應用程序;嵌入式開發系統模塊適用于任何32位處理器的圖形化開發;DSP模塊則適用于圖形化DSP算法開發,集成數字濾波器設計工具包;信號處理工具包適用于測試數據的高精度頻譜分析和顯示。總之,圖形化開發軟件LabVIEW將極大地提高工程師的工作效率。

圖1 用NI LabVIEW實現FPGA圖形化編程

使用LabVIEW FPGA軟件和可重復配置硬件技術,可創建高性能的控制和采集系統。下面舉兩個例子,有關基于FPGA技術的硬件平臺在車載測試中的應用。

用戶解決方案1:便攜式車載數據采集系統

車載數據采集的信號類型包括溫度信號(熱電偶、RTD)、聲音和振動信號(帶IEPE激勵的加速度傳感器或麥克風)、壓力和載荷信號(應變計或稱重傳感器)、位置信號(LVDT或線性電位計)、速度信號(編碼器)、控制總線信號(CAN,J1350,ODBII),以及視頻信號等。這些信號都是用于汽車性能的評價。

德國Goepel Electronic公司在面臨上述信號類型、環境條件復雜、有大量數據存儲要求,用于車載測試分析和在線診斷的便攜式測試設備時,選擇了NI CompactRIO嵌入式控制系統,LabVIEW FPGA模塊和LabVIEW Real-Time模塊。在很短的時間內開發了CARLOS (in-car logging system),加上CompactRIO平臺的低成本解決方案,從而大大節省了預算。

圖2 Goepel CARLOS 車載數據采集系統

CompactRIO硬件平臺(參看圖2)是一個基于FPGA技術的嵌入式系統。FPGA芯片是CompactRIO體系結構的核心,直接和相應的車載模塊相連。車載模塊可直接和車用傳感器、執行器和網絡相聯,并提供信號調理、隔離和汽車總線。該平臺包含一個嵌入式實時處理器,可用于獨立工作、確定性控制、車載數據記錄和分析等。CompactRIO具有小型、堅固的機械封裝、可承受50g沖擊和-40 oC到70 oC工作溫度范圍等特點,提供雙電壓輸入(9~35V),可直接從車上電池取電。這些都使CARLOS適用于復雜的車載測試環境和有限的測試空間。

該系統已成功用于實驗室、風洞和試驗場上的汽車測試,可長時間記錄數據。另外,可通過選擇相應的車載模塊和內置的應用程序,實現不同測試的需求。比如為了實現冬季或夏季試驗中發動機熱管理系統的評價,只需選擇溫度等信號對應的車載模塊和已開發好的LabVIEW應用程序即可;同時,該程序提供報警、用LabVIEW報告生成工具包實現數據寫入EXCEL表格、或直接寫進數據庫、歷史數據查看等功能。此外,基于FPGA的CompcatRIO開放試架構允許用戶擴展系統或進一步開發自定義的測試系統。

用戶解決方案2:自定義遠程模塊開發

無線通信技術已廣泛應用于汽車在行進中實現監控狀態、精確定位或遠程通信,包括GPS導航和精確定位、胎壓監測等;其中,GPS在日本和歐美汽車上安裝的普及率逐年上升,在國內也越來越受關注。

德國S.E.A. Datentechnik GmbH公司針對車載無線通信測試的需求,為了盡快將產品投入市場,選擇了基于FPGA技術的CompactRIO開放式硬件平臺和LabVIEW開發環境。根據車載遠程控制、數據采集、位置跟蹤等應用需求開發了cRIO GPRS(General Packet Radio Service)、 cRIO GPS(Global Positioning System)、cRIO RCC(Radio Controlled Clock)和一個混合模塊cRIO Gxxx,如圖3所示。最終,整個項目的開發時間比原計劃提前了40%。

圖3 S.E.A. Datentechnik遠程模塊

GPS模塊通過接收L1波段的GPS信號實現精確的定位。接收機可以在啟動之后將數據轉換成NMEA 0183格式,以便進一步分析。備份電池可以保證接受機的記憶功能,存儲以前的信息,比如位置數據。該模塊可用于汽車導航、精確定位。GPRS模塊通過GSM/GPRS公網進行測量數據和事件消息傳輸,同時使用SIM卡讀卡器接入GSM/GPRS網絡,以短信方式手法數據,可應用汽車防盜系統。RCC模塊用于分布式系統的時間同步;混合模塊則集合了以上功能。在車載應用時,CompactRIO嵌入式系統的高度可靠性得以充分體現。

這些模塊除用于車載測試外,還可廣泛應用于ATM終端、工業和醫療遠程系統、遠程診斷等。

總結

FPGA技術帶來了車載測試技術的創新,憑借開發基于FPGA硬件的單個系統可以解決不同的車載測試應用,而無需多個定制的測試設備。圖形化FPGA編程則進一步縮短開發時間。NI CompactRIO是基于FPGA的硬件平臺之一,用戶可以開發適用于涉及汽車總線、不同信號類型的車載測試應用,甚至可以自己定制開發模塊實現特定的車載測試功能。

QUOTE:

我估計得幾萬美刀吧?我知道中國很多軍用fpga都是直接又商用芯片,直接拿去測試,只要能達到軍品標準的,就是“軍品”。QUOTE:

呵呵,是,幾萬美元一片!一方面是因為你根本買不到,所以就貴;另一方面就象你說的,得挑,那可是千里挑一、萬里挑一啊;從商業級和工業級的芯片里去挑軍品級的,呵呵,你可以想像是怎樣的一個浪費哦。QUOTE: