�����S���ƌW(xu��)���g(sh��)�İl(f��)չ��Ƕ��ʽ̎������ͨ���O(sh��)�䡢���M(f��i)�����܊����ӵ��I(l��ng)�����ˏV���đ�(y��ng)�ã����Ҍ�̎������̎���ٶȡ����ļ������ضȶ����˸��Ӈ�(y��n)���Ҫ����������܇��ӡ�܊����ӵȷ���đ�(y��ng)�á�

����PowerPC �wϵ�Y(ji��)��(g��u)��һ�N����ָ�Ӌ(j��)��C(j��)��Reduced Instruction Set Computer��RISC���wϵ�Y(ji��)��(g��u)�����и����ܺ͵��ĵ����c(di��n)����Ҫ��(y��ng)����Ƕ��ʽϵ�y(t��ng)�У���������ΰ�Ӌ(j��)��C(j��)���M(j��n)�и�����Ӌ(j��)��͈D��̎����

������PowerPC �����У��F(xi��n)�ڑ�(y��ng)�����V������G4 ϵ��, G4 ��G3 ���ش���M(j��n)�Ѓɂ�����һ��֧���Q��̎������SMP���Y(ji��)��(g��u)���ڶ���G4 ������һ����AltiVec ���g(sh��)��̎��ʸ���\(y��n)�㡣

����AltiVec ���g(sh��)��һ��128 λ��SIMD ʸ��̎�����棬��(j��)Motorala *������ʹ����������ԭ����4.3 ����

����������PowerPC G4 ���C(j��)̎������������B��(bi��o)��(zh��n)6U �߶�CompactPCI �ΰ�Ӌ(j��)��C(j��)��Ӳ���O(sh��)Ӌ(j��)�Լ���(sh��)�r����ϵ�y(t��ng)VxWorks ��BSP �_�l(f��)�^�̡�

����2 �ΰ�Ӌ(j��)��C(j��)Ӳ���_�l(f��)

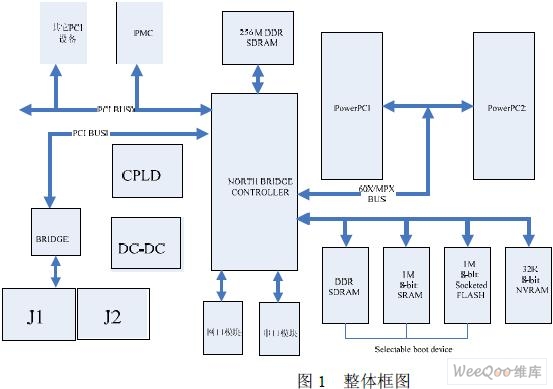

�����ΰ�Ӌ(j��)��C(j��)�����w��D��D1 ��ʾ��

���������ΰ���O(sh��)Ӌ(j��)�֞��������֣��Դģ�K��PowerPC ���ֺ�ͨ�Žӿڲ��֡�����PowerPC ���ֺ�����ӿ���PCI ������ֽ羀��PowerPC ���ְ���PowerPC��host bridge��SDRAM ��FLASH��

��������ӿڰ����W(w��ng)�ڡ����ڡ�ͨ�^PCI �����U(ku��)չ�Ľӿں͔U(ku��)չ�Ķ���PCI �������W(w��ng)�ںʹ������_�l(f��)�A�����چΰ���_�l(f��)���C(j��)ͨ�ţ������چΰ�Ƕ�����ϵ�y(t��ng)����������ΰ�֮�g��ͨ�Žӿڡ���D��PowerPC �]��ָ�����w����̖�������x��IBM ����PPC750�� Ҳ�����x��Freescale����PowerPC G4 ϵ�е�MPC74XX��host bridge �����x��MARVELL ��˾��MV64360 ��MV*60���Ñ����Ը���(j��)�IJ�ͬ��Ҫ�x������(y��ng)�ĽM�ϡ�

����2.1 �Դģ�K���O(sh��)Ӌ(j��)

�����Դ���κ�һ���·ϵ�y(t��ng)���P(gu��n)��Ҫ�IJ��֣����е���̖��ݔ���ǻ��ڜ�(zh��n)�_����(w��n)�����Դ���A(ch��)�ϵġ�CPCI �B�����ṩ���Դ��5V��3.3V��12V ��-12V�������ΰ�����Ҫ���Դ�ж�N�����Դ5V��PowerPC �ă�(n��i)���Դ��host bridge ��(n��i)���Դ��DDR SDRAM �Դ������I/O�����Դ3.3V�������������Դ��(w��n)����Ҫ��ߵģ���(y��ng)���ÿɾ��̵�DC/DC ����оƬ����Դ���D(zhu��n)�Q��

�����Դģ�K��PCB ����ҲҪ�M(j��n)��С��̎���� ��Ҫ�����ׂ�������Ҫע�⡣

����a) ����ȥź��ݣ��S��һ����(sh��)����ȥź��ݱ������ڰ��ϣ��·�屾�����е��C����Ա����Ƶ����Ķ��p�����Įa(ch��n)����߀���Խ����·��߅��ݗ���Ծ���늴ż��݆��}����������Դ���ϵ�y(t��ng)�Ŀɿ��Ժͽ���ϵ�y(t��ng)������ɱ�����(y��ng)���]��ν�(j��ng)��(j��)��Ч���x��ȥź��ݵ�ϵ�y(t��ng)���֡�

����b) �����Դ���ϵ�y(t��ng)���迹��һ��������Դ���ϵ�y(t��ng)(��ֱ��������)�ǫ@�õ�늉����ӵ��P(gu��n)�I���p��늸����ã�����������ã���������Щ�C������O(sh��)Ӌ(j��)Ŀ��(bi��o)�����_(d��)����Ŀ��(bi��o)��(y��ng)�����Դ�͵ذ��֮�g���g�ࣻ ����ƽ��ijߴ磻��������|(zh��)�Ľ�늳���(sh��)�����ö����Դ�͵ذ�ӡ�

����2.2 PowerPC ����

����PowerPC ���ְ���PowerPC1&2��host bridge��DDR SDRAM��SRAM ��Flash���˲����������ΰ�Ӌ(j��)��C(j��)�ĺ��ģ��·�O(sh��)Ӌ(j��)�{(di��o)ԇ�y��Ҳ���PowerPC1&2 ��DDR SDRAM �����ٶ��^�죬�·�O(sh��)Ӌ(j��)Ҫע��PCB �����x����m����?f��)�Y(ji��)��(g��u)�Ͳ�������, �Ա��C��̖�����ԡ�

����a) ��?f��)�Y(ji��)��(g��u)���`�(y��ng)��

������ PCB �O(sh��)Ӌ(j��)�г��õ���?f��)�Y(ji��)��(g��u)�оջ����?f��)�������ؓ(f��)䡣Ҫ���?j��)��ͬ����r���ò�ͬ����?f��)�Y(ji��)��(g��u)��

����һ����ԣ����ڶ�ؓ(f��)�d�Ŀ���ϵ�y(t��ng)�����þջ����?f��)䣬�������h(yu��n)�˵�ؓ(f��)�d̎�M(j��n)���m��(d��ng)?sh��)ĽK�Y(ji��)���ջ����?f��)�ă?y��u)�����������M(j��n)���迹���ƣ��˽Ӻ��Σ��W(w��ng)�j(lu��)�IJ����L�ȶ̣������^�鷽�㣬ֻҪ�����������ڽ�����̖�r�g�ϵIJ�e�����S�ķ�����(n��i)�Ϳ��Բ��þջ����?f��)��M(j��n)�в������@Ҳ�f���ջ����?f��)䲻�m���ڸ���ϵ�y(t��ng)����ע��Ҫ�ջ�朵ķ�֧���M���̡�Local bus �ϵ����O(sh��)�҂����õĴ˷N��?f��)�Y(ji��)��(g��u)��local bus ����Flash��DDR SRAM��SRAM �����O(sh��)��

����������?f��)�һ���ڕr犾W(w��ng)�j(lu��)��?q��)���̖ͬ��Ҫ��ߵľW(w��ng)�j(lu��)�Б�(y��ng)�ã��乲ͬ�c(di��n)����Ҫ�����������ͬһ�r���յ��(q��)�Ӷ˰l(f��)������̖��������?f��)�IJ����y�ȱȾջ����?f��)��Ҫ��ռ�ÿ��gҲ��(sh��)�H��������?f��)�����ڶ˽ӂ�ݔ����֧���(q��)�����c������(ji��)�c(di��n)�g���ڂ�ݔ����֧���@Щ�����ӻ���̖���������O(sh��)Ӌ(j��)������?f��)�һ����Ҫ���棬�Ա��C��̖�������ԡ�

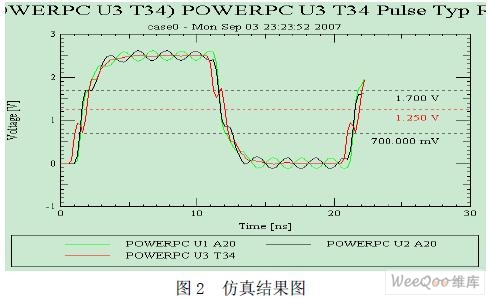

����PowerPC1&2��U1��U2����host bridge��U3������������?f��)�Y(ji��)��(g��u)��������D����D2 ��ʾ�������M����̖�����ԡ��r��·����������?f��)�Y(ji��)��(g��u)��һ����������host bridge��ݔ�����(zh��n)�r犣������r状���host bridge ���ṩ������ PLL Ҫ�x����m�ą���(sh��)���ã�ʹ��оƬ���·��(w��n)���\(y��n)�С�

����b) ��(y��n)��ĵ��L����Ҫ��

������SDRAM �O(sh��)Ӌ(j��)�r��Ҫע���{(di��o)�����_SDRAM_SYNC_OUT ��SDRAM_SYNC_IN ֮�g�IJ����L�ȣ�ʹ��SDRAM ��(sh��)��(j��)�����r犵Ľ����r�g�ͱ��֕r�g�õ��ܺõĝM�㡣PCI ���ֵĕr�Ҫע����_PCI_SYNC_OUT ��PCI_SYNC_IN ֮�g�IJ����L�Ⱥ�PCI_CLK ��ͬ��

����2.3 ͨ�Žӿڲ���:

����ͨ�Žӿڌ�(sh��)�F(xi��n)��-�C(j��)���C(j��)-�C(j��)֮�g����Ϣ�����͔�(sh��)��(j��)�Ă�ݔ���oՓ����ϵ�y(t��ng)�{(di��o)ԇ��߀����ϵ�y(t��ng)��(y��ng)���ж��dz���Ҫ����D1 ��ʾ��host bridge �����˃ɂ����ں�3 ��ǧ�W(w��ng)��������ͨ�^��Ӵ��ں;W(w��ng)�ڵ��հl(f��)���O(sh��)Ӌ(j��)�Ñ������ͨӍ�ӿڡ�

�������ں;W(w��ng)�����_�l(f��)�^����������Ҫ�����á����ô��ڣ�ͨ�^�����K�˻������K��ܛ�������Կ����{(di��o)ԇ�^���еĴ�ӡ����Ϣ���Ԏ����{(di��o)ԇ�����þW(w��ng)�ڣ�����ͨ�^�W(w��ng)�j(lu��)���d�ļ����ߒ��d�ļ�ϵ�y(t��ng)��

�������⣬host bridge �ṩ�ɽMPCI ����������ͨ�^PCI �U(ku��)չһЩ���O(sh��)�ӿ���IDE��USB���W(w��ng)�j(lu��)�ȣ����Ը���(j��)��Ҫ�M(j��n)������(y��ng)�ĔU(ku��)չ��ͬ�r���ԔU(ku��)չ��PMC �ӿڣ��B�Ә�(bi��o)��(zh��n)��PMC �O(sh��)�䡣���⣬�x��һ�MPCI ������ͨ�^PCI to PCI bridge ��������J1 ��J2�������c���O(sh��)�����B������ϵ�y(t��ng)�ĔU(ku��)չ�������ڌ�ϵ�y(t��ng)�\(y��n)��̎������Ҫ���^�߶�ϣ�������ڱ��^���뷶����(n��i)�ĸ߶ˑ�(y��ng)�È��ϣ������ɂ����߃ɂ����ϵ�̎�����Զ�̎�����ķ�ʽ�f(xi��)ͬ�������M�ɲ�ͬ�Ķ��C(j��)ϵ�y(t��ng)��

����3 VxWorks BSP �_�l(f��)

����Ƕ��ʽϵ�y(t��ng)���_�l(f��)����Ҫ��Ӳ���O(sh��)Ӌ(j��)��ɺ�Ƕ�����ϵ�y(t��ng)�����M(j��n)���όӳ�����_�l(f��)��VxWorks �������L(f��ng)�ӹ�˾�Ƴ���һ����(sh��)�r����ϵ�y(t��ng)�����nj��T�錍(sh��)�rǶ��ʽϵ�y(t��ng)�O(sh��)Ӌ(j��)�_�l(f��)�IJ���ϵ�y(t��ng)��(n��i)�ˣ�����(qi��ng)����ұ��^��(f��)�s�IJ���ϵ�y(t��ng)���������M(j��n)�̹������惦�������O(sh��)��������ļ�ϵ�y(t��ng)�������W(w��ng)�j(lu��)�f(xi��)�h��ϵ�y(t��ng)��(y��ng)�õȎׂ����֣���ֻռ���˺�С�Ĵ惦���g�����ɸ߶ȲÜp�����C��ϵ�y(t��ng)�����^�ߵ�Ч���\(y��n)�С���ϵ�y(t��ng)�_�l(f��)�^����һ�(xi��ng)��Ҫ�Ĺ�����(n��i)�����_�l(f��)�弉֧�ְ�BSP(Board Support Package)��

����3��1 BSP �ĸ���

����BSP ���^�ļ���Դ�ļ���makefile �ļ��������ļ��M�ɡ����������cӲ�����P(gu��n)��ܛ���Ͳ���Ӳ���o�P(gu��n)��ܛ�����ṩVxWorks �L��Ӳ�����(q��)�ӳ�������P(gu��n)�O(sh��)��ij�ʼ���������܌�CPU��Ŀ��(bi��o)�C(j��)��ϵ�y(t��ng)�YԴ���M(j��n)�г�ʼ�����ڳ�ʼ���^���У�������CPU ��(n��i)����B(t��i)�Ĵ��������ƼĴ��������پ����M(j��n)���O(sh��)�ã����ό�ܛ��ϵ�y(t��ng)�ṩӲ���h(hu��n)����֧�֣����Ҟ����ϵ�y(t��ng)�����\(y��n)���M(j��n)���YԴ��ʼ����

����3��2 �{(di��o)ԇ�^��

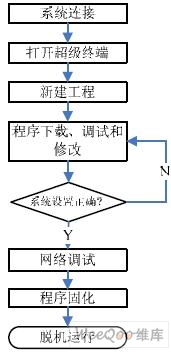

����ϵ�y(t��ng)�O(sh��)Ӌ(j��)�r����Bootrom ��VxWorks �ķ�ʽ���@�N������ʽ���䪚(d��)��(y��u)�c(di��n)�����m��(y��ng)Ӳ��������F(xi��n)���{(di��o)ԇ�ȡ�ϵ�y(t��ng)���õ��{(di��o)ԇ������Wind River ��˾���{(di��o)ԇܛ��visionCLICK ��������Wind River ICE�����w���E���D ��ʾ��

����(1) ϵ�y(t��ng)�B��

�����B�Ӻ÷�������Ŀ��(bi��o)�塣��Ҫ���Դ�����ڡ�JTAG �ڡ�

����(2)���_�����K��

������늺��÷������Ĵ����B����X��RS 232 ���ڣ����_�����K�ˣ����·������ď�(f��)λ�I���ڳ����K�˿ɿ��������������P(gu��n)��Ϣ����Ҫ��IP Address�����C(j��)(host)��IP �ĵ�ַҪ�ͷ�������IP ��ַ��ͬһIP �Σ��ڳ����K�˿��\(y��n)��help ����ɿ������N��������\(y��n)�С��\(y��n)��"eth-setup"����ɸ��ķ�������IP ��ַ��

����(3) �½�����

�������_ visionCLICK���½����̣�������ʾ�O(sh��)�ã���Ҫ�У�configuration file��symbolfile��download file ��sourcepath���������x�(xi��ng)Ĭ�J(r��n)������bootrom uncmp��a(ch��n)b

����(4)�������d���{(di��o)ԇ����

�����B�ӷ����������d���\(y��n)�С���ʾ�o�`���^������ڵļĴ�������(n��i)��Ȇ�Ԫ��ֵ���M(j��n)ԇ�������e�`����Դ���a�������_ʼ���g�����d��ֱ����ȫ���_��ֹ��

������5���W(w��ng)�j(lu��)�{(di��o)ԇ

����BootROM �{(di��o)ԇ���Ŀ��(bi��o)�����̫�W(w��ng)�ں����C(j��)�ľW(w��ng)�����B��VxWorks ���ԄӏľW(w��ng)������(d��o)���Ѿ��g�õ�VxWorks ���d��Ŀ��(bi��o)�壬�M(j��n)���{(di��o)ԇ��

������6������̻���Ó�C(j��)�\(y��n)��

�������ȫ����ɺ�BootROM ��VxWorks ���̻���Ŀ��(bi��o)���ϣ��Ա�Ó�C(j��)�\(y��n)�С�

����4 �Y(ji��)���Z

�����������߄�(chu��ng)���c(di��n)���x��PowerPC G4 ϵ���_�l(f��)�ΰ�C(j��)�����ڿ�������ĵ��ģ���(sh��)�F(xi��n)����(sh��)��(j��)������̎����ͬ�rϵ�y(t��ng)�S���Ľӿ��O(sh��)Ӌ(j��)�͘�(bi��o)��(zh��n)��CPCI �Y(ji��)��(g��u)������ϵ�y(t��ng)�ĔU(ku��)չ�ͽM�����C(j��)ϵ�y(t��ng)���S���Ƽ��İl(f��)չ��ԓ�NӋ(j��)��C(j��)�����M(f��i)��ӡ�ͨ���O(sh��)�䡢���I(y��)���ƺ�܊����ӵ��I(l��ng)��������õđ�(y��ng)��ǰ����

]]>�µķ�����A(ch��)�O(sh��)��ܘ�(g��u)����ȡ��ԭ����TDM���A(ch��)�O(sh��)ʩ���@��ζ���C(j��)���еĔ�(sh��)��(j��)�l��Ҫ������10��100Mbps��ߵ�Gb��Tb�ȼ���Compact PCI�е�PCI�R���şo���ṩ����l������ʹ����Gb���ʵ�PICMG 2.16���壬Ҳ�o��֧Ԯһ���pGb��̫�W(w��ng)·�塣���⣬�S���l����������Ҳ��Ҫ�����·����g�c���ʁ��M(j��n)�Д�(sh��)��(j��)̎����

|

�D1��MPC8548 AMC�����O(sh��)Ӌ(j��)���� |

��ATCA��(bi��o)��(zh��n)���w�˙C(j��)�ܳߴ硢���ʺͭh(hu��n)����(bi��o)��(zh��n)�ȣ�����߀�{������Ůa(ch��n)�I(y��)������Ҫ�����m����Ҫ����̎�����ܵĸ��ܶȑ�(y��ng)�ã���o�����Z����(y��ng)�á��о���(sh��)��(j��)����������_(d��)10Gbps�Ĺ��ݔ��(y��ng)�á�

��M���@Щ��(y��ng)������PICMG 3.x ATCA���g(sh��)Ҏ(gu��)���x��֧Ԯ��N�ؘ����úͻ��B���g(sh��)�ı���ܘ�(g��u)������Gb��̫�W(w��ng)·�ʹ���RapidIO���档�����ʽ��Q��ꇼ��g(sh��)���چ�һ�C(j��)���ό�(sh��)�F(xi��n)2.5Tbps�Ľ��Q��̎�����ʡ�ATCA߀������������ƽ�_�Ļ����C(j��)�ơ��@��һ�N���M(j��n)�^�̣����O(sh��)���u�����ṩ�˽���(g��u)������ֵ�I(y��)��(w��)�Ļ��A(ch��)ƽ�_��

ATCAĿ��(bi��o)��(y��ng)�ü�ǰ��

�S���W(w��ng)·��ĭ�Ɯ���S����ŘI(y��)�l(f��)չ�ٶȵĜp�����S��OEM��ODM��Ƹ�˴��������ˆT���F(xi��n)�ڣ��S��ͨӍ�Ј�����(f��)�d�����Еr�g�ɞ���Ҫ�ijɹ����ء����Ø�(bi��o)��(zh��n)ƽ�_�܅f(xi��)����˾Ѹ���_�l(f��)��Q�������������r�g�����������ֵ�I(y��)��(w��)(��ܛ�w����(w��))���ڸ�����Ó�f������

ATCA��Ŀ��(bi��o)�ǟo����ȡ���o��EDGE���о���ȡ�ͺ��Ă�ݔ�Ј����@Ȼ�������Ⱥܿ��ܕ���2/2.5/3G�o�����A(ch��)�ܘ�(g��u)�Ј���ȡ�óɹ���������_������(BSC)���o���W(w��ng)·������(RNC)������(w��)GPRS֧Ԯ��(ji��)�c(di��n)(SGSN)���W(w��ng)·�l��GPRS֧Ԯ��(ji��)�c(di��n)(GGSN)��ý�w�W(w��ng)·�l��(MGW)���Єӽ��Q����(MSC)�ȡ�

��(j��)Crystal Cube Consulting(CCC)�A(y��)������2009��ף�AMC���Ј������~���_(d��)��140�|��Ԫ��ATCA�Ј������~���_(d��)��420�|��Ԫ����In-Stat/MDRҲ��Ӌ(j��)ATCA��(bi��o)��(zh��n)�C(j��)���������A(y��)Ӌ(j��)���_(d��)��184�|��Ԫ��

����֧ԮATCA��(bi��o)��(zh��n)��ģ�M�����棬Ŀǰ�����a(ch��n)�I(y��)����PCI�A�ӿ�(PCI Mezzanine Card��PMC)�ͽ��Q�A�ӿ�(Switched Mezzanine Card��XMC)�D(zhu��n)����A�A�ӿ�AMC(Advanced Mezzanine Card)����Ҫ����?y��n)�AMC֧Ԯ���Σ�ʹ��AMC�܉��ṩ���о��̹��ܵĬF(xi��n)������Qģ�M�������(w��)�ˆT����O����`���ԣ��K�f(xi��)���S�̽����Y��֧����

�I(y��)�������h��MicroTCAƽ�_���S��1���C(j��)�������ʹ��12��AMC��������ҪATCA���d�������@Щ��(bi��o)��(zh��n)ģ�M��(chu��ng)���˸����̙C(j��)��MicroTCA��ҕ��ATCA���a(b��)�䣬���������������Ј��ṩ�ɱ����͵�·�ɣ��e�nj��ð忨�I(l��ng)����܊�¡��t(y��)ˎ���I(y��)�Ԅӻ��Ј��еĸ�����Ƕ��ʽ��(y��ng)�á��^����(qi��ng)AMC��MicroTCA���Ј�֧Ԯ���ռ����ȣ�����ĘI(y��)��(w��)�������ṩ��(bi��o)��(zh��n)�忨�Ĺ�˾�����µęC(j��)�����@���^�����f(xi��)���K�˿͑�����ÿ��ģ�M������(g��u)�^(q��)�K�ijɱ���

ATCA��AMC����������(zh��n)

ATCA��AMC���g(sh��)Ҏ(gu��)����Ƴ���忨�O(sh��)Ӌ(j��)�ˆT�����һϵ���µ�����(zh��n)���^ȥ���忨�O(sh��)Ӌ(j��)�ˆTֻ�迼�]�R����ؓ(f��)�d�������O(sh��)Ӌ(j��)���ʹ����Ȇ��}���F(xi��n)�ڣ�����߀��횿��]�忨����Ŀ��g��ɢ�����ܣ��_���������cATCA��ϵ�y(t��ng)�o�p���ϡ��@����ʹ�O(sh��)Ӌ(j��)�ˆT����ӹ��̎�׃��ϵ�y(t��ng)�O(sh��)Ӌ(j��)���ҡ�

|

�D2��ATCA����ƽ�_�� |

�ɷN���g(sh��)Ҏ(gu��)��忨�O(sh��)Ӌ(j��)�ˆT���x�˰�����(d��)���O(sh��)Ӌ(j��)����(zh��n)���h(hu��n)������������Ҫ�ăɂ������ǰ忨�ߴ��ɢ�ᆖ�}��

1. �忨�ߴ�

����AMC�Еr���`�J(r��n)����PMC����������忨�O(sh��)Ӌ(j��)�ˆT�ṩ�˱�PMC������ı���e��AMC���g(sh��)Ҏ(gu��)�����S�ɷN��ͬ��PCB�ߴ磬���ІΌ����ߴ�s75mm �� 180mm���p�����s149mm �� 180mm�����d�w�ܶȷ��棬��(bi��o)��(zh��n)8U�d�w���ݼ{4���Ό�����2���p������1���p������2���Ό���(���O(sh��)����ȫ�ߡ�����ǰ�߿�����(sh��)���͕�����)��

�x��ηN�忨�ߴ��@Ȼȡ�Q��ض���(y��ng)�����������Ƭ��(sh��)�������ǣ�����Ƭ��(sh��)�������x���O(sh��)��ߴ��Ψһ���]���ء��p��PCB���H��ζ�����ÿ��g�܉�����һ����߀��ζ������ǰ������ṩI/O������~����g������һ���忨��Ҫ�������Ƭ��(sh��)�����S�O(sh��)Ӌ(j��)�ˆT���˿��sС��Ό�AMC����I(xi��n)/O���ܕ�Ҫ��ʹ���p���������磬ʹ�ÆΌ����r��ǰ����Ͽ���ֻ��3��RJ45���^(ӛס��LED�Ͱ����_�P(gu��n)ҲҪ��(zh��n)�ÿ��g)������(j��)�忨��I/O���@�����h(yu��n)�h(yu��n)���������ʹ�O(sh��)Ӌ(j��)�ˆTʹ���p������

�˂��ѽ�(j��ng)�_�l(f��)���߶����ϵ�̎����(�������ϵ�ӛ���w������������RapidIO��PCI Express SERDESģ�M)����������ˌ���Ӿ�Ƭ���L߅�O(sh��)���Ҫ����ʹ��ˣ�����ע��忨���g���}��

ͬ�r��ATCA���g(sh��)Ҏ(gu��)��߀��忨�O(sh��)Ӌ(j��)�ˆT�����ˇ�(y��n)�����ơ�է��֮�£����g(sh��)Ҏ(gu��)���ṩ�Ĵ�忨�ߴ���ṩ���ýM���������g�����ǣ���(y��n)��ġ��A(y��)�����g��(����֧ԮAMC�������ӡ��M���ԴҪ��֧Ԯ���廥�B)����Ҳ����sС���d�w�ϵĿ��ÿ��g��

2. ɢ�ᆖ�}

���ܼ��g(sh��)Ҏ(gu��)���Ό�AMC��Ҏ(gu��)����60W�Ĺ����A(y��)�㣬���O(sh��)Ӌ(j��)�ˆT�l(f��)�F(xi��n)�������Ŀ��ÿ��g��(n��i)Ҫ��Чɢ��dz����y���˂��ձ��J(r��n)�飬�����(sh��)AMC�����b��ATCA�C(j��)���ϣ������ṩ�Ę�(bi��o)�Q������1m/s������(y��ng)ԓӛס������4�����M�ɵ��d�w�ϣ�����1��AMC��ֻ����ǰ��3�����ų���ů�����M(j��n)����s���O(sh��)Ӌ(j��)�ˆTϣ����ɢ�ᱣ�������ˮ��(zh��n)���@�r�����ϵĵ���̎�����dz����ã�������߀��Ҫʹ��ij�N�����b�á�

ATCA�d�w�����A(y��)�㹦��ĿǰҎ(gu��)����200W����(d��ng)Ȼ���҂�߀��(y��ng)�eע���d�w����Kʹ�õ�AMC�������磬�������2���~�����ʞ�60W��AMC�����d�w���N���ݾ�ֻ��80W���A(y��)�㹦���ˡ��c�^ȥ��ͬ�������҂���ȫ�������@�������A(y��)���(n��i)����O(sh��)Ӌ(j��)�����O(sh��)Ӌ(j��)�ˆT��(y��ng)�O(sh��)����������ʡ�

������Ƭ�O(sh��)Ӌ(j��)��Ӱ�

ATCA��AMC���߶����ϵĵ����O(sh��)���Ҫ���ь�Ԫ������(y��ng)�S�̮a(ch��n)������ҪӰ푣��K���ѽ�(j��ng)���@Ӱ푵������a(ch��n)Ʒ�Ķ��x�����w˼��������PowerPC���ĵĵ�MPC8548̎����������ԓ��Ƭ���S���O(sh��)Ӌ(j��)����ʹ��dz��m�ϴ�h(hu��n)����

MPC8548��һ�N�߶����ϵ�̎�������ϳ����S�ཨ��(g��u)����ϵ�y(t��ng)����ľ�Ƭ���ܡ���ʹ�ð���DDR1/2��������Ͳ�����Ҫ�ⲿ��Ӿ�Ƭ��ԓ��Ƭ���ϴ���RapidIO��PCI Express��Gb��̫�W(w��ng)·ģ�M����ʽ�ڰ���������һ�����ܡ��@���H���Խ��͌��ⲿ��Ƭ������(����p�ٰ忨��(zh��n)�õĿ��g)��߀��������ʹ�Ø��/�L߅�O(sh��)�侧Ƭ�r���ܳ��F(xi��n)��ϵ�y(t��ng)ƿ�i���@Щ����ģ�M���Ѓ�(n��i)��DAM���棬ʹ��(sh��)��(j��)�o���κ���CPU�������ܿ��ق�ݔ?sh��)�������ӛ���w�С�

|

�D3������(bi��o)��(zh��n)ӍϢͨ���������O(sh��)Ӌ(j��)�� |

��(d��ng)Ȼ������Ƭֻ���O(sh��)Ӌ(j��)һ���ݡ����˼��ٮa(ch��n)Ʒ���У��͑��ձ����������Ƭ�u���̣�ϣ���@�Å����O(sh��)Ӌ(j��)���@Щ�O(sh��)Ӌ(j��)�ȿ�����һ�N��(sh��)�w�壬Ҳ������Ԕ��(x��)�Ŀɿ��O(sh��)Ӌ(j��)���͑������ڴ˻��A(ch��)���O(sh��)Ӌ(j��)�Լ��Įa(ch��n)Ʒ��

���w˼������MPC8548 AMC�������@�ׅ����O(sh��)Ӌ(j��)�ǻ��MPC8548 PowerPC̎������һ�N���A�A�ӿ�����D1��ʾ���˿��džΌ���ȫ��AMC��������AMC.4���g(sh��)Ҏ(gu��)��Ҳ�����f�������õĹ��w���B�����Ǵ���RapidIO����2����4����RapidIO���B�⣬�˿�߀�^3��Gb��̫�W(w��ng)·SERDES�����B�ӵ����塣��4��Gb��̫�W(w��ng)·�����^��(bi��o)��(zh��n)RJ45���^��ǰ����ⲿ�ṩ��

ԓ̎��������߹����l�ʞ�1.5GHz�����ȿ��ԏ��Լ��İ��dROM(16MB�Ǔ]�l(f��)�Կ��Wӛ���w)�φ��ӣ�Ҳ�������Þ�Ĵ���RapidIO�φ��ӡ���һ�N������Ҫ�����/�����á����̿��g�ɷ��ϘI(y��)���(bi��o)��(zh��n)��SODIMM(С���p��ӛ���wģ�M)�ṩ��ԓģ�M�ṩ2��1GB��DDR��ӛ���w������533MHz�����ʂ�ݔ��(sh��)��(j��)��һ��С��D���^���Ñ��ṩ��ǰ����ⲿ�Ĵ��в������뵽ATCA�C(j��)���r��ԓ�������������ϵ�y(t��ng)��һ���݈�(zh��)�У������h(yu��n)�x��(bi��o)��(zh��n)�Դ��(d��)����(zh��)�С�

�D2��ʾ������һ�NATCA����ƽ�_���@��һ�NATCA���d�忨��ԓƽ�_����܉��b�d4��AMC����3��AMC�����1������Ԓ�A�ӿ�(PTMC��Packet Telephony Mezzanine Card)��ԓ���ϵ��B�����^����RapidIO���Q�C(j��)�O(sh��)���ġ����⣬AMC��Ҳ�����^Gb��̫�W(w��ng)·�B�ӡ�

�D3�@ʾ���Ƕ���(bi��o)��(zh��n)ӍϢͨ������ԓ�����Á������_�l(f��)ӍϢͨ�������ܵ��_�l(f��)�������ϲ�ͬ���н����(bi��o)��(zh��n)�������������802.16��WCDMA��(bi��o)��(zh��n)��

�@�NӍϢͨ�����Ǹ���(j��)�p����AMC��ȫ�߶�AMC.4���g(sh��)Ҏ(gu��)���O(sh��)Ӌ(j��)����ˣ��ȿ�����춪�(d��)��ģʽ��Ҳ���Բ��뵽���ϵ�ATCA��MicroTCA�h(hu��n)���С����ӍϢͨ�����Ϳ���������_ϵ�y(t��ng)��Q������ӍϢͨ����ģ�M����(x��)�������_�Ī�(d��)��ƽ�_��

]]>����Pcb�����ļ��״μ��d�W(w��ng)�j(lu��)���ĕr�]�Ќ����M(j��n)�з���@�����ܿ����˹����o��(sh��)�ľW(w��ng)�j(lu��)�B�ӷ��T�e�����ֳ�power��data_bus��Address_bus��Hi_volta��e���@�ӷ����Էքe����ͬ��eʩ�Ӳ�ͬ�IJ�������

���ˣ��F(xi��n)���҂��Lԇһ���@�����ܣ���protel��������

�������ȴ��_һ��PCB�D���x��ˆΡ�Design-->Classes..��

�����@�����ѽ�(j��ng)�A(y��)�ȶ����ˎׂ�C�����С�AllNets����protelĬ�J(r��n)��e���@��e���������еľW(w��ng)�j(lu��)��������x�˲���Ҏ(gu��)�t��Ĭ�J(r��n)����ᘌ��@��e�ġ�

�����F(xi��n)����Ҫ���@��pcb��������һ����ʾCPU��ַ������e��Address_bus�������� ��Add�����I���ڮ�����ݔ�x��A0~A19����Ȼ���x��>�����@Щ�W(w��ng)�j(lu��)���õ���߅���Ӵ����С��@�Ӿͽ�������һ���µ�pcb�W(w��ng)�j(lu��)e����ͬ�ӵ��k�����ٽ�����power������data_bus���ȾW(w��ng)�j(lu��)e��

���ˣ��҂�?y��u)��@Щ�W(w��ng)�j(lu��)e�քeָ���������ɣ������҂�?y��u)��Դ�ָ���������ԡ����D4�����еġ�Add�����I������һ�����ԡ� ��FilterKind���x��NetClass��,��NetClass���x��POWER����Ȼ����Էքe�O(sh��)�����ľ����ȅ���(sh��)����߀���Ԟ�POWER�����һ���������Ƶ�Ҏ(gu��)�t���������@���·����4�Ӱ壬���@�����̾Ͳ��O(sh��)�ÿ���Ҏ(gu��)�t�ˣ���

�����ҵ��@���·����һ�����ٵ�Ƕ��ʽϵ�y(t��ng)��CPU�ⲿ�����l�ʴ�s200MHz�����Ե�ַ�����͔�(sh��)��(j��)�������O(sh��)Ӌ(j��)��׃�����P(gu��n)��Ҫ��ÿ����ַ�����֮�g���L�Ȳ��̫�L����t����ɂ�ݔ���t�������ֹ�ȥ�y���L�Ȳ(sh��)���韩���@��Ϳ��Ԟ��ַ�����O(sh��)��һ������Ҏ(gu��)�t��

�����ڲ���Ҏ(gu��)�t�����У��x��LengthConstraint�����������ڣ��x��ADDRESS_BUS��������O(sh��)�ÿ�������L�Ⱥ���С�L�ȡ���ʾ���ڿ��Ԟ��@��NetClass�O(sh��)�����β���Ҏ(gu��)�t��

�����O(sh��)��������Ҏ(gu��)�t�oՓ���քӲ���߀���ԄӲ������������κܶࡣ���ֹ������������·����^���У������ٿ��]�@Щ����(sh��)�ˣ���?y��n)��㷸�?gu��)��PCB���徎�����o�����档ͨ�^�@�ӵ��O(sh��)�ã���һ�ο��Ԟ�һ�����̖���O(sh��)��Ҏ(gu��)�t��������Ҫһ��һ����̖�Ϊ�(d��)�O(sh��)���ˡ����Թ�(ji��)�s�㲻�ٵĕr�g��Ҳ���Ա�����ܶԓ���ĵͼ��e�`��

]]>

�S��PCB�a(ch��n)�I(y��)��ͻ�w���M(j��n)���طNԪ�����IJ����Ƴ���������bԪ����څ��С�ͻ��Ͷ�ܻ����@�ʹ�ʹӡ���·����O(sh��)Ӌ(j��)��ӡ���·�����켼�g(sh��)��څ����ܶȡ��߿ɿ��߾��ܶȷ���l(f��)չ�����m��(y��ng)��Ӯa(ch��n)ƷС�ͻ��Ͷ�ܻ��İl(f��)չ����Ҫ������PCB����a(ch��n)ƷҲ���������͡�С�M�������ܶȡ���(x��)�g�����ٰl(f��)չ����·����Ԫ�����M�b�ܶ���ߣ�PCB����ľ������g�ࡢ���PԽ��Խ��(x��)С���ѵ�������(f��)�όӔ�(sh��)Խ��Խ�ࡣ���y(t��ng)���˹�Ŀ�y��MVI����ᘴ��ھ��yԇ��ICT���z�y���|���ޡ���늚���|����ҕ�X���|���ޣ�����,�Ѳ�����ȫ�m��(y��ng)��(d��ng)�����켼�g(sh��)�l(f��)չ����Ҫ���� PCB��ͨ�����M(j��n)�и��N�ߴ�֮�A���@�ӹ������ӹ���A�Ďγߴ缰λ�Ì�Ӱ����cIC�M������������b�õĺ��m(x��)�M�b�Ƴ̡���һ����������PCB������֮�A�ה�(sh��)�������y(t��ng)��MVI��ICT���g(sh��)�ѽ�(j��ng)�����m��(y��ng)��˿��ٵ��M(j��n)�̣����ڮa(ch��n)�ܼ�Ʒ�|(zh��)��Ҫ�O��Ҫ�߿����Ҿ��ܵęz�y���������b�ڴˣ� PCB�·���ИI(y��)�l(f��)չȫ�Ԅӹ�W(xu��)Ӱ��z�yϵ�y(t��ng)���ڱO(ji��n)ҕ�ͱ��C���a(ch��n)�^�̵�Ʒ�|(zh��)���ѽ�(j��ng)�ɞ�PCB������I(y��)�ı�Ȼ����

����1 ��W(xu��)Ӱ��z�yϵ�y(t��ng)������

������W(xu��)Ӱ��y��ϵ�y(t��ng)��F(xi��n)������C(j��)е���P(gu��n)�I���O(sh��)�䣬���V����(y��ng)���ڙC(j��)��ҕ�X��(y��ng)���I(l��ng)����z�y�����̼������Ԅӻ����I(y��)���S���߿Ƽ����I(y��)�İl(f��)չ���^ȥ�S��a(ch��n)Ʒ�z�y��ʽ���F(xi��n)����Ҫ�����Ԅӻ����ǽ��|��ʽ�M(j��n)�Йz�y����PCB�ИI(y��)��������W(xu��)Ӱ��z�yϵ�y(t��ng)�������Ǚz�yPCB�������^���еijߴ�Ҏ(gu��)�����M(j��n)���^�̿��ƣ�ͨ�^������ˇ��������p��ȱ�ݡ�ͨ���ѹ�W(xu��)Ӱ��z�yϵ�y(t��ng)�����P(gu��n)�Iλ�ã��O(ji��n)�ؾ��w���a(ch��n)��r���������a(ch��n)��ˇ���{(di��o)���ṩ��Ҫ������(j��)��

������PCB���������^���У���z�y���(xi��ng)Ŀ�����֟�Û��s�ęz�y���a(ch��n)Ʒ���^�z�y����Ԫ��λ�Ùz�y���L���߶șz�y����ֱ�șz�y����A�șz�y����ë߅�z�y�ȡ�

����2����W(xu��)Ӱ��z�yϵ�y(t��ng)��D

������W(xu��)Ӱ��z�yϵ�y(t��ng)��Ҫ�ɹ����_���(q��)�ӿ��ơ�CCD�z��ϵ�y(t��ng)��ܛ��ϵ�y(t��ng)4�ֽM�ɡ�

����3����W(xu��)Ӱ��z�yϵ�y(t��ng)�Ĺ���ԭ��

�����Ԅӹ�W(xu��)Ӱ��z�yϵ�y(t��ng)�����ĽY(ji��)��(g��u)��һ��CCD�z��ϵ�y(t��ng)�������ŷ�����x��y�����_���D��̎��ϵ�y(t��ng)���������M(j��n)�Йz�y�r�����Ȍ���Ҫ�z�y��ӡˢ��·�����ڹ�W(xu��)�y��ϵ�y(t��ng)�Ĺ����_���ϣ���(j��ng)�^��λ���{(di��o)����Ҫ�z�y�a(ch��n)Ʒ�ęz�y����x��y�����_����·���͵��R�^���棬�R�^������·��ĈD���̎����������x��y�����_������һ��λ���M(j��n)�в���Ȼ���M(j��n)������(y��ng)��Ӌ(j��)�㡣ͨ�^���D���M(j��n)���B�m(x��)̎�����@���^�ߵęz�y�ٶȡ���W(xu��)Ӱ��z�yϵ�y(t��ng)ͨ�^�����Ԅӌ�PCB�M(j��n)�гߴ�Ҏ(gu��)������ݔ����Ҫ�y���Č�(sh��)�Hֵ�c�����(j��ng)�^������̎�����Д࣬�l(f��)�F(xi��n)ȱ�ݲ��M(j��n)��λ����ʾ��ͬ�r�����ļ����ȴ��������M(j��n)һ���_�J(r��n)�������P(gu��n)���T�M(j��n)�и�����

����4����W(xu��)Ӱ��z�yϵ�y(t��ng)�Ĺ�������

������W(xu��)Ӱ��z�yϵ�y(t��ng)�������̿�D��D3��ʾ��

����5����W(xu��)Ӱ��y��ϵ�y(t��ng)��Μy���߶�

���� �ԏ�1995����F(xi��n)���Nͨ���g(sh��)�ԁ������������a(ch��n)���ϘI(y��)���_ʼ��u����CO2���⡢UV/YAG�����Լ������늽���ϵȼ��g(sh��)���@Щ�¼��g(sh��)��(d��o)���·���O(sh��)Ӌ(j��)˼��l(f��)���D(zhu��n)׃������ǰС��ʹ��0.3mmͨ���D(zhu��n)�����ʹ��ä��ͨ�ף������ڸ��ܶȑ�(y��ng)�È���(���Ƅ��Ԓ��Ӌ(j��)��C(j��)�����N�忨��IC���b)���ߌ��ȴ���8:1��ֱ��С��0.3mm�Ŀ���Խ��Խ��Ҋ���e���ڷ���(w��)�����������վ���·���ϡ���Ό��@�ͨ��Ʒ�|(zh��)�M(j��n)�п��ƣ�

��W(xu��)Ӱ��y��ϵ�y(t��ng)�y���߶ȵ�ԭ���Ǹ���(j��)���Ҳ�ͬ�߶ȃɂ���������Ľ�������������W(xu��)�ĽǶȁ��v�����^�ġ�����������һ������̓ɱ�����֮�g�ij���Ҳ�����f����ijһ���^(q��)��(n��i)�������������ģ����۷e���ɂ������Ԅӌ����r����IJ�e��Z�S�ľ��ȾͲ����cX��Y�S���ᲢՓ���@����Ҫ��һ�����ÿ��ƺͼ��g(sh��)������ܛ��ҲҪ�кܸߵļ��g(sh��)������Micro-Vu�y���x�����cIBM Microsoft��ͬ�аl(f��)֮ܛ������Դ��Ȧ�˷�����ʮ���^(q��)�K�����{(di��o)����Z�S����ͬ��Ҳ�ܿ�����5um���ң���(sh��)��������ܛ�����ܼ��ġ�

����6����W(xu��)Ӱ��y��ϵ�y(t��ng)��B

��������Micro-Vu��˾��45�����ό��I(y��)���x����S��ÿ��a(ch��n)��1500���������N���磬�����c IBM Microsoft �����аl(f��)֮ܛ���F(tu��n)�(du��)�������Ԅ����y�C(j��)�N�����ИI(y��)֮���u�������(chu��ng)�·����Լ����Ի������ڲ�ͬ����/��ͬ��Դ�¾������y��֪�������u(y��)���缰ͬ�I(y��)���Ҟ�������һ��ҕ�X���y����S��]]>

���� ��PCB����֮ǰһ����Ҫ���I(y��)����Ҫ���İ��M(j��n)���u������Ҫ������ʲô��;�������ڳ�֮ǰ��Ҫ�_�J(r��n)�Ƿ���IC��ُ�������Ƿ���IC��Ҫ���ܣ�ICĿǰ�ɷ���ܣ�һ��DSP��CPLD�ȴ�Ҏ(gu��)ģ�����·�����������y����r(ji��)���^�ߣ�߀��Ҫ�_�J(r��n)Ҫ�����Ƿ��Ǹ߾��ȵăx�����ԓ�a(ch��n)Ʒ���S����Ҫ�����{(di��o)���Įa(ch��n)Ʒ��

2����ʲô���ĵăr(ji��)���е��F�еı���?

�� �F(xi��n)�ڳ��幫˾���^�࣬�����еăr(ji��)���һ�㶼�dz��������õ�Ԫ�����]�н�����ö�����Ԫ�ط��ã��@�ӷ���Ԫ�������İ岻�����ĺ̈́�(chu��ng)���W(w��ng)�j(lu��)���M(j��n)�ж����_�l(f��)�O(sh��)Ӌ(j��)����άF(xi��n)�����S�������������壬���|(zh��)���]�б��C����r�r(ji��)��Ȍ��I(y��)���幫˾�r(ji��)����Ȼ���ͣ������@�ӳ������İ��|(zh��)���Ǜ]�б��ϵġ�

3����α��C�����ļ�100%���_?

�� һ���ڳ������п��ܳ����}�ĵط���**** PCB ��͙z�飬�҂����Լ���һ�����ƵĹ��_���DƬ�������ȡ������ļ����һϵ�Йz�鷽ʽ�������Ɍ��I(y��)���ˆT����ɵģ��@�Ӵ��_�����ļ��Ĝ�(zh��n)�_�ԣ����ļ�������ɺ��҂������ṩ�o�͑����������DƬ�ļ����@�ӿ�ʹ���幫˾����Ҳ�������д_�J(r��n)�z�顣

4��PCB ���L��ԭ��D�ܺ�ԭ���_(d��)�� 100% һ��?

���� ���L����ԭ��D������(j��) PCB �ļ��W(w��ng)�j(lu��)�����ģ������������f�ñ�y���L�Ƶģ��L������ں�ԭ PCB �ļ��ľW(w��ng)�j(lu��)�M(j��n)�бȌ��������B���P(gu��n)ϵ���Ա��C 100% һֱ��һЩ�Y�ϲ����ҵ� IC �����ܵ��҂����]�нo���������_���_���x�������� PCB ���� 1 �� 2 �� 3 �_�@�Ӂ����x����� PCB ��������(y��ng)�Ĺ��_�B���P(gu��n)ϵ�^�����_��

5��Ŀǰ���W(w��ng)�j(lu��)��������Ĺ�˾�ܶ࣬�����w��ԓ��κY�x�أ��� �@�����}�]��Ψһ�Ĵ𰸣��Ŀɿ��ԣ��ɹ��ʣ�����r(ji��)��ͳ������ڵȲ�ͬ�ĽǶȁ������Y(ji��)�����ܲ�һ�ӣ������ā��v߀�������חl������ѭ��

�����ڳ�����Ҫ�A(y��)��һ����(sh��)�~�Ķ��𣬶�Ŀǰ�ھW(w��ng)�j(lu��)�����V��ĺܶ����^ �� ��˾ �� ��(sh��)�H�σH�ǂ��˽�(j��ng)�I�����Ե�һ������һ����Ҏ(gu��)�ij��幫˾������һ��Ҫ�РI�I(y��)��(zh��)�պ�˾�_���y�Ў����ȣ��@Ҳ���A(y��)������������ı��C��

��Ҫ��PCB����ɿ��Ժͳɹ��ʶ��б��C�������ٶȿ�Č��I(y��)���幫˾���Դ_��PCB�����(xi��ng)Ŀ�܉��(zh��n)�_���r��ɣ����ǿ��]����೭�幫˾���������V�͑��ɹ��ʞ� 100% �����ԣ��͑���ֻ�܉����(j��)�����յČ��I(y��)֪�R���Єe�ˡ�

]]>

�x��pcb�����c�⚤�ӵ��c(di��n)�x���ԭ�t������ chassis ground �ṩ���迹��·���o�������(returning current)�����ƴ˻��������·�������磬ͨ���ڸ��l������r犮a(ch��n)�����������Խ�̶��õ��ݽz�� PCB����ĵ،��c chassis ground ���B�ӣ��ԱM���sС���������·��e��Ҳ�͜p��늴�ݗ�䡣

2���ڸ��� PCB �O(sh��)Ӌ(j��)�У���̖�ӵĿհׅ^(q��)����Է��~����������̖�ӵķ��~�ڽӵغͽ��Դ�ϑ�(y��ng)��η��䣿

һ���ڿհׅ^(q��)��ķ��~�^����r�ǽӵء� ֻ���ڸ�����̖���Է��~�rҪע����~�c��̖���ľ��x�� ��?y��n)�������~������һ�c(di��n)�߾��������迹�� ҲҪע�ⲻҪӰ푵����ӵ������迹�� ������ dual strip line �ĽY(ji��)��(g��u)�r��

3���ڸ��ܶ�PCB����ͨ�^ܛ���ԄӮa(ch��n)���yԇ�c(di��n)һ����r���ܝM����������a(ch��n)�ĜyԇҪ��

һ��ܛ���ԄӮa(ch��n)���yԇ�c(di��n)�Ƿ�M��yԇ�����횿����Ӝyԇ�c(di��n)��Ҏ(gu��)���Ƿ���Ϝyԇ�C(j��)�ߵ�Ҫ�����⣬����߾�̫���ҼӜyԇ�c(di��n)��Ҏ(gu��)�����^��(y��n)���t�п��ܛ]�k���Ԅӌ�ÿ�ξ������Ϝyԇ�c(di��n)����(d��ng)Ȼ����Ҫ�ք��a(b��)�R��Ҫ�yԇ�ĵط���

4�����Ӝyԇ�c(di��n)������Ӱ푸�����̖���|(zh��)����

���ڕ�����Ӱ���̖�|(zh��)����Ҫ���Ӝyԇ�c(di��n)�ķ�ʽ����̖������������������ӵĜyԇ�c(di��n)(���þ��ϼ��еĴ���(via or DIP pin)��(d��ng)�yԇ�c(di��n))���ܼ��ھ��ϻ��Ǐľ�����һС�ξ�������ǰ���ஔ(d��ng)���Ǽ���һ����С������ھ��ϣ����߄t�Ƕ���һ�η�֧���@�ɂ���r������������̖������ٕ����c(di��n)Ӱ푣�Ӱ푵ij̶Ⱦ���̖���l���ٶȺ���̖��׃����(edge rate)���P(gu��n)��Ӱ푴�С���^�����֪��ԭ�t�Ϝyԇ�c(di��n)ԽСԽ��(��(d��ng)Ȼ߀Ҫ�M��yԇ�C(j��)�ߵ�Ҫ��)��֧Խ��Խ�á�

5������ PCB ����M��ϵ�y(t��ng)��������֮�g�ĵؾ���(y��ng)����B�ӣ�

���� PCB ������B��֮�g����̖���Դ�ڄ����r������ A�������Դ����̖�͵� B ���壬һ�����е���������ĵ،����ص� A ���� (�˞� Kirchoff current law)���@�،��ϵ���������迹��С�ĵط�����ȥ�����ԣ��ڸ����������Դ����̖��B�ӵĽӿ�̎������o�،ӵĹ��_��(sh��)����̫�٣��Խ����迹���@�ӿ��Խ��͵،��ϵ��������⣬Ҳ���Է�����������h(hu��n)·������������^��IJ��֣��{(di��o)���،ӻ�ؾ��Ľӷ���������������߷�(���磬��ij̎������迹���ֵ�������@���ط���)�����͌������^������̖��Ӱ푡�

6���ܽ�BһЩ�����P(gu��n)�ڸ��� PCB �O(sh��)Ӌ(j��)�ļ��g(sh��)�������Y�φ

�F(xi��n)�ڸ��ٔ�(sh��)���·�đ�(y��ng)����ͨ�žW(w��ng)·��Ӌ(j��)��C(j��)�����P(gu��n)�I(l��ng)����ͨ�žW(w��ng)·���棬PCB ��Ĺ����l�����_(d��) GHz ���£����Ӕ�(sh��)������֪�е� 40 ��֮�ࡣӋ(j��)��C(j��)���P(gu��n)��(y��ng)��Ҳ��?y��n)�оƬ���M(j��n)�����oՓ��һ��� PC �����(w��)��(Server)�������ϵ���߹����l��Ҳ�ѽ�(j��ng)�_(d��)�� 400MHz (�� Rambus) ���ϡ���(y��ng)�@���ٸ��ܶ��߾�����ä���(blind/buried vias)��mircrovias �� build-up �Ƴ̹�ˇ������Ҳ�u�uԽ��Խ�ࡣ �@Щ�O(sh��)Ӌ(j��)�����ЏS�̿ɴ������a(ch��n)��

7���ɂ����������������迹��ʽ��

����(microstrip) Z={87/[sqrt(Er+1.41)]}ln[5.98H/(0.8W+T)] ���У�W �龀����T ���߾����~Ƥ��ȣ�H ���߾�������ƽ��ľ��x��Er �� PCB������|(zh��)�Ľ�늳���(sh��)(dielectric constant)���˹�ʽ�����0.1<(W/H)<2.0 �� 1<(Er)<15 ����r���ܑ�(y��ng)�á�

���(stripline) Z=[60/sqrt(Er)]ln{4H/[0.67��(T+0.8W)]} ���У�H ��Ʌ���ƽ��ľ��x�������߾�λ�ڃɅ���ƽ������g���˹�ʽ����� W/H<0.35 �� T/H<0.25 ����r���ܑ�(y��ng)�á�

8�������̖�����g�ɷ�ӵؾ���

�����̖���gһ���Dz��ܼӵؾ�����?y��n)�����̖�đ?y��ng)��ԭ������Ҫ��һ�c(di��n)�������ò����̖�g����(coupling)�������ĺ�̎���� flux cancellation������(noise immunity)�����ȡ��������g�ӵؾ�������Ɖ����Ч��(y��ng)��

9����?c��)��pcb�O(sh��)Ӌ(j��)�Ƿ���Ҫ�����O(sh��)Ӌ(j��)ܛ���cҎ(gu��)��������(n��i)��̎���Գн�ԓ��·��ӹ���

������һ���O(sh��)Ӌ(j��) PCB ��ܛ�����O(sh��)Ӌ(j��)�����·��(Flexible Printed Circuit)��һ���� Gerber ��ʽ�o FPC�S�����a(ch��n)����������Ĺ�ˇ��һ�� PCB ��ͬ�������S�̕�����(j��)��������������������С��������С���ࡢ��С��(via)�������ơ�����֮�⣬���������·����D(zhu��n)��̎�Щ�~Ƥ�����a(b��)��(qi��ng)���������a(ch��n)�ďS�̿��ϾW(w��ng)��FPC����(d��ng)�P(gu��n)�I�~��ԃ��(y��ng)ԓ�����ҵ���

10���·�� DEBUG ��(y��ng)���ǎׂ��������֣�

�͔�(sh��)���·���ԣ�����������_���������飺 1. �_�J(r��n)�����Դֵ�Ĵ�С���_(d��)���O(sh��)Ӌ(j��)���衣��Щ�����Դ��ϵ�y(t��ng)���ܕ�Ҫ��ijЩ�Դ֮�g����������c������ij�NҎ(gu��)���� 2. �_�J(r��n)���Еr���̖�l�ʶ�������������̖߅���ϛ]�зdž��{(di��o)(non-monotonic)�Ć��}��3. �_�J(r��n) reset ��̖�Ƿ��_(d��)��Ҏ(gu��)��Ҫ�� �@Щ��������Ԓ��оƬ��(y��ng)ԓҪ�l(f��)����һ������(cycle)����̖����������ϵ�y(t��ng)�\(y��n)��ԭ���c bus protocol �� debug�� ]]>

�҂������|(zh��)��PCB�O(sh��)Ӌ(j��)���̎������S������ż����ٶ����·��PCB�O(sh��)Ӌ(j��)��(j��ng)�(y��n)��ͨ�^�C�Ͽ��]�r��Ҫ���stripline������microstrip����̖ƥ�䷽����ͨ��̖�|(zh��)������̖�߾���?f��)�Y(ji��)��(g��u)���Դ��ȥźdecoupling��������̖����current return path��̖�迹����impedance control�ͯB��stackup���ơ��ΰ�EMC/EMI���Է�������ä��blind via and buried via�ȶ������أ�����͑��ṩ��(y��u)�|(zh��)��Ч��PCB LAYOUT������PCB�O(sh��)Ӌ(j��)��SI����������Դ�����Է���������a(ch��n)Ʒ/�ΰ�EMC�O(sh��)Ӌ(j��)�ȼ��g(sh��)����(w��)��

��ֻ���ṩ������ԭ��D��Ҏ(gu��)���Y�ϣ������Ԫ�������x�����b��������PCB���O(sh��)Ӌ(j��)�Լ��ư��NƬ���҂��ṩһվʽ��Q���������������ֻ�Юa(ch��n)Ʒ�O(sh��)Ӌ(j��)��˼·��߀�]��ԭ��D�ȼ��g(sh��)�Y�ϣ��҂��ɞ����ṩԭ��D�O(sh��)Ӌ(j��)���Y(ji��)��(g��u)�����O(sh��)Ӌ(j��)�������x�͵�PCB�O(sh��)Ӌ(j��)�Ŀ��w�O(sh��)Ӌ(j��)�������ӿ����Įa(ch��n)Ʒ�аl(f��)���Ƅ��®a(ch��n)Ʒ�������У���ְ����Ј��C(j��)���A�ø���(j��ng)��(j��)Ч�档

PCB�O(sh��)Ӌ(j��)������

����O(sh��)Ӌ(j��)�Ӕ�(sh��)���������PIN��(sh��)Ŀ��48963 ���Connections��36215 ��С�^�ף�8MIL(4MIL�����) ��С������3MIL ��С���g�ࣺ4MIL һ�KPCB�����BGA��(sh��)Ŀ��44 ��СBGA PIN�g�ࣺ0.5mm �������̖��10G CML�����̖��콻�ڣ�2�fPIN�ΰ�PCBǰ���桢���֡�������������Ӌ(j��)6�졣

��̖��ͣ�

оƬ��Xilinx��ViVex2��VirxtexPro��Inter2800��Altera��VIA AMD��TI..... ��̖��DDR/DDR2��USB��Ether��iLink��LVDS��PCI/PCI Express��HDMI��SATA��RAMBUS.....

PCB�O(sh��)Ӌ(j��)���̈D��

PCB��������X���峭�壬�֙C(j��)������F(xi��n)PCܛ�Գ��壬�X���峭��

�҂�����pcb��¡���İ塢ԭ��D��BOM��������pcb���a(ch��n)���әC(j��)�����{(di��o)ԇ��С������Ʒ�ӹ�һ�l������(w��)���¼��g(sh��)�߿Ƽ���I(y��)��������(j��)�͑��ṩ�ĺ����Ԫ�������Ӱ�����ԓ�a(ch��n)Ʒ��ԭ��D���ɈD���x�Կ��c�O(sh��)Ӌ(j��)ԭ�D���������ڕr�g��,��(zh��n)�_�ȿ��_(d��)100��һ�γɹ�����ּ���\�ŵ�һ,����(w��)һ�����\���ǹ�˾һ؞�đB(t��i)�ȡ��Ñ��M��t�ǹ�˾һֱ���Ŀ��(bi��o)��

]]>����ORCAD����ORCAD��˾��20���o(j��)80���ĩ�Ƴ���EDAܛ��������������ʹ����V��EDAܛ����ÿ�춼���ϰ��f���·���̎���ʹ����������������EDAܛ�����ԣ����Ĺ���Ҳ���(qi��ng)��ģ�����ORCADܛ��ʹ����ܛ�������I�棬����ڇ���(n��i)�������ռ���֪����Ҳ�Ȳ���PROTEL��ֻ���ٔ�(sh��)���·�O(sh��)Ӌ(j��)��ʹ���������ڹ�����DOS�h(hu��n)����ORCAD 4.0�����ͼ������ԭ��D�L�ơ�ӡ���·���O(sh��)Ӌ(j��)����(sh��)���·���桢�ɾ���߉�����O(sh��)Ӌ(j��)�ȹ��ܣ��������Ľ����Ѻ���ֱ�^������Ԫ������Ҳ������EDAܛ�������S���ģ�����������һֱ��EADܛ���е����x��ORCAD��˾��ȥ��7���cCADENCE��˾�ϲ����ɞ��������(qi��ng)����_�l(f��)EDAܛ���Ĺ�˾�����Įa(ch��n)ƷORCAD���o(j��)���ɰ湤����Windows 95�cWindows NT�h(hu��n)���£��������ԭ��D�L�ƣ�ӡˢ�·���O(sh��)Ӌ(j��)��ģ�M�c��(sh��)���·��Ϸ���ȹ��ܡ������·�����Ԫ��������_(d��)����8500���������ˎ����е�ͨ�����·Ԫ����ģ�K�����ď�(qi��ng)���܌�(d��o)���������ۃr(ji��)���ƣ��ڱ����^(q��)�������o(j��)�ӏ�(qi��ng)����u����7995��Ԫ����ORCAD���dȤ���x�߿���ȥ�L������վ�c(di��n)��HTTP:����WWW.ORCAD.COM��HTTP:����WWW.CADENCE.COM��HTTP:����PCB.CADENCE.COM��

PROTEL �·�Ԅ��O(sh��)Ӌ(j��)

����PROTEL��PORTEL��˾��20���o(j��)80���ĩ�Ƴ����·�ИI(y��)��CADܛ��������(d��ng)֮�o�������ڱ���EDAܛ����ǰ�棬���·�O(sh��)Ӌ(j��)�ߵ����xܛ�������^���ڇ���(n��i)ʹ�ã��ռ���Ҳ��ߣ���Щ��У���·���I(y��)߀���T�_�O(sh��)���n�́�W(xu��)��(x��)���������е��·��˾��Ҫ�õ��������ڵ�PROTEL��Ҫ����ӡˢ���ԄӲ�������ʹ�ã��\(y��n)����DOS�h(hu��n)������Ӳ����Ҫ��ܵͣ��ڟoӲ�P286�C(j��)��1M��(n��i)���¾����\(y��n)�С����Ĺ����^�٣�ֻ���ԭ��D�L���cӡˢ���O(sh��)Ӌ(j��)���ܣ�ӡˢ���ԄӲ����IJ�ͨ��Ҳ�͡��F(xi��n)�ڵ�PROTEL�Ѱl(f��)չ��PROTEL99���W(w��ng)�j(lu��)�Ͽ����d�����Ĝyԇ�棩���ǂ������EDAܛ������ȫ���b��200��MB����������Windows 95�h(hu��n)���£��ǂ�������ȫ��λ�·�O(sh��)Ӌ(j��)ϵ�y(t��ng)�����������ԭ��D�L�ơ�ģ�M�·�c��(sh��)���·�����̖���桢����ӡˢ�·���O(sh��)Ӌ(j��)������ӡˢ�·���ԄӲ��������ɾ���߉�����O(sh��)Ӌ(j��)���D�����ɡ��·�������ɡ�֧�ֺ�����ȹ��ܣ�������Client/Server ���͑�/����(w��)�����wϵ�Y(ji��)��(g��u)��ͬ�r߀����һЩ�����O(sh��)Ӌ(j��)ܛ�����ļ���ʽ����ORCAD��PSPICE��EXCEL�ȡ�ʹ�ö���ӡ�ƾ�·����ԄӲ������Ɍ�(sh��)�F(xi��n)���ܶ�PCB��100����ͨ�ʡ��������˽�PROTEL��ܛ�����ܻ������dPROTEL99��ԇ�ð棬������Internet���L������վ�c(di��n)��HTTP:����WWW.PROTEL.COM��

Protel for Windows v1.0 sch �·ԭ��D�Ԅ��O(sh��)Ӌ(j��)

�����汾�m�ͣ����ǹ���(qi��ng)������ϵ�y(t��ng)��Ӳ��Ҫ���^�ͣ� 486�����ϙC(j��)�ͼ��ɣ����b���ļ��^С�s 14.2MB�������L�Ƶ� *.sch ��ʽ�D���ļ��eС���c�����O(sh��)Ӌ(j��)ܛ�������ԘO�ã���һ���y�õă�(y��u)��ܛ����

Protel for Windows v1.5 pcb ӡˢ�·���Ԅ��O(sh��)Ӌ(j��)

�����汾�m�ͣ����ǹ���(qi��ng)������ϵ�y(t��ng)��Ӳ��Ҫ���^�ͣ�486�����ϙC(j��)�ͼ��ɣ����b���ļ��^С�s 4.65MB�������L�Ƶ� *.pcb��ʽ�D���ļ��eС���c�����O(sh��)Ӌ(j��)ܛ�������ԘO�ã�����֧�������ַ���ݔ�룬���ҵ���ͨ��PCB����ֻ��Ӣ���ַ���������֮��Protel for Windows v1.5��һ���y�õă�(y��u)��ܛ����

PSPICE �·����

����PSPICE���^����F(xi��n)��EDAܛ��֮һ��1985�����MICROSIM��˾�Ƴ������·���淽�棬���Ĺ��ܿ����f����鏊(qi��ng)���ڇ���(n��i)���ձ�ʹ�á��F(xi��n)��ʹ���^�����PSPICE 6.2��������Windows�h(hu��n)����ռ��Ӳ�P���g20��M������ܛ����ԭ��D�����·���桢�����Ԫ�����쾎�����ΈD�Ȏׂ����ֽM�ɣ�ʹ�Õr��һ�����w�����������ָ��и��Ĵ��ڡ�PSPICE�l(f��)չ�����ѱ�����ORCAD���ɞ�ORCAD��PSPICE����PSPICE��Ȼ�Ϊ�(d��)�N�ۺ�ʹ�ã����Ƴ��İ汾��PSPICE 9.1��������Windows 9x��NTƽ�_�ϣ�Ҫ���DZ��v����CPU��32M��(n��i)�桢50M����ʣ��Ӳ�P���g��800��600�����@ʾ�ֱ��ʣ��ǹ���(qi��ng)���ģ�M�·�͔�(sh��)���·��Ϸ���EDAܛ�����������M(j��n)�и��N���ӵ��·���桢��������ض��c��������ģ�M���ơ�����ݔ������(sh��)��(j��)ݔ��������ͬһ�����ڃ�(n��i)ͬ�r�@ʾģ�M�c��(sh��)�ֵķ���Y(ji��)�����oՓ���ķN������Щ�·�M(j��n)�з��棬����IGBT���}���{(di��o)���·��ģ����(sh��)�D(zhu��n)�Q����(sh��)��ģ�D(zhu��n)�Q�ȣ������Եõ����_�ķ���Y(ji��)�������ڎ��Л]�е�Ԫ����ģ�K��߀�������Ѿ�������INTERNET�ϵľW(w��ng)ַ�cORCAD��˾һ�ӡ�

EWB �·����

��EWB(ELECTRONICS WORKBENCH EDA)ܛ���ǽ����D���g(sh��)����˾��INTERACTIVE IMAGE TECHNOLOGIES Ltd����20���o(j��)90������Ƴ���EDAܛ�������ڇ���(n��i)�_ʼʹ�Ås�ǽ�������¡��F(xi��n)���ձ�ʹ�õ�����Windows 95�h(hu��n)���¹�����EWB 5.0����������EDAܛ�����ԣ����ǂ��^С�ɵ�ܛ����ֻ��16M������Ҳ���^��һ�������M(j��n)��ģ�M�·�͔�(sh��)���·�Ļ�Ϸ��棬����^������С���������ķ��湦��ʮ�֏�(qi��ng)��100���ط�����挍(sh��)�·�ĽY(ji��)�������������������ṩ���f�ñ���ʾ��������̖�l(f��)���������l�x��߉�����x����(sh��)����̖�l(f��)������߉�D(zhu��n)�Q���ȹ��ߣ������������Єt�������S���˾�ľ��w��Ԫ�����������·�͔�(sh��)���T�·оƬ���������Л]�е�Ԫ������߀�������ⲿģ�K��(d��o)�롣�ڱ�����·����ܛ���У�EWB�����������ֵģ����Ĺ�������dz�ֱ�^��ԭ��D���N���߶���ͬһ�����ڃ�(n��i)��δ���|�^�������ԼӌW(xu��)��(x��)�Ϳ��Ժ��쾚��ʹ��ԓܛ���������·�O(sh��)Ӌ(j��)�����߁��f�����ǂ��O�õ�EDA���ߣ��S���·��o횄������F�Ϳɵ�֪���ĽY(ji��)��������������QԪ�������׃Ԫ��������(sh��)��ֻ��c(di��n)�c(di��n)���(bi��o)���ɣ���Ҳ��������늌W(xu��)֪�R���o���̌W(xu��)ܛ��ʹ�ã�����������ֱ�ӏ���Ļ�Ͽ������N�·��ݔ�����Ρ�EWB�ļ�����Ҳ�^�ã����ļ���ʽ���Ԍ�(d��o)�����ܱ�ORCAD��PROTEL�xȡ�ĸ�ʽ��ԓܛ��ֻ��Ӣ�İ棬�����İ��Windows 98������һЩ�D��(bi��o)��ƫ�ƃɂ�λ�ã���Windows 95��������������Ӱ�����ʹ�ã����ǹP����ϲ�g��EDAܛ��֮һ��

]]>�����҂��Ĺ��̎����@������䡱�����p��ʹ�ã�Ҳ�S����?y��n)���PCB �{(di��o)ԇ�У�����(j��ng)���^�����^����Ҳ�����nj��҂�һֱ�]�нo�����_�ĽY(ji��)Փ��

�������~�ǡ������ڱס�߀�ǡ��״��������������Ì�(sh��)�y�ĽǶȁ��f���@�����}��

����Ĝy���Y(ji��)��������EMSCAN 늴Ÿɔ_����ϵ�y(t��ng) (http://www.emscan.com.cn )�@�õģ�EMSCAN ��ʹ�҂���(sh��)�r����늴ň��ķֲ���������1280 ������̽�^����������ГQ���g(sh��)�����ْ���PCB �a(ch��n)����늴ň�����������Ψһ��������쾀����Ӓ��輼�g(sh��)��늴ň���������ϵ�y(t��ng)��Ҳ��Ψһ�ܫ@�ñ��y������늴ň���Ϣ��ϵ�y(t��ng)��

�ȿ�һ����(sh��)�y�İ�������һ�K����PCB �ϣ����̎���PCB ���܇�������һȦ�~����D1 ��ʾ�����@�����~��̎���ϣ����̎��H���~Ƥ���_ʼ���ַ����ˎׂ��^�ף����@��

�~Ƥ�B�ӵ��˵،��ϣ������ط�?j��ng)]�д��^�ס�

�D1 PCB �����ӵصķ��~�a(ch��n)����늴ň�

�ڸ��l��r�£�ӡˢ�·���ϵIJ����ķֲ���ݕ������ã���(d��ng)�L�ȴ������l������(y��ng)���L��1/20 �r���͕��a(ch��n)���쾀Ч��(y��ng)�����͕�ͨ�^��������l(f��)�䡣

����ϵ�y(t��ng)�Ƽ�����˾ EMSCAN ����Ӯa(ch��n)Ʒ�O(sh��)Ӌ(j��)�еđ�(y��ng)�á���PCB ���~���}

- 2 -

�������@����(sh��)�H�y���ĽY(ji��)��������PCB �ϴ���һ��22.894MHz �ĸɔ_Դ�������O(sh��)���~Ƥ���@����̖�����У����顰�����쾀�����յ����@����̖��ͬ�r��ԓ�~Ƥ�����顰�l(f��)���쾀�����ⲿ�l(f��)���(qi��ng)��늴Ÿɔ_��̖���҂�֪�����l���c���L���P(gu��n)ϵ��f�� C/�ˡ�ʽ��f ���l�ʣ���λ��Hz���˞鲨�L����λ��m��C ����٣�����3��108 ��/�댦��22.894MHz ����̖���䲨�L�˞飺3��108/22.894M=13 �ס���/20 ��65cm��

��PCB �ķ��~̫�L�����^��65cm���Ķ���(d��o)�®a(ch��n)���쾀Ч��(y��ng)��

Ŀǰ���҂���PCB �У��ձ������������С��1ns ��оƬ�����O(sh��)оƬ��������

��1ns����a(ch��n)����늴Ÿɔ_���l�ʕ����_(d��)fknee = 0.5/Tr ��500MHz������500MHz ��

��̖���䲨�L��60cm����/20=3cm��Ҳ�����f��PCB ��3cm �L�IJ������Ϳ����γɡ��쾀����

���ԣ��ڸ��l�·�У�ǧ�f��Ҫ�J(r��n)�飬�ѵؾ���ij���ط����˵أ��@���ǡ���

������һ��Ҫ��С�ڦ�/20 ���g�࣬�ڲ����ϴ��^�ף��c���Ӱ�ĵ�ƽ�桰���ýӵء���

����һ��Ĕ�(sh��)���·����1cm ��2cm ���g�࣬��Ԫ������ߺ�����ġ�����䡱

���^�ף���(sh��)�F(xi��n)�c��ƽ������ýӵأ����ܱ��C������䡱�����a(ch��n)�����ס���Ӱ푡�

�ɴˣ��҂��M(j��n)���������죺

? ���Ӱ����g�ӵIJ����Օ�^(q��)��Ҫ���~����?y��n)�����y�����@�����~����

�ýӵء�

? һ�KPCB�������ж��ٷN�Դ�����h�����Դ�ָ�g(sh��)������ֻʹ��һ���

Դ�ӡ���?y��n)��Դ�c��һ�ӣ�Ҳ�ǡ�����ƽ�桱���Դ�c�صġ����ýӵء���

ͨ�^�����ĞV�����(sh��)�F(xi��n)�ģ��]�ОV����ݵĵط����͛]�С��ӵء���

? �O(sh��)���(n��i)���Ľ��٣��������ɢ���������ټӹ̗l�ȣ�һ��Ҫ��(sh��)�F(xi��n)�����ý�

�ء���

? ���˷�(w��n)������ɢ����ىK��һ��Ҫ���ýӵء�

? �����Ľӵظ��x����һ��Ҫ���ýӵء�

�Y(ji��)Փ��PCB �ϵķ��~������ӵ؆��}̎�����ˣ��϶��ǡ������ڱס������ܜp��

��̖���Ļ�����e���pС��̖�����늴Ÿɔ_

]]>2���^��(Via��

���Bͨ����֮�g�ľ�·���ڸ�����Ҫ�Bͨ�Č�(d��o)�����ąR̎�@��һ�������ף��@�����^�ס���ˇ�����^�ĿױڈA�������û��W(xu��)���e�ķ������һ�ӽ��٣������Bͨ���g������Ҫ�Bͨ���~�������^��������������ͨ�ĺ��P�Π��ֱ���c������ľ�·��ͨ��Ҳ�ɲ��B��һ����ԣ��O(sh��)Ӌ(j��)��·�r���^��̎��������ԭ�t��

��1���M�������^�ף�һ���x�����^�ף���(w��)��̎�������c��߅����(sh��)�w���g϶���e�����ױ���ҕ�����g�����c�^�ײ����B�ľ��c�^���g϶��������ԄӲ��������ڡ��^�ה�(sh��)����С���� �� Via Minimiz8tion���Ӳˆ����x��on���(xi��ng)���Ԅӽ�Q��

��2����Ҫ���d����Խ��������^�׳ߴ�Խ�����Դ�Ӻ͵،��c������(li��n)�����õ��^��Ҫ��һЩ��

3���zӡ�ӣ�Overlay��

�鷽���·�İ��b�;S�ȣ���ӡˢ������ɱ���ӡˢ������Ҫ�Ę�(bi��o)־�D�������ִ�̖�ȣ�����Ԫ����(bi��o)̖�͘�(bi��o)�Qֵ��Ԫ�������Π�͏S�Ҙ�(bi��o)־�����a(ch��n)���ڵȵȡ����ٳ��W(xu��)���O(sh��)Ӌ(j��)�zӡ�ӵ����P(gu��n)��(n��i)�ݕr��ֻע�����ַ�̖���õ����R���^�������ˌ�(sh��)�H�Ƴ���PCBЧ���������O(sh��)Ӌ(j��)��ӡ���ϣ��ַ����DZ�Ԫ����ס���������������^(q��)��Ĩ�d��߀�еİ�Ԫ����(bi��o)̖��������Ԫ���ϣ���˷N�N���O(sh��)Ӌ(j��)�������o�b��;S�ގ����ܴ㡣���_�Ľzӡ���ַ�����ԭ�t�ǣ����������x��Ҋ�p��ᘣ����^����

4��SMD��������

Protel���b���(n��i)�д���SMD���b�������溸�b�������@��������w�eС��֮���������c(di��n)�dž���ֲ�Ԫ���_�ס���ˣ��x���@�����Ҫ���x�����������棬���⡰�Gʧ���_��Missing Plns���������⣬�@�Ԫ�������P(gu��n)���֘�(bi��o)עֻ���SԪ����������á�

5���W(w��ng)������^(q��)��External Plane �������^(q��)(Fill)

������ߵ������ǘӣ��W(w��ng)�j(lu��)�����^(q��)�ǰѴ���e���~��̎���ɾW(w��ng)��ģ����^(q��)�H�����������~�������W(xu��)���O(sh��)Ӌ(j��)�^������Ӌ(j��)��C(j��)���������������ߵą^(q��)�e����(sh��)�|(zh��)�ϣ�ֻҪ��шD��� ����һĿ��Ȼ�ˡ���������ƽ�������������ߵą^(q��)�e������ʹ�Õr����ע�⌦���ߵą^(q��)�֣�Ҫ��(qi��ng)�{(di��o)���ǣ�ǰ�����·���������^��(qi��ng)�����Ƹ��l�ɔ_�����ã��m������������e���ĵط����e�ǰ�ijЩ�^(q��)��(d��ng)�����΅^(q��)���ָ�^(q��)���������Դ���r�Ȟ���m�����߶�����һ��ľ��˲����D(zhu��n)�ۅ^(q��)����ҪС��e���ĵط���

6�����P( Pad��

���P��PCB�O(sh��)Ӌ(j��)������|Ҳ������Ҫ�ĸ�������W(xu��)�߅s����ҕ�����x������������O(sh��)Ӌ(j��)��ǧƪһ�ɵ�ʹ�ÈA�κ��P���x��Ԫ���ĺ��P���Ҫ�C�Ͽ��]ԓԪ�����Π��С��������ʽ����Ӻ��ܟ���r��������������ء�Protel�ڷ��b���нo����һϵ�в�ͬ��С���Π�ĺ��P����A�������˽ǡ��A���Ͷ�λ�ú��P�ȣ����Еr�@߀�����ã���Ҫ�Լ��������磬���l(f��)���������^������^��ĺ��P���������O(sh��)Ӌ(j��)�ɡ��I�Π���ڴ����Ϥ�IJ��PCB����ݔ��׃�������_���P���O(sh��)Ӌ(j��)�У����ُS�����Dz��õ��@�N��ʽ��һ����ԣ����о����P�r�����������v�����⣬߀Ҫ���]����ԭ�t��

��1���Π����L�̲�һ�rҪ���]�B�������c���P�ض�߅�L�Ĵ�С������^��

��2����Ҫ��Ԫ������֮�g�߾��r�x���L�̲����Q�ĺ��P�����°빦����

��3����Ԫ�����P�Ĵ�СҪ��Ԫ�����_�ּ�(x��)�քe���_����ԭ�t�ǿijߴ�����_ֱ����0��2- 0��4���ס�

7�����Ĥ��Mask)

�@ЩĤ���H��PcB������ˇ�^���бز����ٵģ����Ҹ���Ԫ�����b�ı�Ҫ�l��������Ĥ����̎��λ�ü������ã���Ĥ���ɷ֞�Ԫ���棨���棩����Ĥ��Top or Bottom ��Ԫ���棨���棩�躸Ĥ��Top or BottomPaste Mask����� ���˼�x������Ĥ��Ϳ�ں��P�ϣ���߿ɺ����ܵ�һ��Ĥ��Ҳ�����ھGɫ�����ϱȺ��P�Դ�ĸ��\ɫ�A�ߡ��躸Ĥ����r�����෴������ʹ�Ƴɵİ����m��(y��ng)���庸�Ⱥ�����ʽ��Ҫ������ϷǺ��P̎���~������ճ�a������ں��P����ĸ���λ��ҪͿ��һ��Ϳ�ϣ�������ֹ�@Щ��λ���a����Ҋ���@�ɷNĤ��һ�N���a(b��)�P(gu��n)ϵ���ɴ�ӑՓ���Ͳ��y�_���ˆ�����ơ�solder Mask En1argement�����(xi��ng)Ŀ���O(sh��)���ˡ�

8���w�����w���Ѓ��غ��x��

��1���ԄӲ����r���^���õ������Ƥ��ľW(w��ng)�j(lu��)�B������ͨ�^�W(w��ng)�j(lu��)���{(di��o)��Ԫ�������˳������ֺ��á�Show ����Ϳ��Կ���ԓ�����µľW(w��ng)�j(lu��)�B���Ľ����r�������{(di��o)��Ԫ����λ��ʹ�@�N�������٣��ԫ@�������ԄӲ����IJ�ͨ�ʡ��@һ������Ҫ�������f��ĥ�����`�����Щ�r�g��ֵ�����⣬�ԄӲ����Y(ji��)����߀����Щ�W(w��ng)�j(lu��)��δ��ͨ��Ҳ��ͨ�^ԓ���܁����ҡ��ҳ�δ��ͨ�W(w��ng)�j(lu��)֮�����ֹ��a(b��)������(sh��)���a(b��)�����˾�Ҫ�õ����w�����ĵڶ��Ӻ��x�������ڌ�����ӡ�����Ì�(d��o)���Bͨ�@Щ�W(w��ng)�j(lu��)��Ҫ�������ǣ����ԓ�·���Ǵ������ԄӾ����a(ch��n)���Ɍ��@�N�w��ҕ��0�W��ֵ�����нy(t��ng)һ���P�g������Ԫ�����M(j��n)���O(sh��)Ӌ(j��).

���ʿƼ����I(y��)��·�峭�塢PCB LAYOUT��PCB�İ壬BOM������� ��PCB����ԭ��D��PCB���a(ch��n)��SMT�ӹ����әC(j��)���� ���{(di��o)ԇ����Ʒ���a(ch��n)�� �O(sh��)Ӌ(j��)�_�l(f��)һ�γɹ���]]>

1 ����һ��ҪС��֔(j��n)��������Ҫ�ľ��Dz��֡�

2 �������R�ÿ���Ҳ���^���ײ�����

3 �Դ�Ӳ����RJ45�ȿ���������߅�磬�������⚤�ĕr��

���b��

4 ���ڶ����_��늵�IC,���ÿ���Դ���_����ȥź��ݡ�����

�Դ�����^�ֵĿ�������ȥź��ݡ�

5 ע���ԴоƬ�l(f��)����^���ض����е�����Ҫ�h(yu��n)�x��

6 �����Ȳ��Դ�����ؾ����

7 ����Ҏ(gu��)�t������ڲ���ǰ��ã��O(sh��)����,���_ʼ����t�����ˡ�

8 �������治Ҫ����̖�������Բ��ؾ���

9 Ĭ�J(r��n)���^����ֱ��50mil,��(n��i)ֱ��28mil���^��һ���x��20mil

��(n��i)ֱ����pcb�S��һ���������С���^�׃�(n��i)ֱ��10mil(����ԃ��һ��pcb�S�ҵ��ˣ���

10 һ�����a(ch��n)Ʒ�����x���⚤��Ȼ����pcb��á�

11 ���Ȳ��Դ������ò��ɰ�h(hu��n)�Σ������Դ��������̖�߾������⣬�Դ���M��������

ͬһ���棬����top layer�� ��ʹ��2�N�����Դ��

12 ����̖���Ȳ��������ǷN���ܵIJ�����

13 �����������������ˣ���ؾ���Ȼ����~��һ����~���x��GND,�����~䁲�����

���ԷŎׂ��W(w��ng)�j(lu��)��GND���^�ס�һ�㲻Ҫ���~�����䁾W(w��ng)�����m��(d��ng)�x��W(w��ng)�ȺͲ���

���ȡ����䁌�(sh��)���~�����ԾW(w��ng)�ȵ��ڲ������ȵ�2����

14 ��(d��ng)�������ж������ˣ����a(b��)�I�Σ���?y��n)��a(b��)�˜I����pcb���韩��������(n��i)PCB�ИI(y��)����Ҳ���ž�����2009�����������ɞ齛(j��ng)�I�I(y��)���D(zhu��n)���ڡ������҇�����ИI(y��)��PCB�ИI(y��)Խ��Խ�@�����_������������݆��(j��ng)��(j��)���������Ї���(n��i)PCB�ИI(y��)����Ҳ�����@�½������҂��J(r��n)���݆�ИI(y��)���{(di��o)��������2009�����ڽY(ji��)�����@�ǻ����҂��A(y��)Ӌ(j��)ȫ��(j��ng)��(j��)����2009���°�����(f��)�K��ǰ�ᡣ��?y��n)���^��(j��ng)��(j��)�΄ݵĺ��D(zhu��n)��������I(y��)�����ĺ����M(f��i)�����ģ�PCB�ИI(y��)�����������������L�������¾������С��҂����h�P(gu��n)ע����PCBӆ�γ�؛�ȡ������댧(d��o)�w�O(sh��)��ӆ�γ�؛�ȡ��������M(f��i)������ָ��(sh��)������ָ��(bi��o)��ۙ�ИI(y��)��ů�ĕr�c(di��n)��

�� �����ИI(y��)��������څ���y�Ը�׃���҂��o���ИI(y��)�����ԡ���Ͷ�Y�u���������b��Ŀǰ�ИI(y��)��(n��i)���й�˾�^�͵Ĺ�ֵˮƽ���҂�?n��i)ԃA���ڲ�ȡ���¶��ϵķ������ھ��ИI(y��)��(n��i)���й�˾��Ͷ�Y�C(j��)�����҂����hץס�ɂ����c(di��n)��(1)�����ڇ���(n��i)3G�W(w��ng)�j(lu��)���O(sh��)Ͷ�Y�ļ��٣�(2)�a(ch��n)Ʒ������(sh��)�F(xi��n)�M(j��n)�����

]]>���S������������ӄ����S�����R�Įa(ch��n)Ʒ�����r�g�ĉ���ҲԽ��Խ������������M(j��n)��EDA�����Լ��(y��u)���ķ��������̣����|(zh��)������Ч�ʵ�����O(sh��)Ӌ(j��)���ѽ�(j��ng)�ɞ�ϵ�y(t��ng)�S�̺��O(sh��)Ӌ(j��)���̎����ò��挦�Ć��}��

���c(di��n)������̖���������Դ�������D(zhu��n)��

Մ�������O(sh��)Ӌ(j��)���˂������뵽�ľ�����̖�����Ԇ��}����̖��������Ҫ��ָ��̖����̖���ς�ݔ?sh��)��|(zh��)������(d��ng)�·����̖����Ҫ��ĕr���m(x��)�r�g��늉����ȵ��_(d��)����оƬ���_�r��ԓ�·���кܺõ���̖�����ԡ���(d��ng)��̖��������푑�(y��ng)������̖�|(zh��)������ʹϵ�y(t��ng)�L�ڷ�(w��n)�������r���ͳ��F(xi��n)����̖�����Ԇ��}����̖��������Ҫ���F(xi��n)�����t�����䡢��?d��ng)_���r����ʎ�Ȏׂ����档һ���J(r��n)�飬��(d��ng)ϵ�y(t��ng)������50MHz�r���͕��a(ch��n)����̖�����Ԇ��}�����S��ϵ�y(t��ng)�������l�ʵIJ�����������̖�����ԵĆ��}Ҳ�����l(f��)ͻ����Ԫ������PCB��ą���(sh��)��Ԫ������PCB���ϵIJ��֡�������̖�IJ������@Щ���}����������̖�����Ԇ��}����(d��o)��ϵ�y(t��ng)��������(w��n)����������ȫ��������������

��̖�����Լ��g(sh��)��(j��ng)�^��ʮ��İl(f��)չ������Փ�ͷ����������ѽ�(j��ng)�^����졣������̖�����Ԇ��}����m���J(r��n)�飬��̖�����Բ���ij���˵Ć��}�����漰���O(sh��)Ӌ(j��)朵�ÿһ���h(hu��n)��(ji��)������ϵ�y(t��ng)�O(sh��)Ӌ(j��)���̎���Ӳ�����̎���PCB���̎�Ҫ���]������������rҲ���ܺ�ҕ����Q��̖�����Ԇ��}����횽������M(j��n)�ķ��湤�ߣ���Cadence��SPECCTRAQuest���Dz��e�ķ��湤�ߣ��������������O(sh��)Ӌ(j��)ǰ���M(j��n)�н�ģ�����棬�Ķ��γɼs��Ҏ(gu��)�tָ��(d��o)���ڵIJ��ֲ���������O(sh��)Ӌ(j��)Ч�ʡ��S��Cadence �ڽ���6���Ƴ��Č��Tᘌ�ǧ����̖�ķ�����MGH�������ǘI(y��)���ׂ������ڎ���֮��(n��i)��ɔ�(sh��)�fBITǧ����̖�ķ�����������̖�����Լ��g(sh��)�������ơ�

��������̖�����ԣ��Դ��������һ�N�^�µļ��g(sh��)�������J(r��n)���Ǹ��ٸ��ܶ�PCB�O(sh��)Ӌ(j��)Ŀǰ��������(zh��n)֮һ���Դ��������ָ�ڸ���ϵ�y(t��ng)�У��Դ��ݔϵ�y(t��ng)��PDS power deliver system���ڲ�ͬ�l���ϣ��迹���Բ�ͬ��ʹPCB�����Դ���c�،��g��늉����·��ĸ�̎���M��ͬ���Ķ���ɹ�늲��B�m(x��)���a(ch��n)���Դ����ʹоƬ��������������ͬ�r���ڸ��lݗ�䣬�Դ�����Ԇ��}߀������EMC/EMI���}��������ܺܺõؽ�Q�Դ�����Ԇ��}������(y��n)��Ӱ�ϵ�y(t��ng)������������

ͨ�����Դ�����Ԇ��}��Ҫͨ�^�ɂ�;������Q����(y��u)���·��įB���O(sh��)Ӌ(j��)�����ֲ������Լ�����������ݡ����������ϵ�y(t��ng)�l��С��300 ~ 400MHz�r����������ֹ�l�ʡ��V�����迹���Ƶ����ã���ǡ��(d��ng)?sh��)�λ�÷��ú��m��������������ڜpСϵ�y(t��ng)�Դ�����ԵĆ��}�����Ǯ�(d��ng)ϵ�y(t��ng)�l�ʸ��ߕr��������ݵ����ú�С�����@�N��r�£�ֻ��ͨ�^��(y��u)���·��Č��g���O(sh��)Ӌ(j��)�Լ����ֲ������������Ľ����Դ�������ķ��������m��(d��ng)ƥ�併���Դ��ݔϵ�y(t��ng)�ķ��䆖�}���ȁ���Q�Դ�����Ԇ��}��ͬ�r��ֹEMC/EMI��

������̖�����Ժ��Դ������֮�g���P(gu��n)ϵ����m���J(r��n)�飺����̖�������Ǖr��ĸ�����^�����⣬���Դ�����ԅs���l��ĸ���y�ȱ���̖�����Դ���ijЩ�������̖������������֮ͨ̎���Դ�����Ԍ����̎��ļ���Ҫ����ߣ����ڸ����O(sh��)Ӌ(j��)���ԣ���һ���µ�����(zh��n)���������漰���弉��ͬ�r�漰��оƬ�ͷ��b�������h���¸����·���O(sh��)Ӌ(j��)�Ĺ��̎��ڽ�Q����̖�����ԵĻ��A(ch��)�������Դ�����ԡ�����(j��)��B��Cadence���Դ�����Թ���PI�������Ј������ѳɹ��\(y��n)�õ��ܶ�͑����O(sh��)Ӌ(j��)�С�

��

ͨ�^���� ��ܛ��������O(sh��)Ӌ(j��)

�����nj��Ѹ����憖�}�����]�M(j��n)ȥ��̓�Mԭ�͵Ĝyԇ�������O(sh��)Ӌ(j��)Խ��Խ��(f��)�s�����̎������ܰ�ÿһ�N�������Á팍(sh��)ʩ���˕rֻ�ܽ������M(j��n)�ķ������ԇ�(y��n)�M(j��n)���Дࡣ

�����ϵ�y(t��ng)�O(sh��)Ӌ(j��)���������R���ٸ��ܶ��·��������������(zh��n)�⣬�a(ch��n)Ʒ���������ĉ�������ʹ����ɞ�ϵ�y(t��ng)�O(sh��)Ӌ(j��)�ز����ٵ��ֶΡ��O(sh��)Ӌ(j��)��ϣ���������M(j��n)�ķ��湤�ߣ����O(sh��)Ӌ(j��)�A�μ��ҳ����}���Ķ���Ч�ʡ����|(zh��)�������ϵ�y(t��ng)�O(sh��)Ӌ(j��)��

���y(t��ng)���·���O(sh��)Ӌ(j��)�����̎����ٽ���������ֶΡ�����ĕr������������оƬ�S���ṩ�ą����O(sh��)Ӌ(j��)���O(sh��)Ӌ(j��)ָ��(d��o)Ҏ(gu��)�t������Ƥ�������Y(ji��)�Ϲ��̎��Č�(sh��)�H��(j��ng)�(y��n)�M(j��n)���O(sh��)Ӌ(j��)��Ȼ���O(sh��)Ӌ(j��)���a(ch��n)������ԭ�͙C(j��)�M(j��n)�з���(f��)�yԇԇ�(y��n)���ҳ����}�����O(sh��)Ӌ(j��)���@���ܶ���(f��)ʼ��ֱ�����}����ȫ����Q�����rż�����÷��湤���M(j��n)���O(sh��)Ӌ(j��)��Ҳֻ�����ھֲ��·�����·��ζ���r�g�ϵ����t���@�N���t�ڮa(ch��n)Ʒ���������ĉ������ǟo�����ܵģ����䌦�ڴ���ϵ�y(t��ng)��һ̎СС����Ҳ�S��Ҫ�������O(sh��)Ӌ(j��)�Ʒ����������^����һ�l(f��)����ȫ���������o�S�̎����ēpʧ�ǟo�������ġ�

�a(ch��n)Ʒ�|(zh��)�����y�Ա��C���_�l(f��)���ڵIJ��ɿء������̎���(j��ng)�(y��n)���^����ه�����@Щ����ʹ�����O(sh��)Ӌ(j��)�����y�ԑ�(y��ng)��Խ��Խ��(f��)�s�ĸ��ٸ��ܶ�PCB�O(sh��)Ӌ(j��)������������(zh��n)�������횽������M(j��n)�ķ��湤���Խ�Q��������оƬ�S�̽o���O(sh��)Ӌ(j��)�����ǽ����������Լ��Ӱ�Ļ��A(ch��)�ϵģ���ϵ�y(t��ng)�S�̵Įa(ch��n)Ʒ�����ΏS�̵ĘӰ岻������ȫһ�ӣ�ͬ�r��һ��оƬ���O(sh��)Ӌ(j��)Ҫ����ܺ���һ�����ì�ܣ��@�r���ͨ�^������_���O(sh��)Ӌ(j��)����������m���f��

��ij�N���x���v���������ܛ����̓�Mԭ���������ǰ��Ҫͨ�^������ԭ�͵Ĝyԇ���܉���ɵĹ����u�r(ji��)����һ�N���顰ܛ�������ӽ�(j��ng)��(j��)�ķ�����

Ȼ�����ٸ��ܶ��·��ķ���͂��y(t��ng)�ķ�����������ͬ��Mentor Graphics��˾���g(sh��)���̎��������B�������y(t��ng)�ķ�����ᘌ�ԭ��D�����ģ���ֻ�ǼӼ����ݔ�����ɴˁ��Д���Ƿ����_�������ٷ������ڹ������_��ǰ���£����O(sh��)Ӌ(j��)��������Σ�����ᘌ�ԭ��D��ͬ�rᘌ�PCB�O(sh��)Ӌ(j��)�������÷��湤�ߣ������Д���һ���������N����(sh��)�H�����ڝM������Ҫ��Ļ��A(ch��)�ϣ��Д���һ���ijɱ����ͣ��������O(sh��)Ӌ(j��)��ϵ�y(t��ng)�ɱ�֮�g�ҵ�һ��ƽ���c(di��n)���������f�������÷��湤�ߣ������Д�ϵ�y(t��ng)���M(j��n)�ķ����Ƿ����_�����O(sh��)Ӌ(j��)ָ���������һ��ɹ��ʣ�ʹ�a(ch��n)Ʒ���������Ј������ǣ��oՓ����ĽY(ji��)����ô�ӽ��yԇ�Y(ji��)�����������ܴ��挍(sh��)�H�Ĝyԇϵ�y(t��ng)���� �yԇ�nj��������ЬF(xi��n)��(sh��)�h(hu��n)�����ص�ϵ�y(t��ng)���ܵ�һ�N�挍(sh��)�Д࣬Ȼ������s�nj�̓�Mԭ�͵ġ��yԇ������ᘌ�ij�N�ض��l���ģ��]��һ�N���߿��Ԍ����ЬF(xi��n)��(sh��)�l��ȫ�����]�M(j��n)ȥͬ�r���档Ȼ�����S�����g(sh��)�İl(f��)չ���ߵIJ������ƣ�����Y(ji��)���͌�(sh��)�H�yԇ�Y(ji��)���ıƽ���Խ��Խ�ߣ����O(sh��)Ӌ(j��)��ָ��(d��o)���xҲԽ��Խ��ͬ�r�����̎�Ҳ����˸��ߵ�Ҫ���mȻ����Խ��Խ���ã���������Y(ji��)�����Д���M(j��n)��������ه�ڹ��̎��ļ��g(sh��)ˮƽ����Փ���A(ch��)��

Ŀǰ�ڸ���PCB�����У�Ч����������EMC/EMI���@����?y��n)錦�ڸ���ϵ�y(t��ng)�������^��Ч��(y��ng)��Ӱ푣���Ҫ��ϵ�y(t��ng)�M(j��n)�����S��ģ������Чģ�M�挍(sh��)�h(hu��n)����Ȼ������PCB�@��һ�������ҏ�(f��)�s��ϵ�y(t��ng)�������M(j��n)�����S��ģ�dz����y����(j��)�������B��Ŀǰ��Ҫ���Ì��ҙz��ķ�ʽ���Ȱ��Շ��Hͨ�Ø�(bi��o)��(zh��n)��EMC/EMI���}׃�Q��PCB�ϲ��ֲ�����Ҏ(gu��)�t��Cadence ��EMControl�����@��һ������ڌ���ϵ�y(t��ng)��Ҏ(gu��)�t�z�鹤�ߣ�ͬ�r߀�ṩ�˿͑����Ľӿڣ�����͑������m���ڱ���˾��EMC/EMI�z��Ҏ(gu��)�t��Mentor Graphics��Quiet Expert���ԙz������EMI���}�IJ����_�IJ����Y(ji��)��(g��u)���ҳ����}�����o����(d��o)��EMI���}��ԭ��ͽ��h�Ľ�Q������

���⣬�����S�������棬Ansoft��Apsim�ȹ�˾�����ṩ���T�Ĺ��ߺͷ����������@Щ���߿����cCadence��Mentor Graphics��ϵ�y(t��ng)�������ʹ�á�

Ч��֮�x���ԄӲ����c�����O(sh��)Ӌ(j��)

ԭ��D�O(sh��)Ӌ(j��)��ֹ�ǰ��·���衱�M(j��n)ȥ��߀�кܶ�����Ҫ��ԭ��D�O(sh��)Ӌ(j��)���ߑ�(y��ng)ԓ�܌��@ЩҪ����һ���h(hu��n)��(ji��)��֧���ԄӲ��������ܷ���ȡ�

�����ҵ�һ�l����Ч�ʵ��O(sh��)Ӌ(j��)·������Q�a(ch��n)Ʒ�����r�g���������a(ch��n)Ʒ���������Ј����ԄӲ����Ͳ����O(sh��)Ӌ(j��)���g(sh��)��(y��ng)�\(y��n)������

������ܺܺõ������ԄӲ������g(sh��)�����Ԝp�ٮ���r�g����PCB���O(sh��)Ӌ(j��)Ч�����һ�����ϡ��� ��m����B��Ȼ��Ҫ�댍(sh��)�F(xi��n)�ԄӲ�������횽���늚⻯��Ҏ(gu��)�t����������ϵ�y(t��ng)�O(sh��)Ӌ(j��)���̎���Ӳ���O(sh��)Ӌ(j��)���̎����·���O(sh��)Ӌ(j��)Ҫ����f�oPCB���̎���

���������^�麆�ε�ϵ�y(t��ng)��ͨ����������Ӳ�����̎����O(sh��)Ӌ(j��)Ҫ��һ�l�l���������VPCB�O(sh��)Ӌ(j��)���̎����ȥ���������ڏ�(f��)�s��ϵ�y(t��ng)���挦��ǧ���f���B�����o��(sh��)��Ҫ��Ӳ�����̎��o�����@ЩҎ(gu��)�tһһӛ�����PCB�O(sh��)Ӌ(j��)���̎����o��һ�l�lȥ�z��͌�(sh��)ʩ���@�r������Ҫ늚⻯��Ҏ(gu��)�t�����������N�O(sh��)Ӌ(j��)Ҫ�����������Ӳ�����̎���PCB�O(sh��)Ӌ(j��)���̎�������ͬһ��Ҏ(gu��)�t�������Ļ��A(ch��)�υf(xi��)ͬ������Cadence��˾��Ҏ(gu��)�t������Constrain Management�����QCM���ѱ��o�p�ؼ��ɵ���ԭ��D�O(sh��)Ӌ(j��)���ߺ�PCB�O(sh��)Ӌ(j��)�����У�Ӳ�����̎���ԭ��D�O(sh��)Ӌ(j��)��ɺ����O(sh��)Ӌ(j��)Ҫ��늚����ܡ�DFT��DFMҎ(gu��)�t�ȣ��ͱ�CM�Ԅӎ�����һ���h(hu��n)��(ji��)��ϵ�y(t��ng)����(j��)�@ЩҎ(gu��)�t�M(j��n)���ԄӲ���������ԄӲ����ǽ����ڼs��Ҏ(gu��)�t�(q��)�ӻ��A(ch��)�ϵ��ԄӲ�������ͬ�r�����һ���ܺܺ����������@Щ�s��Ҏ(gu��)�t�IJ�������Cadence��Specctra��ʹ���ߺܺõ��_(d��)���y(t��ng)һ��

�����ԄӲ������g(sh��)����m�����h�������һ����˾���g(sh��)�]�����պã���̖�����Ԇ��}���ܺܺý�Q�����h��Ҫ�����ԄӲ�������?y��n)�������ܶ��x�ܺõ�Ҏ(gu��)�t�����o�����_�(q��)���ԄӲ��������oՓ������ΰl(f��)�_(d��)��Ӌ(j��)��C(j��)����������ȫȡ���˵Ĵ��X�О飬���Ҳ�Ͳ�������100�����ԄӲ�����ǰ���҂����f���ԄӲ����䌍(sh��)��һ�N����ʽ���ԄӲ�������Ҫ�˵ą��c���ԄӲ�����ǰ��ЩҎ(gu��)�t߀��Ҫ�ֹ��M(j��n)һ���_�����ԄӲ�������Ժ���Ҫ���̎��(y��n)�C���ġ�

���ڂ��y(t��ng)�ġ��^����ٵ�ϵ�y(t��ng)�O(sh��)Ӌ(j��)���ܶ�̎����ܶ����^�@�ӵĽ�(j��ng)�(y��n)����Cadence��OrCAD��ԭ��D������Mentor��PowerPCB�����ֲ���������m���J(r��n)�飬�@�N�����ڸ����O(sh��)Ӌ(j��)�I(l��ng)�����m�ϡ�����(sh��)��(j��)�ڲ�ͬ�S�̵Ĺ���֮�g���܌�(sh��)�F(xi��n)��ȫ�D(zhu��n)�Q�����磺���y(t��ng)���x�W(w��ng)���ķ����������ܰ�ԭ��D�е�һЩ늚���Ժ�Ҫ��PCB�O(sh��)Ӌ(j��)�У�������m�ϸ����O(sh��)Ӌ(j��)����

���ԄӲ�����������ϵ�y(t��ng)�������O(sh��)Ӌ(j��)Ҳ������O(sh��)Ӌ(j��)Ч�ʵ���Ч;���������O(sh��)Ӌ(j��)���f(xi��)ͬ�O(sh��)Ӌ(j��)�����nj�һ�K�·��ָ�Ɏײ��֣��Ɏׂ���ͬ�r�M(j��n)���O(sh��)Ӌ(j��)����(j��)�������B��ĿǰMentor Graphics�Ĺ����ڲ����O(sh��)Ӌ(j��)�����ѽ�(j��ng)���������������һ�_�C(j��)���ϵ��O(sh��)Ӌ(j��)��P����һ�_�C(j��)�����̿��Կ�Ҋ�����҃�߅���B�������Ԅ��B��һ���@�ӿ��Ԝp�p��ͬ�O(sh��)Ӌ(j��)֮�g���ϵ��΄�(w��)���������f������������Щ�r��Mentor Graphics��˾��ȫ�ӑB(t��i)�IJ����O(sh��)Ӌ(j��)����extremePCB�Ϳ��������Ј������r���̎��Ϳ�����(li��n)�W(w��ng)��CSһ���M(j��n)����ȫ��(sh��)�r�IJ����O(sh��)Ӌ(j��)�����˴˵��O(sh��)Ӌ(j��)���Ԍ�(sh��)�r��������Ҋ���@�ӿ��Է��㮐�ع��̎�֮�g�ĺ����������ڲ����O(sh��)Ӌ(j��)����m���J(r��n)�飬��������Ҫ�õ��O(sh��)Ӌ(j��)���ߣ�����Ҫ�õ��O(sh��)Ӌ(j��)�����������h�������O(sh��)Ӌ(j��)��Ҫ�ֵ�̫��(x��)��̫�V��2~3�˱��^��������t˼·̫��ɢ�������������O(sh��)Ӌ(j��)����(j��)Ϥ��Cadence�IJ����O(sh��)Ӌ(j��)����Ҳ������һ�汾���Ƴ��� ��ԽPCB�����ن��}��ϵ�y(t��ng)�����]

��(d��ng)ϵ�y(t��ng)�Ďװ��װl(f��)չ����(sh��)ʮ���r��оƬ�O(sh��)Ӌ(j��)�����b�O(sh��)Ӌ(j��)��ϵ�y(t��ng)�O(sh��)Ӌ(j��)�ѽ�(j��ng)�������ٷ��_���]�����ڸ߶ˮa(ch��n)Ʒ�����O(sh��)Ӌ(j��)оƬ�r���͑�(y��ng)ԓ���]���b�O(sh��)Ӌ(j��)��ϵ�y(t��ng)�O(sh��)Ӌ(j��)��

��ȥ��ܛ�������Ć��}֮����ξ������̣��������Ϝp�ٹ��̎���ʧ�`��ʹ���̎��Ѹ���ľ���Ͷ�뵽�O(sh��)Ӌ(j��)֮�У�ʹ�a(ch��n)Ʒ�M���M(j��n)���Ј���Ҳ�ѽ�(j��ng)�ɞ�EDA�S�����ڿ��]�ă�(n��i)�ݡ�

ͨ����һ��ϵ�y(t��ng)�ϵ��B�Ӿ���ʼ��оƬ��Silicon����I/O����(j��ng)�^���b��Package����bump��substrate�����_(d��)���b��pin��Ȼ��(j��ng)�^PCB������һ���b��pin��substrate��bump��оƬ��I/O��оƬ�����b���·�壬�@��������ͬ���I(l��ng)����ǰ�Ĺ��̎����O(sh��)Ӌ(j��)�ĕr��ȥ�C�Ͽ��]��Ҳ�o��֪���������̎����뷨�������S���O(sh��)Ӌ(j��)�l�ʵ���ߡ�оƬ��e�ĜpС���O(sh��)Ӌ(j��)���ڵĿs�̣��S������оƬ�O(sh��)Ӌ(j��)�r�͑�(y��ng)ԓ���]�����b�O(sh��)Ӌ(j��)��PCB�O(sh��)Ӌ(j��)��ʹ������Ч�ؽY(ji��)����������m���J(r��n)�飬���@�r�oՓ����̖�������ρ��f��߀�Ǐ��O(sh��)Ӌ(j��)�����ρ��f���҂�����(y��ng)ԓͬ�r���]Silicon-Package-Board���O(sh��)Ӌ(j��)�����f(xi��)�{(di��o)����֮�g�Ļ���(li��n)ϵ�������f���Еr��PCB�Е��к��y��Q�ĕr���}����Package�Ѕs���Ժ����ؽ�Q����

Cadence����ϵ�y(t��ng)�������O(sh��)Ӌ(j��)�ķe�O����(d��o)�ߣ���Allegroƽ�_�����w�˰弉�O(sh��)Ӌ(j��)�ͷ��b���O(sh��)Ӌ(j��)�������Ժ�Cadence�������ׂ�оƬ�O(sh��)Ӌ(j��)ƽ�_�����������γ��������O(sh��)Ӌ(j��)朣���(sh��)�F(xi��n)��(sh��)��(j��)����Ч���Q�͜�ͨ�����⣬Cadence��VSIC��Virtual System InterConnect���O(sh��)Ӌ(j��)������һ�N�µ�Silicon-Package-Board �f(xi��)ͬ�O(sh��)Ӌ(j��)��������ʹ�ù��̎����O(sh��)Ӌ(j��)���ھͿ��Կ��]����ϵ�y(t��ng)����ĕr�������̖�����ԵĆ��}����Q��ǧ����̖�O(sh��)Ӌ(j��)��һ��ƿ�i�� Allegro DesignWorkbench �t�Ǻ�MatrixOne(li��n)���Ƴ�������O(sh��)Ӌ(j��)�I(l��ng)���һ��PLM��Product Lifecycle Management���a(ch��n)Ʒ�����C�˹��̎��ں��m�ĕr�g�����m�ĵ��c(di��n)���xȡ����m�������������϶������F(xi��n)�е��O(sh��)Ӌ(j��)���̎������h(yu��n)��Ӱ푣����ܕ��s�̹��̎�50%���O(sh��)Ӌ(j��)���ڡ��� ��m����B�f��

���x��m�������������������ش���L���}���ṩ���P(gu��n)�Y�ϣ�

��m���������I(y��)����ӿƼ���W(xu��)���@��ӌW(xu��)�Tʿ�W(xu��)λ��������ИI(y��)���г��^14����S����(j��ng)�(y��n)���F(xi��n)��Cadence��˾����ϵ�y(t��ng)���g(sh��)���ĸ���(j��ng)����

�������������I(y��)�ڹ����I���̴�W(xu��)���@ˮ���̲�ʿ�W(xu��)λ��������c��̖̎��ϵ�y(t��ng)�O(sh��)Ӌ(j��)������г��^10����S����(j��ng)�(y��n)����������2004��2�¼���Mentor Graphics�Ї���(d��n)���Ј����N���g(sh��)���̎���

���ģ��a(ch��n)�I(y��)朵ĸ���

��EDA�����Ј���EDA�S�̺����ΏS�̵��P(gu��n)ϵֱ��Ӱ����乤����ijһ�Ј���ռ���ʡ���PCB�O(sh��)Ӌ(j��)���߸߶��Ј���Mentor Graphics��Cadenceռ��(j��)�˽^���Ј����~��������Ӌ(j��)��C(j��)�����I(l��ng)��Mentor�sֻռ��10-20%���Ј����g����(j��)��B���@��Ҫ������Cadence�����ΏS��Intel��������o�ܵĺ����P(gu��n)ϵ��Intel�ṩ�o���ΏS�̵�ԭ��D�����O(sh��)Ӌ(j��)������Cadenceܛ����(sh��)�F(xi��n)�ģ������ֱ��Ӱ������ΏS�̵đB(t��i)�ȡ����b�ڴˣ�Mentor GraphicsҲ�m�r�ӏ�(qi��ng)���cIntel�ĺ����P(gu��n)ϵ����(j��)Mentor Graphics��˾���g(sh��)���̎��������B��Mentor Graphics�cIntel�I(y��)���_(d��)�Ʌf(xi��)�h��Intelδ��������Ƭ����������Mentor Graphics���ߌ�(sh��)�F(xi��n)���O(sh��)Ӌ(j��)�������@Щ�O(sh��)Ӌ(j��)��������ԭ��D�O(sh��)Ӌ(j��)��������PCB�O(sh��)Ӌ(j��)�����҂����ţ�ͨ�^��Intel�ĺ�����Mentor�ĸ���ϵ�y(t��ng)�O(sh��)Ӌ(j��)������Ӌ(j��)��C(j��)�����Ј���ռ���ʌ����кܴ����������������f��

���҂��Ϳ͑����P(gu��n)ϵ�Ѳ����džμ����I�u�P(gu��n)ϵ�����Ǻ����������湲ͬ�w���P(gu��n)ϵ�������Ǹ߶˹��ߣ����Ǐ�(qi��ng)��(qi��ng)�Y(ji��)�ϵĽY(ji��)������ Cadence��˾����ϵ�y(t��ng)���g(sh��)���ĸ���(j��ng)����m���f�� ��(j��)��B��Cadence���Դ�����Թ���PI�Ǻ�SUN��ͬ�_�l(f��)�ģ�ͬ�r��Cadence���ں�Motorola(li��n)���_�l(f��)RFSiP���b����Q������

�S�����g(sh��)�İl(f��)չ���Ј��h(hu��n)����׃�����S��֮�g�ĸ����ѽ�(j��ng)�Ĺ���(y��ng)朣����ɱ��ĸ����D(zhu��n)��a(ch��n)�I(y��)朵ĸ�������ϵ�y(t��ng)�S�̺�оƬ�S�̽Y(ji��)�����湲ͬ�w���c��һϵ�y(t��ng)�S�̺�оƬ�S�̵����湲ͬ�w֮�g�ĸ�����

]]>

����Ӽ��g(sh��)�l(f��)չ���Sǧ��Ľ��죬ҲԽ��Խ��ĸ��N��(y��u)��EDA��Electronic Design Automatic ����O(sh��)Ӌ(j��)�Ԅӻ����·�O(sh��)Ӌ(j��)ܛ������S��ӿ�F(xi��n)��������(d��ng)Ȼ���o���S�ĸ��NEDAܛ���̿ƕ�Ҳ�廨���T���ӳ����F��ÿһ�̿ƕ���������(d��)�صČ����L(f��ng)�������x���ܷ�������I(l��ng)��(d��ng)Ȼ��������(d��ng)�eՓ���ܶ���W(xu��)�߷�醲��ٕ�����ʼ�K���֟o�ߟo�����֡����v�^�����ϵĸ��N�P(gu��n)���@����ĕ�������Ŷ������^��(f��)�s���·�M(j��n)���v�⣬����X���@��ʲô֮ĸ߿Ƽ��a(ch��n)Ʒ�M(j��n)���v�⣩��ˣ����˽�(j��ng)�^���^�L�r�g�ķ�˼�����(d��)��(chu��ng)һ�У�ԓ�����÷����y(t��ng)�Č�����ʽ�����������µġ������^����?q��)�������ģʽ���\(y��n)��̓�M�n�õ��v����ʽ���ѹ����h(hu��n)���ЙC(j��)�ؽY(ji��)����һ���x�����ڼ���Ϳ��Եõ����R�n�á������F(xi��n)���ČW(xu��)��(x��)���ܡ�

�ܶ��·�O(sh��)Ӌ(j��)���W(xu��)�ߣ��������@�ӵ�Ը����ϣ�����û��M(f��i)̫��ĕr�g�ͽ��X���W(xu��)У��W(xu��)��(x��)���H�H���ڼ���������ØI(y��)���r�g��Ȼ���Եõ��������ʽ���n���ϵČ��I(y��)ָ��(d��o)��ϣ����Ҫ�ȵ���ʽ̤�Ϲ�����λ�������Ռ��������еĸ��N���I(y��)���ܣ�ϣ���ڌW(xu��)��(x��)�^�������S�r�õ�ָ��(d��o)����

�����������С��ߵȴ�ԺУ�����������I(y��)�̲ģ���ɹ���������·�O(sh��)Ӌ(j��)�_�l(f��)��(y��ng)�õďV����ӹ��̎������g(sh��)�ˆT������֔(j��n)�Դ˕��I(xi��n)�o�V����Ӿ�·�O(sh��)Ӌ(j��)�ۺ��ߡ�

���(qu��n)�w��������

��(n��i)����Ҫ

�]�������̲ĵď�(f��)�s�ԣ����W(xu��)�߄����|ԓܛ�����I(l��ng)���������Լ����˵����ֱ��_(d��)�����cˮƽ�dz����ޣ�������Ҫ��Ԕ��(x��)��B�ɉK��·�^����һ�c(di��n)���p�Ӱ��c�ΌӰ���O(sh��)Ӌ(j��)��(sh��)���M(j��n)���v�⡣���h�x�߰����˵�˼·һ��һ��������ȥ���������O(sh��)Ӌ(j��)���^�������c���ԓ��·���ӵ��O(sh��)Ӌ(j��)�������µ��¹�(ji��)�п����кܶ�ĵط��c��(x��)��(ji��)���؏�(f��)�c�_�µĬF(xi��n)��Ո�x��Տ�⣬�������˲��nj��I(y��)�Ŀƣ�����ˮƽ�dz�֮���ޣ��gӭ������uָ��������w���и��õ�Ҋ�⣬Ҳ�����������h�cָ��һ�£����·dz�����Ո�̡�����E-mail��powerpcb88@163.com

ԓ���Y(ji��)�������߶������Ӿ�·�O(sh��)Ӌ(j��)�����Ќ�(sh��)�`���@ȡ�Ĺ�����(j��ng)�(y��n)�������˽̌W(xu��)�ĸ�ijɹ���������������(j��)�����O(sh��)Ӌ(j��)����ȫ�^�̼��W(xu��)��(x��)�ߵ�֪�RҎ(gu��)�Ɂ����Ń�(n��i)�ݣ�����w�F(xi��n)�����˞鱾��ָ��(d��o)˼�롣���W(xu��)�ߌ�PCB Layout�܉���ٵ��������T�c��ߵļ��ɡ�

�����ڽ�BPADS Powerܛ���O(sh��)Ӌ(j��)�^�̕r������ʮһ�¹�(ji��)���p�������������O(sh��)Ӌ(j��)���̞�����(d��o)�M(j��n)��������Ԕ��(x��)�v��PADS Powerܛ���đ�(y��ng)�÷����ͼ��ɡ����У���һ����PADS Powerܛ���������ڶ��£�PADS Power ܛ���İ��b�������£�PADS PowerԪ���죻�����£�Ԫ����CAE���b�������£�Ԫ����PCB���b�������£�Ԫ����͵ķ��b�������£�ԭ��D���O(sh��)Ӌ(j��)���ڰ��£� PCB��Layout�O(sh��)Ӌ(j��)���ھ��£��������Ԫ����CAE���b�� PCB���b����ʮ�£��������Ԫ����Ԫ����ͷ��b�cԭ��D�O(sh��)Ӌ(j��)����ʮһ�£�������ӵ�PCB�O(sh��)Ӌ(j��)��

�c(di��n)�����³����B���B�ӵ����¹�(ji��)��(n��i)�ݡ����ߌ��ØI(y��)���r�g�M(j��n)�и��£�

��һ�£�PADS Power ܛ������

�ڶ��£�PADS Power ܛ���İ��b���ƽ⣩

�����£�PADS PowerԪ����

�����£�Ԫ����CAE���b

�����£�Ԫ����PCB���b

�����£�Ԫ����͵ķ��b�O(sh��)Ӌ(j��)

]]>

�Ұl(f��)���������°�Power pcb 5.01��Power logic 5.01

�����Ҳ����D,�N�˂�3.5��ĈD,3.5�����Ҳ��,����Ҫ�l(f��)�Ͱl(f��)���°�İ�,���ڸ�PCB��·�O(sh��)Ӌ(j��)������ͬ�ʑ�(y��ng)ԓ����һЩ������

���ǹ�˾��(n��i)���W(w��ng),�����_ͨ�˶˿�ӳ��,�Ǹ�ID,ÿ��8:30~18:00���C�_�C(j��),�����r�g�����°౧Ǹ�����ṩԴ!

PowerPCB 5.0.1���b

1.���b�r�x��Node-locked with FLEXid Key(teal)��

2.Ҫ��license�r������CrackĿ��µ�pcblic.dat����

3.���b������Ҫ������Ӌ(j��)��C(j��)����ӛ�ˣ�

4.�\(y��n)��\(zh��ng)CRACK\Dongle\FlexID\WinNT\Ŀ��µ�setupx86.exe��WIN2000��WINXP��

������\CRACK\Dongle\FlexID\Win9x\Ŀ��µ�sentw9x.exe��WIN98��

��(zh��)��FunctionsĿ��µġ�Install Sentinel Driver��

�ԫ@��FLEXID7�顰7-12345678��

��ͬ�r߀������һ����Ҳ�����õģ�

5.������Ӌ(j��)��C(j��)

6.�M(j��n)��Dos�����crackĿ����\(y��n)�С�PCBCrypt -h 7-12345678��

����HOSTID=FLEXID=7-12345678��license�ļ���pcblic.dat

��������һ��FLEXID7Ҳ���ԣ�F(xi��n)LEXID7�����á��_ʼ����>

��PowerPCB with BlazeRouter5.0����>��Security��->

��Licensing diagnostics�����ߵġ�System Setting���x�(xi��ng)��������

7.��CRACKĿ��µ�pcblic.dat����PowerPCB���bĿ���

\Security\Licenses\Ŀ��µ�pcblic.dat

OK

���Ԇ���PowerPCB��BlazeRouter��

=========================================================

���\(y��n)��\(zh��ng)PowerPCB 5.0 \Crack\Dongle\FlexID\WinNT\setupx86.exe֮��һ��Ҫconfig Sentinel driverһ�£�Ȼ�������ӣ�

���Ӻ����\(y��n)��PCBCrypt.exe���a(ch��n)��license.dat��,

���\(y��n)��\(zh��ng)PowerPCB 5.0 \Crack\Dongle\FlexID\WinNT\setupx86.exe���@��Ҫ�xRomove Sentinel Driverһ�£�Ȼ���������әC(j��)�ӣ�

��������bPowerpcb5.0,�b������\(y��n)��\(zh��ng)PowerPCB 5.0 \Crack\Dongle\FlexID\WinNT\setupx86.exeһ�£�

Ȼ���xconfig Sentinel driverһ��,Ȼ���ن��әC(j��)�ӣ������OK��

���bPowerPCB 5.01,�ٰ��bPower logic 5.01

�ƽ���ѽ�(j��ng)�ṩ��,Power PCB 5.01ʹ��Powerpcb5.0ͬ�ӵ��ƽⷽʽ

]]>

�҂����������M(j��n)�Ē��蹤ˇ�cܛ�����g(sh��)��Y(ji��)��,��¡��,���Ӽ�PCB,���Nä����y��PCB,�·��(zh��n)�_���C100%,���������ɬF(xi��n)�����е�PCB�O(sh��)Ӌ(j��)ܛ����ʽ�ęn;��POWER-PCB,PROTEL99,PADS2000,PCB�D(zhu��n)ԭ��D��BOM��.

��ʾ:���˱��o(h��)ԭ��(chu��ng)PCB�O(sh��)Ӌ(j��)���(qu��n)�����ߵĺϷ���(qu��n)��,���DZ���˾�M(j��n)��PCB��¡�I(y��)��(w��)�Ŀ͑�,���������(qu��n)��Դ�ĺϷ���

2��.PCB���a(ch��n)�ӿ��ļ�

(1)�ṩPCB��GERBER�ļ�

(2)PCB���a(ch��n)Ҏ(gu��)���f����

���|(zh��)�� ���M(f��i)��

�� PCB�O(sh��)Ӌ(j��)�_�l(f��)��PCB���壺����(j��)늚�ԭ��D�ͽY(ji��)��(g��u)�D�\(y��n)�Ì��I(y��)PCB�O(sh��)Ӌ(j��)ܛ���M(j��n)�в����O(sh��)Ӌ(j��),�҂����Ќ��I(y��)�ġ��н�(j��ng)�(y��n)���O(sh��)Ӌ(j��)�(du��)�飬�ܿ˷�ĿǰPCB�O(sh��)Ӌ(j��)�����е�һЩȱ�ݣ������ٔ�(sh��)��(j��)���M(j��n)��ģ�M���棬���C�O(sh��)Ӌ(j��)�|(zh��)����Ŀǰʹ�õ�PCB�O(sh��)Ӌ(j��)ܛ���У�PROTEL��POWERPCB��PADS-2000��ORCAD��CADSTAR��;�҂�����ȫ�����M(j��n)�Č�(sh��)�(y��n)�O(sh��)�䣬�ܜyԇPCB�往·��̖�����Р�B(t��i)���Ա��CPCB�O(sh��)Ӌ(j��)�_(d��)��Ҫ���҂�Ҳ���Ը���(j��)�F(xi��n)�е�PCB���M(j��n)�г����(f��)�ƣ��������(f��)�Ƶ�PCB�D���ȷdz��ߣ������c�Ӱ�һ�ӣ������(f��)���M(f��i)�õͣ���͑���(ji��)ʡ�O(sh��)Ӌ(j��)�M(f��i)�á�

�� PCB�ӹ����҂����Ќ��I(y��)��OEM PCB�ӹ��S�����M(j��n)�������M(j��n)�O(sh��)��ͼ��g(sh��)���܉������ṩ���ܶȡ��߾��ȵĆ��桢�p�桢���ӄ���PCB���ܛ��PCB������;

�� ���Ԫ������ُ�����ӣ���o�͑��p��Ԫ������ُ�韩���s�̕r�g���҂����͑��ṩԪ������ُ����(w��)��PCBA���S��͑��ṩ������NƬ��DIP��SMD/SMT�����ӷ���(w��)��Ŀǰ���S�ɺ���0201��CSP��BGA���͡����ܶȷ��b��Ԫ������

�� ��Ӯa(ch��n)Ʒܛ����Ӳ���O(sh��)Ӌ(j��)�_�l(f��)���҂���һ�����p�г�����_�l(f��)���̎��M���_�l(f��)�F(tu��n)�(du��)����Ϥ��ͬ��ܛӲ�������N�f(xi��)�h���܉���١�ȫ��؞�͑�����(w��)����Ӯa(ch��n)Ʒܛ����Ӳ���O(sh��)Ӌ(j��)�_�l(f��)�漰Ӌ(j��)��C(j��)��ͨ�š��W(w��ng)�j(lu��)�O(sh��)�䡢�֙C(j��)����(sh��)�a���C(j��)���x���x���ȸ߿Ƽ��I(l��ng)���҂���51ϵ�С�PICϵ�С�AVRϵ�С�MOTOROLAϵ�І�Ƭ�C(j��)��MCU���(xi��ng)Ŀ���кܶ�ɹ�����;���Z�Ծ��̷��棬�܉����(j��)�͑�Ҫ��ʹ��C��C++��VB��VC++��PRO C��JAVA��JSP��C++ BUILDER���κ��Z�ԁ��_�l(f��)��ͬ�rҲ�܉�?y��n)�͑��M(j��n)�Д�(sh��)��(j��)��ܛ���_�l(f��)��

�� ��Ӯa(ch��n)Ʒ������Q�������c�͑������ͨ����(f��)Փ�C�_���O(sh��)Ӌ(j��)��ܣ�Ȼ���ṩ�Įa(ch��n)Ʒԭ���O(sh��)Ӌ(j��)���Y(ji��)��(g��u)���֣�ܛ���_�l(f��)��Ӳ���_�l(f��)����Ԫ������ُ�����a(ch��n)Ʒ�yԇ�ӹ�����Ʒ���һ�l��ʽ�a(ch��n)Ʒ����(w��)������Щ��ע�a(ch��n)Ʒ�Ј��ƏV�Ŀ͑���(ji��)ʡ�����_�l(f��)�r�g���_�l(f��)�M(f��i)�ã������͑����h(yu��n)�ڮa(ch��n)Ʒ�Ј��Ͼ����I(l��ng)�ȃ�(y��u)�ݣ���͑�(chu��ng)��r(ji��)ֵ��

]]>

�P(gu��n)�I�~: Konqueror��Ƕ��ʽ�g�[����arm-Linux����ֲ���h��

����

Ŀǰ��Ƕ��ʽ�g�[���ѽ�(j��ng)��u�ɞ�߶��֙C(j��)��PDA�Ę�(bi��o)��(zh��n)���á�Konqueror/embedded����Ƕ��ʽLinux����ϵ�y(t��ng)�����x�g�[���õ��ˏV��ʹ�á���������ԓ�g�[��������ܛ�����������wǶ��ʽƽ�_��ֲ�r����һ�����y�ȡ�������Ҫ��B��Konqueror/embedded ��arm-Linuxƽ�_�ϵ�������ֲ�͝h���^�̣��Ա㹤�̎�������ʹ�á�

Konqueror/embedded�ĽY(ji��)��(g��u)

Konqueror/embedded ���ɵӾW(w��ng)�j(lu��)�B�ӣ��D�λ��Ñ������̎��HTML�L�Ƶ�����KHTML��(g��u)�ɵġ��ӵ�ͨ���f(xi��)�h��(sh��)�F(xi��n)�ǻ���KIO/slave�C(j��)�Ɓ팍(sh��)�F(xi��n)�ģ�GUI������� Kparts�M�����g(sh��)��Qt�Ļ�����(g��u)����������Konqueror/embedded�ĺ���,KHTML�t�\(y��n)�����ęn����ģ��(DOM)���ṩ��API�ӿڣ�����DOM���ϒ��javascript���棬CSS�������Լ���Ⱦ���档Konqueror/embedded�ČӴνY(ji��)��(g��u)��D1��ʾ��

�D1 Konqueror/embedded�ӴνY(ji��)��(g��u)

Kparts��Qt��(g��u)����(sh��)�F(xi��n)GUI

���˷���،�(sh��)�F(xi��n)���F(xi��n)�Б�(y��ng)������һ���ؼ����뵽����һ����(y��ng)����ȥ��������part����ؓ(f��)؟(z��)����������(y��ng)�úʹ��ڡ�����ÿ�������ֲ�ȡ����� ܛ MFC �е� Doc-View �Y(ji��)��(g��u)������ڌ���(y��ng)��Ƕ�뵽����һ����(y��ng)���еĕr��ֻ��Ҫ�@��part�еĽӿں͔�(sh��)��(j��)���ɡ������ڵ�һ�в�����푑�(y��ng)�ɱ�Ƕ�둪(y��ng)�õ� part �������ɣ���� Doc-View �Y(ji��)��(g��u)ֻؓ(f��)؟(z��)�@ʾ�ͱ��攵(sh��)��(j��)���ɡ�

����Konqueror/embedded�ǻ��ڈD�Ύ�Qt/E�����Ҳ��ѭ��signal��slot��Ϣ�C(j��)�ƣ�Konqueror/embedded����Qt/E��һ����(bi��o)��(zh��n)��(y��ng)�ó����M(j��n)��ݔ��/ݔ����������Ϣ푑�(y��ng)��

��(zh��)��DOM ģ�K

DOM ģ�K����(j��ng)�^�����Ę�(bi��o)ӛ�M(j��n)���Z���z�飬���ь��Կ�����(ji��)�c(di��n)������(bi��o)ӛ���Z�x�����P(gu��n)ϵ�Լ��Ⱥ����M����DOM�䡣���oHTML �ęn���x��һ���cƽ�_�o�P(gu��n)�ij���ӿڣ�ʹ��ԓ�ӿڿ��Կ����ęn�ă�(n��i)�ݡ��ӿں͘�ʽ��

�ڈ�(zh��)��DOMģ�K���^���У��g�[�������Џ��Z���Z�x����ģ�K�Ы@�õĘ�(bi��o)ӛ�͌��ԣ�����һ���ČӴνY(ji��)��(g��u)�M����DOM �䡣���DOM ��Ę�(g��u)����DOM ģ�K��ͬ�r�ј�(bi��o)ӛ�͌����Ԍ������ʽ���o����ģ�K���_������ģ�K��

��(zh��)��I/Oģ�K

�g�[�����d���P(gu��n)��I/O�ļ�����HTTP���f(xi��)�h�M(j��n)�н������Z���Z�x����ģ�K�Ľ������ܷ֞�ɲ��֣������յ����ֹ�(ji��)���M(j��n)�з��~���������P(gu��n)�I�֣��{(di��o)�ý������z�(y��n)�P(gu��n)�I���Ƿ�Ϸ������ǺϷ����P(gu��n)�I�֣��t����Ҏ(gu��)�t���뵽DOM ���С�