ΓΓΓΓΓΓΓρ PCB‘O(sh®®)”΄(j®§)ΦΦ«…

ΓΓΓΓΓΓΓρ PCB Layout÷ΗΡœ

ΓΓΓΓΓΓΓρ PCBΒΡΆβ–ΆΦ”ΙΛ

ΓΓΓΓΓΓΓρ –ΨΤ§ΚΗ±P‘O(sh®®)”΄(j®§)‰Υ(bi®Γo)€ (zh®≥n)

ΓΓΓΓΓΓΓρ ViaΩΉΒΡΉς”ΟΦΑ‘≠άμ

ΓΓΓΓΓΓΓρ »γΚΈ‘ΎPCB‘O(sh®®)”΄(j®§)÷–Κœάμ≤Φ÷ΟΗς‘ΣΦΰ

ΓΓΓΓΓΓΓρ PCB“ΜΑψρû(y®Λn) ’‰Υ(bi®Γo)€ (zh®≥n)

ΓΓΓΓΓΓΓρ PCBΡΩôzôzρû(y®Λn)“é(gu®©)ΖΕ

ΓΓΓΓΓΓΓρ PCB‘O(sh®®)”΄(j®§)÷Η“ΐ

ΓΓΓΓΓΓΓρ Cadence Allegro ΚÜ(ji®Θn)Ϋι≈cΑ≤―bΖΫΖ®

ΓΓΓΓΓΓΓρ Mentor PADS2005 Α≤―bΖΫΖ®

ΓΓΓΓΓΓΓρ ”Γ÷Τκä¬ΖΑεΒΡΩ…ΩΩ–‘‘O(sh®®)”΄(j®§)-ΒΊΨÄ‘O(sh®®)”΄(j®§)

ΓΓΓΓΓΓΓρ Cadence Allegro ΚÜ(ji®Θn)Ϋι≈cΑ≤―bΖΫΖ®

ΓΓΓΓΓΓΓρ Mentor PADS2005 Α≤―bΖΫΖ®

ΓΓΓΓΓΓΓρ OrCAD 10.5 ΚÜ(ji®Θn)Ϋι≈cΑ≤―b

ΓΓΓΓΓΓΓρ Mentor WG/EN2004 Α≤―b’fΟς

ΓΓΓΓΓΓΓρ Protel DXP 2004 ΚÜ(ji®Θn)Ϋι≈cΑ≤―b]]>

| œ¬ίd–≈œΔ [ΈΡΦΰ¥σ–ΓΘΚ œ¬ίd¥ΈîΒ(sh®¥)ΘΚ ] | |

ϋc(di®Θn)™τûg”[‘™ΈΡΦΰ:ΓΑcadenceΖ¬’φΓ±ΗΏΦâ(j®Σ)―––όΑύ.rar ϋc(di®Θn)™τûg”[‘™ΈΡΦΰ:ΓΑcadenceΖ¬’φΓ±ΗΏΦâ(j®Σ)―––όΑύ.rar |

<p class="MsoNormal" style="MARGIN: 0cm 0cm 0pt; LINE-HEIGHT: 13pt; mso-line-height-rule: exactly;"><b style="mso-bidi-font-weight: normal;"><span style="FONT-SIZE: 14pt; COLOR: black; FONT-FAMILY: ΥΈσw;">“ΜΓΔ<span style="mso-bidi-font-weight: bold;">≈ύ”•(x®¥n)ïr(sh®Σ)ιgΓΔΒΊϋc(di®Θn)<span lang="EN-US">:</span></span></span></b><span lang="EN-US" style="FONT-SIZE: 14pt; COLOR: black; FONT-FAMILY: ΥΈσw;">2Χλ,…œΚΘ 2009Ρξ8‘¬29-30»’Θ§8‘¬28»’?q®Ϊng)?b®Λo)ΒΫΘΜ<b style="mso-bidi-font-weight: normal;">

</b></span>

<p class="MsoNormal" style="MARGIN: 0cm 0cm 0pt; LINE-HEIGHT: 13pt; mso-line-height-rule: exactly;"><b style="mso-bidi-font-weight: normal;"><span style="FONT-SIZE: 14pt; COLOR: black; FONT-FAMILY: ΥΈσw;">ΕΰΓΔ<span style="mso-bidi-font-weight: bold;">’n≥ΧΧαΨVΘΚ<span lang="EN-US">

</span></span></span></b>

<table cellspacing="0" cellpadding="0" width="665" align="left" border="1" style="BORDER-RIGHT: medium none; BORDER-TOP: medium none; BORDER-LEFT: medium none; WIDTH: 498.6pt; BORDER-BOTTOM: medium none; BORDER-COLLAPSE: collapse; mso-border-alt: solid windowtext .5pt; mso-table-lspace: 9.0pt; mso-table-rspace: 9.0pt; mso-table-anchor-vertical: paragraph; mso-table-anchor-horizontal: margin; mso-table-left: -3.65pt; mso-table-top: 4.7pt; mso-padding-alt: 0cm 5.4pt 0cm 5.4pt;"><tbody><tr style="HEIGHT: 15.2pt;"><td valign="top" width="319" style="BORDER-RIGHT: windowtext 0.5pt solid; PADDING-RIGHT: 5.4pt; BORDER-TOP: windowtext 0.5pt solid; PADDING-LEFT: 5.4pt; PADDING-BOTTOM: 0cm; BORDER-LEFT: windowtext 0.5pt solid; WIDTH: 239.4pt; PADDING-TOP: 0cm; BORDER-BOTTOM: windowtext 0.5pt solid; HEIGHT: 15.2pt; BACKGROUND-COLOR: transparent;"><p class="MsoNormal" style="MARGIN: 0cm 0cm 0pt; LINE-HEIGHT: 13pt; mso-line-height-rule: exactly; mso-element: frame; mso-element-frame-hspace: 9.0pt; mso-element-wrap: around; mso-element-anchor-vertical: paragraph; mso-element-anchor-horizontal: margin; mso-element-left: -3.6pt; mso-element-top: 4.7pt; mso-height-rule: exactly;"><b style="mso-bidi-font-weight: normal;"><span lang="EN-US" style="FONT-SIZE: 14pt; FONT-FAMILY: –¬ΥΈσw; mso-bidi-font-family: ΥΈσw-18030;">

</span></b>

<p class="MsoNormal" style="MARGIN: 0cm 0cm 0pt; LINE-HEIGHT: 13pt; mso-line-height-rule: exactly; mso-element: frame; mso-element-frame-hspace: 9.0pt; mso-element-wrap: around; mso-element-anchor-vertical: paragraph; mso-element-anchor-horizontal: margin; mso-element-left: -3.6pt; mso-element-top: 4.7pt; mso-height-rule: exactly;"><b style="mso-bidi-font-weight: normal;"><span style="FONT-SIZE: 14pt; FONT-FAMILY: –¬ΥΈσw; mso-bidi-font-family: ΥΈσw-18030;">ΒΎ“ΜΧλ…œΈγΘΚ<span lang="EN-US">

</span></span></b>

<p class="MsoNormal" style="MARGIN: 0cm 0cm 0pt; TEXT-INDENT: 7pt; LINE-HEIGHT: 13pt; mso-line-height-rule: exactly; mso-element: frame; mso-element-frame-hspace: 9.0pt; mso-element-wrap: around; mso-element-anchor-vertical: paragraph; mso-element-anchor-horizontal: margin; mso-element-left: -3.6pt; mso-element-top: 4.7pt; mso-height-rule: exactly; mso-char-indent-count: .5; mso-char-indent-size: 14.0pt;"><span lang="EN-US" style="FONT-SIZE: 14pt; FONT-FAMILY: –¬ΥΈσw; mso-bidi-font-family: ΥΈσw-18030;">1ΓΔΗΏΥΌ‘O(sh®®)”΄(j®§)≈cPCBΖ¬’φΝς≥ΧΘΜ

</span>

<p class="MsoNormal" style="MARGIN: 0cm 0cm 0pt; TEXT-INDENT: 7pt; LINE-HEIGHT: 13pt; mso-line-height-rule: exactly; mso-element: frame; mso-element-frame-hspace: 9.0pt; mso-element-wrap: around; mso-element-anchor-vertical: paragraph; mso-element-anchor-horizontal: margin; mso-element-left: -3.6pt; mso-element-top: 4.7pt; mso-height-rule: exactly; mso-char-indent-count: .5; mso-char-indent-size: 14.0pt;"><span lang="EN-US" style="FONT-SIZE: 14pt; FONT-FAMILY: –¬ΥΈσw; mso-bidi-font-family: ΥΈσw-18030;">2ΓΔCadence ΙΛΨΏΚÜ(ji®Θn)ΫιΘΜ

</span>

<p class="MsoNormal" style="MARGIN: 0cm 0cm 0pt; TEXT-INDENT: 7pt; LINE-HEIGHT: 13pt; mso-line-height-rule: exactly; mso-element: frame; mso-element-frame-hspace: 9.0pt; mso-element-wrap: around; mso-element-anchor-vertical: paragraph; mso-element-anchor-horizontal: margin; mso-element-left: -3.6pt; mso-element-top: 4.7pt; mso-height-rule: exactly; mso-char-indent-count: .5; mso-char-indent-size: 14.0pt;"><span lang="EN-US" style="FONT-SIZE: 14pt; FONT-FAMILY: –¬ΥΈσw; mso-bidi-font-family: ΥΈσw-18030;">3ΓΔIbisΡΘ–ΆΫβΉx“‘ΦΑ»γΚΈΉ‘÷ΤΡΘ–ΆΘΜ

</span>

<p class="MsoNormal" style="MARGIN: 0cm 0cm 0pt; TEXT-INDENT: 7pt; LINE-HEIGHT: 13pt; mso-line-height-rule: exactly; mso-element: frame; mso-element-frame-hspace: 9.0pt; mso-element-wrap: around; mso-element-anchor-vertical: paragraph; mso-element-anchor-horizontal: margin; mso-element-left: -3.6pt; mso-element-top: 4.7pt; mso-height-rule: exactly; mso-char-indent-count: .5; mso-char-indent-size: 14.0pt;"><span lang="EN-US" style="FONT-SIZE: 14pt; FONT-FAMILY: –¬ΥΈσw; mso-bidi-font-family: ΥΈσw-18030;">4ΓΔ”ΟΉςΖ¬’φ¨ç(sh®Σ)άΐΒΡΡ≥ΨW(w®Θng)Ϋj(lu®Α)ΧéάμΤςΗΏΥΌÜΈΑε«ι¦rΫιΫBΘΜ ΑΗάΐΖ÷Έω

</span>

<p class="MsoNormal" style="MARGIN: 0cm 0cm 0pt; LINE-HEIGHT: 13pt; mso-line-height-rule: exactly; mso-element: frame; mso-element-frame-hspace: 9.0pt; mso-element-wrap: around; mso-element-anchor-vertical: paragraph; mso-element-anchor-horizontal: margin; mso-element-left: -3.6pt; mso-element-top: 4.7pt; mso-height-rule: exactly;"><b style="mso-bidi-font-weight: normal;"><span style="FONT-SIZE: 14pt; FONT-FAMILY: –¬ΥΈσw; mso-bidi-font-family: ΥΈσw-18030;">ΒΎ“ΜΧλœ¬ΈγΘΚ<span lang="EN-US">

“Σœ¬ίdEDA360’ΙΆϊ’™ΈΡΘ§’à(q®Ϊng)?ji®Γn)LÜ• http://www.eda360.com .

ΗΡΉÉΒΡ±Ί“Σ–‘

κm»ΜœϊΌM(f®®i)’Ώ¨Π(du®§)ΗΏΦâ(j®Σ)“Τ³”(d®Αng)”΄(j®§)Υψ‘O(sh®®)²δ≈cΤδΥϊΗΏ–‘ΡήκäΉ”‘O(sh®®)²δΒΡ–η«σΖ«≥Θσ@»ΥΘ§Ώ@–©°a(ch®Θn)ΤΖΒΡι_Αl(f®Γ)ΖΫ Ϋ’ΐ‘ΎΕσöΔ°î(d®Γng)ΫώΦΦ–g(sh®¥)ΥυΡή¨ç(sh®Σ)§F(xi®Λn)ΒΡ³™(chu®Λng)–¬ΓΘΗυ™ΰ(j®¥)²ςΫy(t®·ng)ΒΡ¥Ι÷±Ζ÷ΙΛ Ϋι_Αl(f®Γ)ΖΫΖ®Θ§ Ήœ»ι_Αl(f®Γ)ΒΡ «”≤Φΰ≈c≤ΌΉςœΒΫy(t®·ng)Θ®OSΘ©Θ§»ΜΚσΧμΦ”ëΣ(y®©ng)”Ο≥Χ–ρΓΘ”≤Φΰ≈c≤ΌΉςœΒΫy(t®·ng)Άξ»ΪΦ·≥…ΚσΘ§ëΣ(y®©ng)”Ο≥Χ–ρ±Μœό÷Τ”ΎΜυ±ΨΒΡή¦”≤ΦΰΤΫ≈_(t®Δi)÷°÷–ΓΘ

¥ΥΆβΘ§άœ≈ΤΒΡκäΉ”ΙΪΥΨ’ΐ ήΒΫ–¬ΏM(j®§n)Τσ‰I(y®®)ΒΡèä(qi®Δng)ΝΠΧτëπ(zh®Λn)ΘΚΥϊ²É’ΐ‘ΎΗΡΉÉ”Έëρ“é(gu®©)³tΘ§ΉΔ÷Ί³™(chu®Λng)–¬≈cëΣ(y®©ng)”Ο≥Χ–ρΒΡ≤ν°êΜ·ΓΘ»γΫώΏ@–©–¬ΏM(j®§n)Τσ‰I(y®®)“Σ«σΑκ¨ß(d®Θo)σwΙ©ëΣ(y®©ng)…ΧΧαΙ©ΓΑΏm“ΥëΣ(y®©ng)”Ο≥Χ–ρΓ±ΒΡΤΫ≈_(t®Δi)Θ§”≤Φΰ≈cή¦ΦΰΕΦ“ΣΏmΚœΧΊΕ®ΒΡëΣ(y®©ng)”ΟΘ§άΐ»γ“Τ³”(d®Αng)”΄(j®§)ΥψΓΘEDA360‘Ύ°a(ch®Θn)‰I(y®®)σwœΒÉ»(n®®i)÷±Ϋ”ëΣ(y®©ng)¨Π(du®§)Ώ@ΖNόD(zhu®Θn)–ΆΘ§Χα≥ωΝΥ“ΜΖNëΣ(y®©ng)”Ορ¨(q®±)³”(d®Αng) Ϋι_Αl(f®Γ)ΡΘ ΫΘ§”≤Φΰ «ûι³”(d®Αng)ëB(t®Λi)ùMΉψëΣ(y®©ng)”Ο≥Χ–ρΒΡ–η“ΣΕχ‘O(sh®®)”΄(j®§)ΚΆι_Αl(f®Γ)ΒΡΓΘ

ΓΑΉςûι“ΜΦ“èΡ ¬°a(ch®Θn)‰I(y®®)Ϋ¦(j®©ng)ùζ(j®§)≈cΦΦ–g(sh®¥)όD(zhu®Θn)–ΆΤσ‰I(y®®)ΒΡ³™(chu®Λng) Φ»ΥΘ§Έ“²É?y®≠u)ιî?sh®¥)“‘ΑΌ»f(w®Λn)”΄(j®§)ΒΡ»Υ»ΚΧαΙ©ôC(j®©)”ωΘ§Έ““Μ÷±ΕΦ‘Ύ”^≤λΤδΥϊ»ΥΒΡ≈e³”(d®Αng)Θ§Γ±O(ji®Γn)ne Laptop per ChildΘ®ΟΩ²Ä(g®®)ÉΚΆ·“Μ≈_(t®Δi)ΙP”¦±ΨκäΡXΘ©ΙΪΥΨ³™(chu®Λng) Φ»ΥΦφ÷ςœ·Nicholas Negroponte’fΓΘΓΑCadence™μ”–Ω…ΡήόD(zhu®Θn)ΉÉΈΔΧéάμΤς°a(ch®Θn)‰I(y®®)ΡΥ÷ΝœϊΌM(f®®i)κäΉ”ΒΡΫ¦(j®©ng)ùζ(j®§)ΚΆ±μ§F(xi®Λn)ΒΡ‘ΗΨΑΚΆΡΘ ΫΓΘEDA360Ος¥_÷Η≥ωΝΥ“Μ²Ä(g®®)÷ΒΒΟξP(gu®Γn)ΉΔΒΡΏh(yu®Θn)ΨΑΓΘΓ±

ΝΔΦ¥––³”(d®Αng)Τπ¹μ(l®Δi)ΘΚCadenceΆΊ’ΙΚœΉςΘ§ΆΤ≥ω÷ß≥÷EDA360ΒΡ–¬°a(ch®Θn)ΤΖ

ûι÷ß≥÷‘™‰I(y®®)ΫγΏh(yu®Θn)ΨΑΘ§CadenceΫώΧλΏÄΙΪ≤ΦΝΥ¨ç(sh®Σ)§F(xi®Λn)EDA360ΒΡ≥θ≤Ϋ≈e¥κΓΣΓΣîU(ku®Α)’ΙΦΦ–g(sh®¥)ΚœΉςΘ§ΆΤ≥ω–¬°a(ch®Θn)ΤΖœΒΝ–Θ§¥ΌΏM(j®§n)‘™ΦΦ–g(sh®¥)‘Ύ‘O(sh®®)”΄(j®§)÷–ΒΡèVΖΚ≤…”ΟΘ§≤Δι_Αl(f®Γ)³™(chu®Λng)–¬‘O(sh®®)²δΓΘΏ@–©≈e¥κΑϋά®ΘΚ

œΒΫy(t®·ng)¨ç(sh®Σ)§F(xi®Λn)ΒΡσwœΒ ΫΖΫΖ®

”…”ΎëΣ(y®©ng)”Ο¨ß(d®Θo)œρ–ΆœΒΫy(t®·ng)‘O(sh®®)”΄(j®§)Ή¨”ΟëτΡήâρΫβ¦Q‰OΤδèΆ(f®¥)κs≈cάßκyΒΡ»Έ³’(w®¥)Θ§¦]”–ΡΡΦ“ΙΪΥΨΡήâρΧαΙ©Υυ”–±Ί“ΣΒΡΙΛΨΏΆξ»Ϊ’ϊΚœœΒΫy(t®·ng)ΒΡ”≤Φΰ≈cή¦ΦΰΫMΦΰΓΘEDA360ΒΡ“Μ²Ä(g®®)ξP(gu®Γn)φI‘≠³t «–η“Σ“Μ²Ä(g®®)σwœΒΘ§ΡήâρΉ¨ΩΆëτ‘ΎΟφ≈R°î(d®Γng)«Α≈cΈ¥¹μ(l®Δi) –àω(ch®Θng)ΒΡ±Ί»ΜΧτëπ(zh®Λn)ïr(sh®Σ) ή“φΓΘΉςûιEDA360½lΩν÷–ξP(gu®Γn)”ΎΓΑœΒΫy(t®·ng)¨ç(sh®Σ)§F(xi®Λn)Γ±Ώ@“Μ≥–÷ZΒΡΒΎ“Μ≤ΫΘ§Cadence≈cWind RiverΫώΧλ–ϊ≤ΦΏM(j®§n)––ΦΦ–g(sh®¥)ΚœΉςΘ§ΡΩ‰Υ(bi®Γo) «’ϊΚœCadence Incisive Software ExtensionsΚΆWind RiverΒΡSimicsΧ™îMΤΫ≈_(t®Δi)ΓΘ‘Ύ…–üo(w®≤)”≤ΦΰΩ…”Ο÷°«ΑΘ§Ώ@ΖNΚœΉςΖΫ ΫνA(y®¥)”΄(j®§)Ω…Ή¨ΙΛ≥Χéü‘ΎΧ™îMΤΫ≈_(t®Δi)…œι_Αl(f®Γ)κäΉ”‘O(sh®®)”΄(j®§) Θ§≤Δ«“ΧαΗΏœΒΫy(t®·ng)ΙΛ≥Χéü‘Ύ“é(gu®©)³ùΓΔΙήάμΓΔΦΛ³ν(l®§)ΓΔôz≤ι≈c±O(ji®Γn)ΩΊ≤ΜΆ§ή¦”≤Φΰ”ΟάΐΖΫΟφΒΡ–ß¬ ΓΘΏ@ΖN≥ΧΕ»ΒΡΚœΉς¨Π(du®§)”ΎΧαΗΏœΒΫy(t®·ng)Φâ(j®Σ)ΏM(j®§n)Ε»Ω…νA(y®¥)€y(c®®)–‘ΖΫΟφ÷ΝξP(gu®Γn)÷Ί“ΣΘ§Ά§ïr(sh®Σ)Ω…“‘ΫΒΒΆοL(f®Ξng)κU(xi®Θn)Θ§Ώ@ «CadenceœΒΫy(t®·ng)¨ç(sh®Σ)§F(xi®Λn)σwœΒ÷–Έ¥¹μ(l®Δi)ΕύΉΎΚœΉςΆΕΌYΒΡΒΎ“Μ≤ΫΓΘ

ΓΑκäΉ”°a(ch®Θn)‰I(y®®)–η“ΣΏmëΣ(y®©ng)–¬Ψ÷³ί(sh®§)≤≈Ρήά^άm(x®¥)ΤδΏ^»Ξ30ΕύΡξ¹μ(l®Δi)ΒΡΦΛΏM(j®§n)³™(chu®Λng)–¬Θ§Γ±Wind River Ήœ·ëπ(zh®Λn)¬‘ΙΌΦφSimics≤ΩιTΩ²Ϋ¦(j®©ng)άμVincent Rerolle’fΓΘΓΑ“ΜΖNΚœΉς–ΆσwœΒ ΫΖΫΖ®Θ§Ή¨‘O(sh®®)”΄(j®§)àF(tu®Δn)ξ†(du®§)ΡήâρΧτΏxΉνΏmΚœΤδΧΊΕ®–η“ΣΒΡΫMΦΰΘ§Ώ@ «¨ç(sh®Σ)§F(xi®Λn)ι_Ζ≈ Ϋ‰Υ(bi®Γo)€ (zh®≥n)–ΆΫβ¦QΖΫΑΗΒΡ±Ί“Σ“Σ«σΘ§ΡήâρΫβ¦Q≥…±ΨÜ•ν}Θ§¨Δάϊùô(r®¥n)Ήν¥σΜ·ΓΘCadenceœΒΫy(t®·ng)–Ά°a(ch®Θn)ΤΖ≈cSimicsΒΡΫY(ji®Π)ΚœûιœΒΫy(t®·ng)ι_Αl(f®Γ)ΒΡΥυ”–ΖΫΟφΧαΙ©ΝΥ“Μ²Ä(g®®)’φ¨ç(sh®Σ)ΒΡΧ™îMΤΫ≈_(t®Δi)ΓΘΓ±

Cadenceρû(y®Λn)ΉC”΄(j®§)ΥψΤΫ≈_(t®Δi)

–«ΤΎ“ΜΘ§ΙΪΥΨΙΪ≤ΦΝΥ‰I(y®®)ΫγΒΎ“Μ²Ä(g®®)Άξ»ΪΦ·≥…ΒΡΗΏ–‘Ρήρû(y®Λn)ΉC”΄(j®§)ΥψΤΫ≈_(t®Δi)Θ§ΟϊûιPalladium XPΘ§Υϋ‘Ύ“Μ²Ä(g®®)Ϋy(t®·ng)“ΜΒΡρû(y®Λn)ΉC≠h(hu®Δn)Ψ≥÷–Φ·≥…ΝΥΡΘîMΓΔΦ”ΥΌ≈cΖ¬’φΓΘΏ@ΖNΗΏΕ»Ω…îU(ku®Α)’ΙΒΡPalladium XPρû(y®Λn)ΉC”΄(j®§)ΥψΤΫ≈_(t®Δi) «ûιΝΥ÷ß≥÷œ¬“Μ¥ζ‘O(sh®®)”΄(j®§)Εχι_Αl(f®Γ)ΒΡΘ§Ή¨‘O(sh®®)”΄(j®§)≈cρû(y®Λn)ΉCàF(tu®Δn)ξ†(du®§)ΡήâρΗϋΩλΒΊΆξ…ΤΥϊ²ÉΒΡή¦”≤Φΰ≠h(hu®Δn)Ψ≥Θ§‘ΎΗϋΕΧΒΡïr(sh®Σ)ιgÉ»(n®®i)…ζ°a(ch®Θn)≥ωΗϋΗΏΌ|(zh®§)ΝΩΒΡ«Ε»κ ΫœΒΫy(t®·ng)ΓΘ

Cadence? Palladium? XP ΉνΗΏ÷ß≥÷20É|ιTΒΡ‘O(sh®®)”΄(j®§)ΫY(ji®Π)‰΄(g®Αu)Θ§ΧαΙ©ΒΡ–‘ΡήΉνΗΏΩ…Ώ_(d®Δ)4MHz≤Δ÷ß≥÷ΉνΕύ512Οϊ”ΟëτΆ§ïr(sh®Σ) Ι”ΟΓΘ‘™ΤΫ≈_(t®Δi)ΏÄΧαΙ©ΝΥΣö(d®≤)ΧΊΒΡœΒΫy(t®·ng)Φâ(j®Σ)Ϋβ¦QΖΫΑΗΘ§Αϋά®ΒΆΙΠΚΡΖ÷Έω≈c÷Η‰Υ(bi®Γo)ρ¨(q®±)³”(d®Αng) Ϋρû(y®Λn)ΉCΓΘ

Palladium XPρû(y®Λn)ΉC”΄(j®§)ΥψΤΫ≈_(t®Δi)ûιι_Αl(f®Γ)’ΏΧαΙ©ΝΥΤδ‘O(sh®®)”΄(j®§)ΒΡΗΏ±Θ’φΟηάL(high-fidelity representation)Θ§Ή¨Υϊ²ÉΡήâρ―ΗΥΌΕχ”–Α―Έ’ΒΊ’“ΒΫ≤Δ–όèΆ(f®¥)εe(cu®Α)’`Θ§èΡΕχΒΟΒΫΗϋΗΏΌ|(zh®§)ΝΩΒΡIPΓΔΉ”œΒΫy(t®·ng)ΓΔSoCΚΆœΒΫy(t®·ng)ΓΘ‘O(sh®®)”΄(j®§)àF(tu®Δn)ξ†(du®§)Ω…“‘Ηυ™ΰ(j®¥)–η“Σ‘ΎΩ…îU(ku®Α)’ΙΒΡρû(y®Λn)ΉC≠h(hu®Δn)Ψ≥÷–¨ΔΡΘîM≈cΦ”ΥΌΚΆΖ¬’φΏM(j®§n)––ΓΑüαΫΜ™Q(hot-swap)Γ±Θ§Ώ@‰”Ω…“‘Φ”Ωλρû(y®Λn)ΉCΏ^≥ΧΘ§≤Δ«“Ω…“‘Ηϋ‘γΒΊ€y(c®®)‘΅«Ε»κ Ϋή¦ΦΰΘ§≤Δ«“‘u(p®Σng)Ιά≤ΜΆ§IP≈cœΒΫy(t®·ng)Φή‰΄(g®Αu)ΒΡ–‘ΡήΆΤîύΓΘ

ΓΑΫώΧλΘ§Ακ¨ß(d®Θo)σwΙΪΥΨ±Ίμö“ΣΆ§ïr(sh®Σ)…ΟιL(zh®Θng)”Ύή¦”≤ΦΰΘ§ΕχΡ«–©üo(w®≤)Ζ®≥§‘Ϋ²ςΫy(t®·ng)”…ΡΠ†•Ε®¬…ρ¨(q®±)³”(d®Αng)ΒΡ³™(chu®Λng)–¬¨Δïΰ(hu®§) ήΒΫ‰O¥σΒΡ¦_™τΘ§Γ±CadenceΩ²≤ΟΦφ Ήœ·àΧ(zh®Σ)––ΙΌLip-Bu Tan’fΓΘΓΑEDA360 «’ϊ²Ä(g®®)°a(ch®Θn)‰I(y®®)ΒΡ––³”(d®Αng)≥ΪΉhΓΘΈ“²ÉΒΡΩΆëτ’ΐΟφ≈RΡΑ…ζΒΡΓΔ‰OΤδèΆ(f®¥)κsΒΡΧτëπ(zh®Λn)Θ§Έ“²É±ΊμöΚœΉς“‘ΧαΙ©Ρή¥_±Θ≥…ΙΠΒΡœ»ΏM(j®§n)ΦΦ–g(sh®¥)≈cΫβ¦QΖΫΑΗΓΘ“ρ¥ΥΘ§Cadence¨Δïΰ(hu®§)àΧ(zh®Σ)––Μυ”Ύ…νΚώΩΆëτΜοΑιξP(gu®Γn)œΒΒΡEDA360ëπ(zh®Λn)¬‘Θ§“‘Ϋβ¦QΈ“²É––‰I(y®®)ΥυΟφ≈R

]]>Cadence OrCAD 15.7,

Ή¨PCBΒΡ‘O(sh®®)”΄(j®§)ΏM(j®§n)»κΗϋΦö(x®§)Ιù(ji®Π)κAΕΈΓΘ≈cPSpiceΫY(ji®Π)ΚœΩ…ëΣ(y®©ng)”Ο”Ύ‘ΎAllegroΤΫ≈_(t®Δi)…œΓΘ¥ΥΧΉΫMœΒûι“ΜΆξ’ϊΚ≠…w«ΑΕΥ÷ΝΚσΕΥΓΔ Ι”ΟΈΔή¦“ï¥ΑΤΫ≈_(t®Δi)ΒΡΝς≥ΧΘ§Ω…“‘Ι©”ΓΥΔκä¬ΖΑε(PCB)

‘O(sh®®)”΄(j®§)éüΆΗΏ^ΙΛΨΏ’ϊΚœ≈c≥Χ ΫΉ‘³”(d®Αng)Μ·ΗΡ…Τ…ζ°a(ch®Θn)ΝΠ≈cΩsΕΈΏM(j®§n)»κ –àω(ch®Θng)ΒΡïr(sh®Σ)ιgΓΘ Orcad Unison Suite

’ϊΚœΝΥΥΡΖN–¬ΫϋΦ”èä(qi®Δng)–ΆΒΡ°a(ch®Θn)ΤΖΘ§‘ΎÜΈ“ΜΧΉ―bή¦σw°î(d®Γng)÷–Φ¥Ω…ΧαΙ©‘O(sh®®)”΄(j®§)éüΥυ–ηΒΡΥυ”–ΙΛΨΏΓΘ

OrCAD 15.7 Αϋά®Ι©‘O(sh®®)”΄(j®§)ίî»κΒΡOrcad CaptureR Θ§Ι©νê±»≈cΜλΚœ”çΧ•(h®Λo)ΡΘîM”ΟΒΡ PSpiceR A/D

BasicsΘ§Ι©κä¬ΖΑε‘O(sh®®)”΄(j®§)ΒΡ Orcad LayoutR “‘ΦΑΙ©ΗΏΟήΕ»κä¬ΖΑεΉ‘³”(d®Αng)ά@ΨÄΒΡSPECCTRAR

4UΓΘ–¬Φ”»κΒΡSPECCTRAΘ§”Ο“‘÷ß‘°‘O(sh®®)”΄(j®§)»’“φèΆ(f®¥)κsΒΡΗςΖNΗΏΥΌΓΔΗΏΟήΕ»”ΓΥΔκä¬ΖΑε‘O(sh®®)”΄(j®§)ΓΘSPECCTRA

ΧαΙ©‘O(sh®®)”΄(j®§)éü“ΜΖN“‘–Έ†νûιΜυΒA(ch®≥)ΒΡΘ§ΙΠΡήèä(qi®Δng)¥σΒΡά@ΨÄΤςΘ§Ω…‘Ύ€p…Ό Ι”Ο’ΏΫι»κ«ι¦rœ¬Άξ≥…ΗςΖNèΆ(f®¥)κs‘O(sh®®)”΄(j®§)ΓΘ

OrCAD PCB Design Tools

The Cadence OrCAD product line includes affordable, high-performance

PCB design tools that boost productivity for smaller design teams

and individual PCB designers.

To stay competitive in today's market, engineers must take a design

from engineering through manufacturing with shorter design cycles

and faster time to market. To be successful, you need a set of

powerful, intuitive, and integrated tools that work seamlessly

across the entire design flow.

Cadence OrCAD personal productivity tools (including Cadence PSpice)

have a long history of addressing these demands. Designed to boost

productivity for smaller design teams and individual PCB designers,

OrCAD PCB design suites grow with your needs and technology

challenges. The powerful, tightly integrated PCB design suites

include design capture, librarian tools, a PCB editor, an

auto/interactive router, and optional analog and mixed-signal

simulator.

The affordable, high-performance OrCAD product line is easily

scalable with the full complement of Cadence Allegro PCB solutions.

The OrCAD product line is supported by a worldwide network of

Cadence Channel Partners. For sales, technical support, and training

inquiries please visit the global Cadence Channel Partner listing to

find a partner in your region.]]>

OrCAD PCB Designer with PSpiceΘ§F(xi®Λn)ull featured suites with time-proven and new OrCAD technologyΘ§»ΪΙΠΡή‘ωèä(qi®Δng)ΧΉΦΰΘ§ΨΏ”–”¦ïr(sh®Σ)ρû(y®Λn)ΉCΙΠΡή“‘ΦΑ–¬OrCADΦΦ–g(sh®¥)ΘΓ «ΡΩ«Αûι÷ΙOrCADΙΠΡήΉνèä(qi®Δng)¥σΒΡ“Μ²Ä(g®®)Αφ±ΨΓΘ

Cadence OrCAD 16.0, Ή¨PCBΒΡ‘O(sh®®)”΄(j®§)ΏM(j®§n)»κΗϋΦö(x®§)Ιù(ji®Π)κAΕΈΓΘ≈cPSpiceΫY(ji®Π)ΚœΩ…ëΣ(y®©ng)”Ο”Ύ‘ΎAllegroΤΫ≈_(t®Δi)…œΓΘ¥ΥΧΉΫMœΒûι“ΜΆξ’ϊΚ≠…w«ΑΕΥ÷ΝΚσΕΥΓΔ Ι”ΟΈΔή¦“ï¥ΑΤΫ≈_(t®Δi)ΒΡΝς≥ΧΘ§Ω…“‘Ι©”ΓΥΔκä¬ΖΑε(PCB) ‘O(sh®®)”΄(j®§)éüΆΗΏ^ΙΛΨΏ’ϊΚœ≈c≥Χ ΫΉ‘³”(d®Αng)Μ·ΗΡ…Τ…ζ°a(ch®Θn)ΝΠ≈cΩsΕΈΏM(j®§n)»κ –àω(ch®Θng)ΒΡïr(sh®Σ)ιgΓΘ Orcad Unison Suite ’ϊΚœΝΥΥΡΖN–¬ΫϋΦ”èä(qi®Δng)–ΆΒΡ°a(ch®Θn)ΤΖΘ§‘ΎÜΈ“ΜΧΉ―bή¦σw°î(d®Γng)÷–Φ¥Ω…ΧαΙ©‘O(sh®®)”΄(j®§)éüΥυ–ηΒΡΥυ”–ΙΛΨΏΓΘΫMΚœΗςμ½(xi®Λng)°a(ch®Θn)ΤΖΒΡ±ΨΧΉΫMΕ®Ér(ji®Λ)US$5,995 (ÖΔΩΦ”Ο), ±»Ζ÷³eΌè(g®Αu)ΌIÜΈμ½(xi®Λng)°a(ch®Θn)ΤΖΩ…Ιù(ji®Π) Γ“ΜΑκ“‘…œΒΡΌM(f®®i)”ΟΓΘ

OrCAD 16.0 Αϋά®Ι©‘O(sh®®)”΄(j®§)ίî»κΒΡOrcad CaptureR Θ§Ι©νê±»≈cΜλΚœ”çΧ•(h®Λo)ΡΘîM”ΟΒΡ PSpiceR A/D BasicsΘ§Ι©κä¬ΖΑε‘O(sh®®)”΄(j®§)ΒΡ Orcad LayoutR “‘ΦΑΙ©ΗΏΟήΕ»κä¬ΖΑεΉ‘³”(d®Αng)ά@ΨÄΒΡSPECCTRAR 4UΓΘ–¬Φ”»κΒΡSPECCTRAΘ§”Ο“‘÷ß‘°‘O(sh®®)”΄(j®§)»’“φèΆ(f®¥)κsΒΡΗςΖNΗΏΥΌΓΔΗΏΟήΕ»”ΓΥΔκä¬ΖΑε‘O(sh®®)”΄(j®§)ΓΘSPECCTRA ΧαΙ©‘O(sh®®)”΄(j®§)éü“ΜΖN“‘–Έ†νûιΜυΒA(ch®≥)ΒΡΘ§ΙΠΡήèä(qi®Δng)¥σΒΡά@ΨÄΤςΘ§Ω…‘Ύ€p…Ό Ι”Ο’ΏΫι»κ«ι¦rœ¬Άξ≥…ΗςΖNèΆ(f®¥)κs‘O(sh®®)”΄(j®§)ΓΘ

‘™ΙΪΥΨCadenceR PCBœΒΫy(t®·ng)≤Ω²ÉΒΡ≤Ώ¬‘––δN≤ΩΗ±Ω²≤ΟJamie Metcalfe±μ Ψ"Cadence OrCAD Suite 10.5ΧαΙ©“Μ–©ΝΥ≤ΜΤπΒΡΩΤΦΦΘ§Εχ έÉr(ji®Λ) «²Ä(g®®)»ΥΙΛ≥Χéü‘O(sh®®)”΄(j®§) –àω(ch®Θng)÷–ΟΩ“ΜΈΜΕΦΡήΊ™(f®¥)™ζ(d®Γn)ΒΟΤπΒΡΓΘΫε÷χΑl(f®Γ)––¥Υ“Μή¦σwΘ§±ΨΙΪΥΨûι¥Υ“Μ –àω(ch®Θng)Ö^(q®±)Ητ÷–ΒΡÉr(ji®Λ)Ηώ/–‘Ρή÷ΤΕ®ΝΥ–¬ΒΡ‰Υ(bi®Γo)€ (zh®≥n)"ΓΘ

Cadence OrCAD Suite With PSpice V10.5–¬ΙΠΡήξP(gu®Γn)φIΗϋ–¬ΘΚ

OrCAD Capture, ΨΏ”–ΩλΫίΓΔΆ®”ΟΒΡ‘O(sh®®)”΄(j®§)ίî»κΡήΝΠΘ§ ΙOrCAD Capture‘≠άμàDίî»κœΒΫy(t®·ng)≥…ûι»Ϊ«ρΖΕ΅ζÉ»(n®®i)èV ήög”≠ ΒΡ‘O(sh®®)”΄(j®§)ίî»κΙΛΨΏΓΘΥϋቨΠ(du®§)‘O(sh®®)”΄(j®§)“Μ²Ä(g®®)–¬ΒΡΡΘîMκä¬ΖΓΔ–όΗΡ§F(xi®Λn)”–ΒΡ“Μ²Ä(g®®)PCBΒΡ‘≠άμàDΘ§Μρ’ΏάL÷Τ“Μ²Ä(g®®)HDLΡΘâKΒΡΖΫΩρ àDΘ§ΕΦΧαΙ©ΝΥΡψΥυ–η“ΣΒΡ»Ϊ≤ΩΙΠΡήΘ§≤Δ«“Ω…“‘―ΗΥΌΒΊρû(y®Λn)ΉCΡψΒΡ‘O(sh®®)”΄(j®§)ΓΘOrCAD CaptureΉςûι‘O(sh®®)”΄(j®§)ίî»κΙΛΨΏΘ§ΥϋΏ\(y®¥n)––‘ΎPCΤΫ≈_(t®Δi)Θ§”Ο”ΎFPGAΓΔPCBΚΆPSpice‘O(sh®®)”΄(j®§)ëΣ(y®©ng)”Ο÷–ΓΘΥϋ «‰I(y®®)ΫγΒΎ“Μ²Ä(g®®)’φ’ΐΜυ”ΎWindows≠h(hu®Δn)Ψ≥ΒΡ‘≠άμàDίî»κ≥Χ–ρΓΘCapture“Ή”Ύ Ι”ΟΒΡΙΠΡήΚΆΧΊϋc(di®Θn) ΙΤδ“―Ϋ¦(j®©ng)≥…ûιΝΥ‘≠άμàDίî»κΒΡΙΛ‰I(y®®)‰Υ(bi®Γo)€ (zh®≥n)ΓΘ

OrCAD PCB Editor, ¬îΟςΒΡ≤ΦΨÄ≠h(hu®Δn)Ψ≥, ΖΫ±ψΒΡ…ζ°a(ch®Θn)Ϋ”ΩΎ,OrCAD PCB Editor «OrCAD PCB DesignerΉν÷ς“ΣΚΆΉνèä(qi®Δng)¥σΒΡΚΥ–ΡΙΛΨΏ,“≤ «”… άΫγΉνœ»ΏM(j®§n)ΒΡCadence / Allegroκä¬ΖΑε‘O(sh®®)”΄(j®§)œΒΫy(t®·ng)Υυ―–Αl(f®Γ). OrCAD PCB Editor «“Μ²Ä(g®®)”Ο¹μ(l®Δi)Ϋ®ΝΔΦΑάL÷ΤèΆ(f®¥)κsΕύ¨”ΒΡκä¬ΖΑε‘O(sh®®)”΄(j®§)ΤΫ≈_(t®Δi). ΕχΩ…îU(ku®Α)èàΒΡΙΠΡήΏxμ½(xi®Λng) ΙΥϊ¨Π(du®§)”Ύ§F(xi®Λn)Ϋώ –Οφ…œΒΡ‘O(sh®®)”΄(j®§)ΦΑ…ζ°a(ch®Θn)–η«σΕΦΡήâρΚΆΆξ»ΪΖϊΚœ.≤ΔΡήΑ≤–ΡΟφ¨Π(du®§)Έ¥¹μ(l®Δi)ΒΡΧτëπ(zh®Λn)ΓΘ

SPECCTRA for OrCAD , SPECCTRA « –Οφ…œΉνœ»ΏM(j®§n)ΒΡΉ‘³”(d®Αng)ΦΑ ÷³”(d®Αng)≤ΦΨÄή¦Φΰ.ΥϊΡήâρ≈cOrCAD PCB Editor≥δΖ÷ΫY(ji®Π)Κœ, ΡζΡή¨Δκä¬ΖΑε…θ÷Ν «ΨĬΖàD…œΥυΕ®ΝxΒΡÖΔîΒ(sh®¥)ΦΑ‘O(sh®®)”΄(j®§)–ϊΗφ?zh®®n)ς¨?d®Θo)÷ΝSPECCTRA. É»(n®®i)Ϋ®ΒΡΉ‘³”(d®Αng)≤ΦΨÄή¦ΦΰΒΡΩ…Ά§ïr(sh®Σ)6 ²Ä(g®®)”çΧ•(h®Λo)¨”ΉΏΨÄΕχΝψΦΰΫ”ϋc(di®Θn)îΒ(sh®¥)≤Μœό, »γΙϊΡψ“ΣΒΡΆ§ïr(sh®Σ)Ή‘³”(d®Αng)≤ΦΨÄΒΡ¨”îΒ(sh®¥)ί^Εύ,ΡζΩ…“‘”Οœύ°î(d®Γng)Ϋ¦(j®©ng)ùζ(j®§)ΒΡÉr(ji®Λ)Ηώ…ΐΦâ(j®Σ)ΒΫ ΤδΥϋΒΡΒ»Φâ(j®Σ)ΒΟΒΫΉν¥σΒΡ–ß“φΓΘ

PSpice A/D (included in OrCAD with PSpice v16.0) PSpice «“Μ²Ä(g®®)»ΪΙΠΡήΒΡΡΘîM≈cΜλΚœ–≈Χ•(h®Λo)Ζ¬’φΤςΘ§Υϋ÷ß≥÷èΡΗΏνlœΒΫy(t®·ng)ΒΫΒΆΙΠΚΡIC‘O(sh®®)”΄(j®§)ΒΡκä¬Ζ‘O(sh®®)”΄(j®§)ΓΘPSpiceΒΡΖ¬’φΙΛΨΏ“―ΚΆ OrCAD CaptureΦΑConcept HDLκä¬ΖΨéί΄ΙΛΨΏ’ϊΚœ‘Ύ“ΜΤπΘ§Ή¨ΙΛ≥ΧéüΖΫ±ψΒΊ‘ΎÜΈ“ΜΒΡ≠h(hu®Δn)Ψ≥άοΫ®ΝΔ‘O(sh®®)”΄(j®§)ΓΔΩΊ÷ΤΡΘîMΦΑΒΟΒΫΫY(ji®Π)ΙϊΓΘ

Cadence‘™ΙΪΥΨ‘Ύ»A ΔνD»πΦΣΖΤΒ¬ΒΡ“ΜΈΜΉς”ΓΥΔκä¬ΖΑε‘΅”΄(j®§)ΒΡνôÜ• (°a(ch®Θn)ΤΖ…œ –«Α ΉςΒΎΕΰκAΕΈΊêΥΰ€y(c®®)) Kris Nelson’J(r®®n)ûι"OrCAD 16.0÷–ΒΡΥΡ¨”ΑεSPECCTRA Ή‘³”(d®Αng)ά@ΨÄΤς ΙΈ“ΡήâρΫβ¦QΝΥ‘Ύ÷––Γ–Ά‘O(sh®®)”΄(j®§)÷–‘ΎΗΏΟήΕ»ΗΏΨΪΕ»ά@ΨÄïr(sh®Σ)ΥυΟφ≈RΒΡÜ•ν}ΓΘOrcad Layout ≈c SPECCTRA÷°ιg“Μ¥ΈΑ¥φIΦ¥Ω…≤ΌΩΊΒΡΫιΟφΘ§Ω…àΧ(zh®Σ)––κpœρόD(zhu®Θn)Ήg≤ΫσEΒΡΉ‘³”(d®Αng)Μ·≤ΫσE,¥_¨ç(sh®Σ) Γœ¬Έ“ΚήΕύïr(sh®Σ)ιgΓΘ ‘ΌΦ”…œ¥ΥΧΉΫM‘ΎΗςΖNΙΛΨΏ÷°ιgΧαΙ©Άξ’ϊΒΡ«ΑΓΔαα(Ζ¥)‰Υ(bi®Γo)ΉΔΘ§ ΙΈ“‘Ό“≤≤Μ”ΟûιΝΥœκΒΫΉςèUΒΡκä¬ΖΑεΕχκy“‘»κΟΏΓΘ"

::::::English Description::::::

The Cadence OrCAD product line includes affordable, high-performance PCB design tools that boost productivity for smaller design teams and individual PCB designers.To stay competitive in todayΓ·s market, engineers must take a design from engineering through manufacturing with shorter design cycles and faster time to market. To be successful, you need a set of powerful, intuitive, and integrated tools that work seamlessly across the entire design flow.

Cadence? OrCAD? personal productivity tools (including Cadence? PSpice?) have a long history of addressing these demands. Designed to boost productivity for smaller design teams and individual PCB designers, OrCAD PCB design suites grow with your needs and technology challenges. The powerful, tightly integrated PCB design suites include design capture, librarian tools, a PCB editor, an auto/interactive router, and optional analog and mixed-signal simulator.

The affordable, high-performance OrCAD product line is easily scalable with the full complement of Cadence? Allegro? PCB solutions.

The OrCAD product line is supported by a worldwide network of Cadence Channel Partners. For sales, technical support, and training inquiries please visit the global Cadence Channel Partner listing to find a partner in your region.To stay competitive in todayΓ·s market, engineers must take a design from engineering through manufacturing with shorter design cycles and faster time to market. To be successful, you need a set of powerful, intuitive, and integrated tools that work seamlessly from start to finish.

Cadence? OrCAD? personal productivity tools (including Cadence PSpice?) have along history of addressing these demands. Designed to boost productivity for smaller design teams and individual PCB designers, OrCAD PCB design suites grow with your needs and technology challenges. The powerful, tightly integrated PCB design suites include design capture, librarian tools, a PCB editor, an auto/interactive router, and optional analog and mixed-signal simulator. The affordable, high-performance OrCAD product line is easily scalable with the full complement of Cadence Allegro? PCB design technologies.

All OrCAD 16.0 products are now supported in Windows Vista? Enterprise.

New Cadence OrCAD and PSpice Bundle!

Cadence OrCAD EE Designer Plus

OrCAD EE Designer Plus provides powerful schematic entry and simulation in one premium package. This competitively priced, complete front-end design solution includes:

OrCAD Capture schematic entry, the worldΓ·s leading schematic capture tool

PSpice A/D for analog and mixed-signal simulation

PSpice advanced analysis capabilitiesΓΣsensitivity analysis, optimization, Smoke (stress analysis), and Monte Carlo (yield analysis)ΓΣto automatically maximize the performance of circuits

For more information contact us at info@ema-eda.com or call 800-813-7494.

Cadence OrCAD Capture

Improved support for complex hierarchical designs, including better support for occurrence properties and externally referenced designs.

Support for placing and moving text and drawing objects on fine grid independent of connectivity objects

Enhancements to archiving adds an option to include PSpice models in the archive libraries which improves the performance of archived simulation profiles

Improved error messages and DRC engine

Cadence Help Online Documentation System replaces CDSDoc, providing faster invocation time, advanced search capabilities, and built-in viewing window

Usability enhancements and implementation of over 100 CCRs for improved quality and performance

Cadence OrCAD Capture CIS Option

Support for including mechanical parts and assemblies in standard component information system (CIS) Bill of Materials (BOM)

Better support for Japanese characters in CIS

Better BOM generation for non-English operating systems

Cadence PSpice A/D

Improved speed for power electronics designs, especially those using ABM if-then expressions, which will simulate up to 50x faster

CheckPoint Restart feature allows you to save the state of a transient simulation at specific times as CheckPoints. Prior to restarting, you can change component values, so if youΓ·re not getting the results you want, you can tune your circuit without having to restart from the beginning. This is particularly useful for circuits that have a long startup time like a switch mode power supply. You can simulate once to reach steady state, tune the circuit to get the final result you want, and then simulate from the beginning to verify the full simulation. In this situation, CheckPoint Restart can be a significant time saver

Autoconvergence feature allows PSpice to automatically modify convergence options as necessary. This reduces the need for user interaction for problem circuits

Improved transient convergence. Adaptive iteration, improvements in the step time algorithm, and an improved switch model allow PSpice to converge on certain types of problem circuits

Run in resume mode accessible from graphical user interface (GUI)

Minimum step size recalculation

Usability enhancements

Tasks such as adding a trace, adding a plot, zooming the view, or adding a text label are now available using the right mouse button to display a context-sensitive menu in the Probe window

Probe window cursors now display X and Y coordinates on the status bar of the Probe window

Improved simulation speed for E and G device-based circuits

PSpice libraries have 120 new power devices. Updated vendor libraries include 290 new LED models

Cadence Help Online Documentation System replaces CDSDoc, providing faster invocation time, advanced search capabilities, and built-in viewing window

Cadence PSpice AA

PSpice Advanced Analysis support for legacy PSpice models. Traditional tolerance specifications can now be used by the Monte Carlo and Sensitivity tools. This includes the use of PDF custom distributions and device and lot tolerances

Cadence OrCAD PCB Designer (including OrCAD PCB Editor)

OrCAD Layout translator user interface opens from within OrCAD PCB Editor

Cadence Help Online Documentation System replaces CDSDoc, providing faster invocation time, advanced search capabilities, and built-in viewing window

Usability enhancements made within the display canvas and to the command structure

Redesigned color / visibility GUI

Enhancements made to the underlying graphics system, based on OpenGL graphics engine

Physical and spacing constraints incorporated in the Allegro constraint management system

Interactive and automatic controls for component fanout (pin escaping)

Context-sensitive editing paradigm built on selecting database objects first, followed by action command

Cadence OrCAD Layout

Cadence Help Online Documentation System replaces CDSDoc, providing faster invocation time, advanced search capabilities, and built-in viewing window

Support for GerbTool Version 15.0

Implementation of numerous CCRs for improved quality and performance

Please note: The OrCAD 16.0 upgrade will be provided without charge to all current OrCAD customers with active maintenance contracts. If you havenΓ·t received your updated license file and CD by July 23, 2007, or if you have additional questions, please

]]>Cadence ¨W(xu®Π)Νï(x®Σ)ΘΚ

ξP(gu®Γn)”ΎCadenceΒΡïχΦ°≤Μ «ΚήΕύΘ§Έ“Ω¥ΝΥ“‘œ¬éΉ±ΨΘΚ

1ΓΔΓΕCadenceΗΏΥΌκä¬ΖΑε‘O(sh®®)”΄(j®§)≈cΖ¬’φΓΖΘΚïχΚήΚώΘ§É»(n®®i)»ίΉν»ΪΘ§ΒΪΗ–”XΚήΕύ÷±Ϋ”Ζ≠ΉgCadenceΒΡhelpΈΡΦΰΘ§÷Μ÷v‘θΟ¥≤ΌΉςΘ§¦]”–÷v«ε≥ΰûι ≤Ο¥Ώ@Ο¥≤ΌΉςΘ§Έ“÷ς“Σ‘ΎάοΟφ¨W(xu®Π)Νï(x®Σ)ΝΥorCADΘ®CIS,orCAD «Κσ¹μ(l®Δi)±ΜCadence ’Όè(g®Αu)ΒΡΘ§§F(xi®Λn)‘Ύ“―Ϋ¦(j®©ng)±ΜCadence’ϊΚœΏM(j®§n)»ΞΘ§ΚΆΤδΥϊή¦Φΰ¨ç(sh®Σ)§F(xi®Λn)üo(w®≤)ΩpΏBΫ”Θ©ΒΡΜυ±Ψ≤ΌΉςΓΘ

2ΓΔΓΕCadence Concept HDL&&Allegro ‘≠άμàDΚΆPCB‘O(sh®®)”΄(j®§)ΓΖΘΚEDAœ»δhΙΛΉς “≥ωΒΡïχΈ““Μ÷±’J(r®®n)ûι «±»ί^≤Μεe(cu®Α)ΒΡΘ§Ώ@±Ψ“≤≤ΜάΐΆβΘ§ΒΪ «Cadence Concept HDLΘ®HDLΘ©Ώ@²Ä(g®®)‘≠άμàD‘O(sh®®)”΄(j®§)ΙΛΨΏΗ–”X¦]”–orCADΘ®CIS)≤ΌΉς¹μ(l®Δi)ΒΡΖΫ±ψΘ§Υυ“‘Έ“÷ς“ΣèΡΏ@±Ψïχ…œ¨W(xu®Π)Νï(x®Σ)ΝΥAllegroΒΡ≤ΌΉςΘ§±Ψïχ¨Π(du®§)AllegroΒΡ÷vΫβΗ–”X±»…œ“Μ±ΨïχΚΟάμΫβΓΘ

3ΓΔΓΕCadenceΗΏΥΌPCB‘O(sh®®)”΄(j®§)≈cΖ¬’φΖ÷ΈωΓΖΘΚCadenceΙΠΡήèä(qi®Δng)¥σΘ§ΦÉ¥βΒΡ°΄κä¬ΖΑεΙΠΡή÷Μ «ΤδΚή–Γ“Μ≤ΩΖ÷ΙΠΡήΘ§ΤδΏÄΩ…“‘‘ΎΗΏΥΌκä¬Ζ‘O(sh®®)”΄(j®§)Θ§–≈Χ•(h®Λo)Άξ’ϊ–‘Θ®SIΘ©Θ§κä‘¥Άξ’ϊ–‘Θ®PIΘ©Ζ¬’φΒ»ΖΫΟφΑl(f®Γ)™]èä(qi®Δng)¥σΒΡΙΠΡήΘ§Ώ@±Ψïχ…œ…φΦΑΒΫ“Μ≤ΩΖ÷ΗΏΥΌPCBΖ¬’φΒΡÉ»(n®®i)»ίΘ§ïχΒΡΚσΟφéΉ’¬÷vΫβmodel integrityΘ®≤ιΩ¥Θ§Ψéί΄IBISΡΘ–ΆΘ©Θ§PCB SIΘ§SigXploerΒ»ΙΛΨΏΓΘ

4ΓΔ ≥ΐΝΥ“‘…œéΉ±ΨïχΆβΘ§ΨW(w®Θng)…œ“Μ÷±Νς²ς÷χ÷–≈dΙΪΥΨÉ»(n®®i)≤ΩΒΡCadence≈ύ”•(x®¥n)ΫΧ≥ΧΘ§Ι≤5²Ä(g®®)Ζ÷É‘(c®®)ΘΚ‘≠άμàDΖ÷É‘(c®®)Θ§PCB‘O(sh®®)”΄(j®§)Ζ÷É‘(c®®)Θ§Φs χΙήάμΤςΖ÷É‘(c®®)Θ§Ή‘³”(d®Αng)≤ΦΨÄΤςΖ÷É‘(c®®)Θ§Ζ¬’φΖ÷É‘(c®®)Θ§άοΟφΒΡ÷vΫβ“≤Κή‘îΦö(x®§)Θ§ΚήΕύÉ»(n®®i)»ίΕΦ «÷±Ϋ”èΡ¨ç(sh®Σ)κH≥ωΑl(f®Γ)ι_ Φ÷vΫβΘ§–η“ΣΒΡ»ΥΩ…“‘ΫoΈ“Ντ―‘Θ§Έ“ïΰ(hu®§)Αl(f®Γ)Ϋo¥σΦ“ΓΘ

5ΓΔ‘ΎCadenceΒΡ¨W(xu®Π)Νï(x®Σ)÷–Η–”XΏ@éΉ²Ä(g®®)’™â·≤Μεe(cu®Α)ΘΚ

http://www.eda365.com/index.php

http://www.eda365.com/index.php

6ΓΔ‘ΎCadenceΒΡ¨W(xu®Π)Νï(x®Σ)÷–Έ“’J(r®®n)ûι÷ς“Σ“ΣΑ―Έ’“Μœ¬éΉϋc(di®Θn)ΘΚ

aΓΔΚΗ±PΈΡΦΰΒΡΫ®ΝΔΘ®.padΘ©Θ§Ζ÷«ε≥ΰΗςΖNΚΗ±PΒΡÖ^(q®±)³eΘ§‘ΎΗς¨”÷–ΒΡΫY(ji®Π)‰΄(g®Αu)Θ§³²èΡprotel÷±Ϋ”όD(zhu®Θn)–Ά”ΟCadenceΘ§Ώ@“Μϋc(di®Θn)“ΜΕ®“ΣΉΔ“βΓΘœ¬ΟφΫo“Μèà±»ί^‘îΦö(x®§)ΒΡ Ψ“βàDΘ§±ψ”Ύ¥σΦ“άμΫβ

bΓΔΖ÷«ε≥ΰκä¬ΖΑε…œΗς²Ä(g®®)¨”ΒΡΚ§ΝxΘ§“ΜΑψÉ…¨”ΑεΕΦïΰ(hu®§)”–μî¨”Θ®ΒΉ¨”Θ©Ϋz”Γ¨”Θ®silkΘ©Θ§μî¨”Θ®ΒΉ¨”Θ©ΉηΚΗ¨”Θ®soldermaskΘ©Θ®ΉηΚΗ¨”Φ¥ûι‘Ύκä¬ΖΑε…œ≤ΜΥΔΡ«¨”ΨG”ΆΒΡ¨”Θ©Θ§μî¨”Θ®ΒΉ¨”Θ©≤ΦΨĨ”Θ®etchΘ©Θ§ΤδΥϋ¨”Ηυ™ΰ(j®¥)ΨΏσw“Σ«σ‘Ό‘O(sh®®)÷ΟΓΘ

cΓΔCadenceΒΡ≤ΌΉςΕΦ «œ»Ώx≤ΌΉςÉ»(n®®i)»ίΘ§‘ΌΏx≤ΌΉς¨Π(du®§)œσΘ§Ώ@“Μϋc(di®Θn)³²ι_ ΦΚή≤ΜΝï(x®Σ)ëTΘ§”ΟΕύΝΥ“‘ΚσΗ–”XΏ@ «ΥϋΒΡ“Μ²Ä(g®®)Éû(y®≠u)ϋc(di®Θn)ΓΘ

dΓΔΏzΚΕΒΡ“Μϋc(di®Θn) «Cadenceίî≥ωΒΡψ@ΩΉΈΡΦΰ≤Μ÷ß≥÷ôEΩΉΘ®olongΘ©Θ§÷ς“ΣΉ‘ΦΚ°΄Εύ²Ä(g®®)àAΏ^ΩΉ¹μ(l®Δi)ΡΘîMΘ§≤Μ÷ΣΒά”–¦]”–ΤδΥϊΖΫΖ®ΓΘ

œ¬Οφ÷v÷vFPGAΒΡ¨W(xu®Π)Νï(x®Σ)ΘΚ

÷vFPGAΒΡ¨W(xu®Π)Νï(x®Σ)÷°«Α≤ΜΒΟ≤ΜΧα”≤ΦΰΟη ω’Z(y®≥)―‘Θ®HDLΘ©Θ§Έ“÷ς“Σ”ΟΒΡ «Verilog’Z(y®≥)―‘Θ§ΝμΆβ“ΜΖN≥Θ”ΟΒΡΨΆ «VHDL’Z(y®≥)―‘Θ§É…ΖN’Z(y®≥)―‘Ης”–Éû(y®≠u)Ν”Θ§¨Π(du®§)”ΎVerilogΒΡ¨W(xu®Π)Νï(x®Σ)Έ“÷ς“ΣΆΤΥ]“‘œ¬É…±ΨïχΘΚ

1ΓΔΓΕverilog îΒ(sh®¥)Ή÷œΒΫy(t®·ng)‘O(sh®®)”΄(j®§)ΫΧ≥ΧΓΖΘ§Ώ@±Ψïχ¨Π(du®§)”Ύ»κιT «“Μ±ΨΚήΚΟΒΡïχΘ§Ά®ΥΉ“ΉΕ°Θ§Ή¨»ΥΚήΩλ…œ ÷Θ§ΥϋάοΟφΒΡάΐΉ”“≤≤Μεe(cu®Α)ΓΘΒΪ±Ψïχ¨Π(du®§)”ΎΌY‘¥Éû(y®≠u)Μ·ΖΫΟφΒΡΨé≥Χ¦]”–Εύ…Ό…φΦΑΒΫΓΘ

2ΓΔΓΕ‘O(sh®®)”΄(j®§)≈cρû(y®Λn)ΉCVerilog HDLΓΖΘ§Ώ@±Ψïχκm»Μ±»ί^±ΓΘ§ΒΪ «œύ°î(d®Γng)ΨΪ±ΌΘ§÷vΫβΒΡ“≤Κή…ν»κΘ§ΚήΕύΗ≈ΡνΩ¥ΝΥΏ@±Ψïχ”–ΖNΜμ»Μι_ά ΒΡΗ–”XΘ§Κ«Κ«ΓΘ

Τδ¨ç(sh®Σ)Verilog’Z(y®≥)―‘ «œύ°î(d®Γng)»ί“Ή…œ ÷ΒΡΘ§÷ς“Σ «“ΣΫ®ΝΔ“Μ²Ä(g®®)”≤Φΰκä¬ΖΨé≥ΧΒΡΗ≈ΡνΘ§ΚήΕύΡΘâKΕΦ «≤Δ––ΒΡΘ§Εχ≤Μ «ή¦ΦΰΨé≥Χ÷–ΒΡ¥°––ΓΘ“Σœ»°΄κä¬ΖΡΘâKΖΫΩρàD‘ΌΏM(j®§n)––≥Χ–ρΒΡΨé¨ëΓΘ

œ¬Οφ÷v÷vFPGAΒΡ¨W(xu®Π)Νï(x®Σ)Θ§Τδ¨ç(sh®Σ)³²ι_ Φ”…”Ύ≥Χ–ρ“é(gu®©)ΡΘ≤Μ «Κή¥σΘ§Έ“”ΟΒΡ «CPLDΘ®MAXIIœΒΝ–ΒΡΘ©Θ§Κσ¹μ(l®Δi)“é(gu®©)ΡΘ¥σΝΥΘ§”»Τδ «ΘΝΘΡΗΏΥΌΨè¥φ÷–“Σ”ΟΒΫFIFOΘ§CPLD÷–¦]”–RAMΘ§Υυ“‘Ή‘ΦΚ”÷ΉωΝΥFPGAΘ®cycloneIIœΒΝ–Θ©ΒΡΑεΉ”ΓΘΤδ¨ç(sh®Σ)MAXIIœΒΝ–ΚΆFPGAΒΡÉ»(n®®i)≤ΩΫY(ji®Π)‰΄(g®Αu)“―Ϋ¦(j®©ng)ΚήœώΝΥΘ§ΕΦ «Μυ”ΎLUTΒΡΓΘCPLD ΚΆFPGAΒΡΫγœό“≤‘Ϋ¹μ(l®Δi)‘ΫΡΘΚΐΓΘFPGA¨W(xu®Π)Νï(x®Σ)÷–“≤÷ς“ΣΩ¥ΝΥÉ…±ΨEDAœ»δhΙΛΉς “≥ωΒΡïχΘΚ

1ΓΔΓΕAltera FPGA/CPLD ‘O(sh®®)”΄(j®§)Θ®ΜυΒA(ch®≥)ΤΣΘ©ΓΖΘΚ÷vΫβ“Μ–©Μυ±ΨΒΡFPGA‘O(sh®®)”΄(j®§)ΦΦ–g(sh®¥)Θ§“‘ΦΑQuartusII÷–Ης²Ä(g®®)ΙΛΨΏΒΡ”ΟΖ®Θ®IPΘ§RTLΘ§SignalProbeΘ§SignalTapIIΘ§Timing Closure FloorplanΘ§chip EditorΒ»Θ©Θ§¨Π(du®§)”Ύ»κιTΖ«≥ΘΚΟΓΘ

2ΓΔΓΕAltera FPGA/CPLD ‘O(sh®®)”΄(j®§)Θ®ΗΏΦâ(j®Σ)ΤΣΘ©ΓΖΘΚ÷vΫβΝΥ“Μ–©ΗΏΦâ(j®Σ)ΙΛΨΏΒΡëΣ(y®©ng)”ΟΘ§LogicLockΘ§ïr(sh®Σ)–ρΦs χΚήΖ÷ΈωΘ§‘O(sh®®)”΄(j®§)Éû(y®≠u)Μ·Θ§“≤÷v ωΝΥ“Μ–©”≤ΦΰΨé≥ΧΒΡΥΦœκΘ§ΉςûιΧαΗΏ”ΟΓΘ

3ΓΔΓΕFPGA‘O(sh®®)”΄(j®§)÷ΗΡœ--ΤςΦΰΘ§ΙΛΨΏΚΆΝς≥ΧΓΖΘΚΏ@±ΨïχΩ¥ΝΥΥϊΒΡΡΩ䦻Χ≤ΜΉΓΨΆΌIΝΥΘ§Ώ@±Ψïχ÷v ωΝΥFPGA‘O(sh®®)”΄(j®§)ΒΡΗς²Ä(g®®)ΖΫΟφΘ§κm»ΜΟΩ²Ä(g®®)ΖΫΟφΕΦ «ϋc(di®Θn)ΒΫûι÷ΙΘ§ΒΪΡήΉ¨Ρψ”–²Ä(g®®)’ϊσwΒΡΗ≈ΡνΘ§ΝΥΫβFPGAΒΡΥυ”–‘O(sh®®)”΄(j®§)ΙΠΡήΘ§ΝΥΫβFPGAι_Αl(f®Γ)ΒΡ’ϊ²Ä(g®®)Νς≥ΧΓΘ

4ΓΔFPGAΒΡ¨W(xu®Π)Νï(x®Σ)Τδ¨ç(sh®Σ)≤ΜκyΘ§³²ι_ ΦΩ¥ΒΫΥϊ”–Ώ@Ο¥Εύ“ΐΡ_Θ§ΚήΕύ»ΥΨΆΚΠ≈¬Θ§Τδ¨ç(sh®Σ)¥σ≤ΩΖ÷“ΐΡ_ΕΦ «IOΩΎΘ§”…ΡψκS“βΕ®ΝxΘ§’φ’ΐΒΡΩΊ÷ΤΦΑ≈δ÷ΟΙήΡ_Κή…ΌΘ§“ΜΑψïχ…œΕΦïΰ(hu®§)’fΟςΏ@–©Ρ_‘θΟ¥ΏBΫ”Θ§Ή‘ΦΚ¨Π(du®§)’’÷χ°΄²Ä(g®®)FPGAΒΡΑεΉ”Θ§‘Ό‘Ύ…œΟφ’{(di®Λo)‘΅“Μ–©άΐ≥ΧΘ§Ώ@‰”¨W(xu®Π)Τπ¹μ(l®Δi)ΏÄ «ΚήΩλΒΡΓΘœ¬Οφïώ“Μœ¬Έ“Ή‘ΦΚ°΄ΒΡFPGAι_Αl(f®Γ)ΑεΘ§F(xi®Λn)PGA «ep2c5Θ§≈δ÷Ο–ΨΤ§ «EPCS1Θ§Τδ¨ç(sh®Σ)“≤≤ΜΡήΫ–Ήωι_Αl(f®Γ)ΑεΘ§”…”Ύμ½(xi®Λng)ΡΩ“Σ«σΟφΖe–ΓΘ§÷ΜΫ”ΝΥéΉ²Ä(g®®)ι_ξP(gu®Γn)ΚΆLEDΘ§ΤδΥϊ“ΐΡ_»Ϊ≤Ω”Ο≤εα‰ΏB≥ω¹μ(l®Δi)ΝΥΘ§±»ί^ ßîΓΒΡ «ΥΡ²Ä(g®®)Ε®ΈΜΩΉ°΄ΒΡΧΪ¥σΝΥΘ§Κ«Κ«

]]>

]]>CadenceΪ@ΒΟ≈c‘ΎCadenceΒΡ°a(ch®Θn)ΤΖœΒΝ–÷– Ι”ΟΒΡIBMÉ»(n®®i)≤Ω€y(c®®)‘΅ΙΛΨΏ”–ξP(gu®Γn)ΒΡ÷ΣΉR(sh®Σ)°a(ch®Θn)ôύ(qu®Δn)(IP)ΓΘ

SynopsysΚΆNational Semiconductor’ΐΚœΉςι_Αl(f®Γ)÷ß≥÷Τδ ÷≥÷±ψîy Ϋ‘O(sh®®)²δΒΡPowerWiseΦΦ–g(sh®¥)ΒΡÖΔΩΦ‘O(sh®®)”΄(j®§)Νς≥ΧΓΘ¥ΥΝς≥ΧΜυ”ΎSynopsysΒΡGalaxy‘O(sh®®)”΄(j®§)ΤΫ≈_(t®Δi)Θ§Αϋά®ΝΥSynopsysΒΡΚœ≥…ΙΛΨΏΚΆAvantiΒΡ≤ΦΨ÷≈c≤ΦΨÄΙΛΨΏΓΘΏ@É…²Ä(g®®)ΙΪΥΨ“―Ϋ¦(j®©ng)ΚœΉςι_Αl(f®Γ)ΝΥ Ι”ΟΩ…ΉÉκä‘¥κäâΚ‘O(sh®®)”΄(j®§)ΒΡΖΫΖ®ΓΘ ‘ΎΏ@μ½(xi®Λng)ΚœΉς÷–Θ§Synopsys‘ΎGalaxy‘O(sh®®)”΄(j®§)ΤΫ≈_(t®Δi)÷–‘ωΦ”¨Π(du®§)Ω…ΉÉκä‘¥κäâΚΒΡ÷ß≥÷Θ§National SemiconductorΧαΙ© Ι”ΟSynopsysΒΡLibertyΗώ ΫΒΡ≥Χ–ρéλ(k®¥)Θ§“‘ΦΑξP(gu®Γn)φIΒΡIPΚΆ€y(c®®)‘΅ΑΗάΐΓΘ ]]>

Θ®“ΜΘ©ΓΔSKILLΜυΒA(ch®≥)

Θ®ΕΰΘ©ΓΔάϊ”ΟAXLΫ”ΩΎ≤ΌΉςAllegro PCB¨Π(du®§)œσ

Θ®»ΐΘ©ΓΔΉΔÉ‘(c®®)ΚΆ Ι”ΟΉ‘Ε®ΝxAllegroΟϋΝν

Θ®ΥΡΘ©ΓΔAllegro UIΫγΟφ‘O(sh®®)”΄(j®§)ΚΆμëëΣ(y®©ng)

Email: TrizDev@yahoo.cn (“‘«ΑΒΡύ]œδ¹GΝΥ)

ΥΡΓΔAllegro UIΫγΟφ‘O(sh®®)”΄(j®§)ΚΆμëëΣ(y®©ng)

1ΓΔΚÜ(ji®Θn)Ϋι

ΫγΟφ «ΫΜΜΞ‘O(sh®®)”΄(j®§)÷–≤ΜΩ…»±…ΌΒΡ“Μ≤ΩΖ÷Θ§ΚήΕύïr(sh®Σ)ΚρΈ“²Éüo(w®≤)Ζ®÷ΜΉ¨≥Χ–ρΙ¬ΖΦΉ‘ΌpΒΊΏ\(y®¥n)––

2ΓΔΜυ”ΎΈΡ±ΨΟη ωΒΡSKILLΫγΟφ‘O(sh®®)”΄(j®§)

άΐΉ”ΘΚExample.formΘ®ΚÜ(ji®Θn)ÜΈΒΡéΉΕΈΈΡΉ÷“―Ϋ¦(j®©ng)Ι¥ά’≥ωΈ“²Éœκ“ΣΒΡΫγΟφΘ©

FILE_TYPE=FORM_DEFN VERSION=2

FORM

FIXED

PORT 26 20

HEADER "FINDER..."

TILE

TEXT "COMPONENT LIST"

TLOC 1 1

FSIZE 25 3

ENDTEXT

FIELD Placed_List

FLOC 1 3

LIST "" 24 16

OPTION sort

ENDFIELD

FIELD done

FLOC 9 33

MENUBUTTON " OK " 10 3

ENDFIELD

ENDTILE

ENDFORM

3ΓΔ€y(c®®)‘΅FormΒΡΖΫΖ®

Form€y(c®®)‘΅Ϋ”ΩΎΚ·îΒ(sh®¥)axlFormTest(s_formPath)

ΨάΐΘΚ

axlFormTest("C:\\Example.form")

ΙΠΡήΘΚ

άϊ”ΟΏ@²Ä(g®®)Κ·îΒ(sh®¥)Ω…“‘ôz≤ιFormΈΡΦΰΒΡ’Z(y®≥)Ζ®“‘ΦΑFormΒΡο@ Ψ–ßΙϊΘ§ Ψéί΄ΫγΟφïr(sh®Σ)≤Μîύ Ι”ΟΘ§ ΙΡψΒΡΫγΟφΗϋΦ”Τ·ΝΝ

Tips:

AΓΔAllegroΥυ”–ΒΡFormΈΡΦΰΕΦΖ≈‘ΎSetup - User Preferences...≤ΥÜΈΘ§Ώx™ώUI_PathΝ–³e÷–ΒΡformpathΓΘ

≤ιΩ¥AllegroΥυ”–ΫγΟφΈΡΦΰΘ§ΚήΚΟΒΡΫγΟφ÷Ί”ΟΌY‘¥

BΓΔ¨ΔΉ‘Ε®ΝxΒΡFormΈΡΦΰΖ≈‘Ύformpathœ¬Ω…“‘≤Μ”Ο¨ëΫ^¨Π(du®§)¬ΖèΫ’{(di®Λo)”ΟΘ§≤Μ–≈‘΅‘΅

4ΓΔΫγΟφΙΛΨΏι_Αl(f®Γ)ABCDE

AΓΔ³™(chu®Λng)Ϋ®ΫγΟφΈΡΦΰ≤Δ Ι”ΟaxlFormCreateΜρaxlMiniStatusLoad¥ρι_FormΨδ±ζΘ®ΉΔ“β–ΕΡΞöΔσHΘ©

BΓΔ Ι”ΟaxlFormSetField≥θ ΦΜ·ΫγΟφÖ^(q®±)”ρ

CΓΔaxlFormDisplayο@ ΨΫγΟφ

DΓΔ‘ΎaxlFormCallback÷–Ε®Νx”ΟëτΫΜΜΞΚΆÖ^(q®±)”ρμëëΣ(y®©ng)

EΓΔ Ι”ΟaxlFormCloseξP(gu®Γn)ι]ΫγΟφ¥ΑΩΎ

/*

ΙΠΡήΘΚΆ®Ώ^Ώx™ώΫγΟφΝ–±μΩρ÷–ΒΡΤςΦΰΟϊΖQûg”[ΤςΦΰ

ΟϋΝνΘΚOverviewComps

*/

;ΉΔÉ‘(c®®)ΟϋΝν

axlCmdRegister("OverviewComps" 'TestFormAppMainModule)

;³™(chu®Λng)Ϋ®ΫγΟφΈΡΦΰ≤Δο@ ΨΫγΟφΘ®÷ςΡΘâKΘ©

procedure( TestFormAppMainModule()

prog( (FileName FilePort)

;¨ëΈΡΦΰ…ζ≥…ΫγΟφΈΡΦΰ

FileName = "TestForm.form"

FilePort = outfile(FileName "w")

fprintf(FilePort "FILE_TYPE=FORM_DEFN VERSION=2\n")

fprintf(FilePort "FORM\n")

fprintf(FilePort "FIXED\n")

fprintf(FilePort "PORT 26 20\n\n")

fprintf(FilePort "HEADER \"FORM TEST...\"\n\n")

fprintf(FilePort "TILE\n\n")

fprintf(FilePort "TEXT \"ComponentList:\"\n\n")

fprintf(FilePort "TLOC 1 1\n")

fprintf(FilePort "FSIZE 25 3\n")

fprintf(FilePort "ENDTEXT\n\n")

fprintf(FilePort "FIELD ComponentList\n")

fprintf(FilePort "FLOC 1 3\n")

fprintf(FilePort "LIST \"\" 24 16\n")

fprintf(FilePort "OPTION sort\n")

fprintf(FilePort "ENDFIELD\n\n")

fprintf(FilePort "FIELD Quit\n")

fprintf(FilePort "FLOC 9 33\n")

fprintf(FilePort "MENUBUTTON \"EXIT\" 10 3\n")

fprintf(FilePort "ENDFIELD\n\n")

fprintf(FilePort "ENDTILE\n\n")

fprintf(FilePort "ENDFORM\n\n")

close(FilePort)

;³™(chu®Λng)Ϋ®ΫγΟφΨδ±ζΘ§³h≥ΐΫγΟφΈΡΦΰΘ®–ΕΡΞöΔσH...Θ©

fw = axlFormCreate(gensym() FileName '("E" "OUTER") 'TestFormAppCallBack t)

deleteFile(FileName)

;ΫγΟφÖ^(q®±)”ρ≥θ ΦΜ·

TestFormFieldInit(fw)

;ο@ ΨΫγΟφ

axlFormDisplay(fw)

return(t)

))

;ΫγΟφÖ^(q®±)”ρ≥θ ΦΜ·

procedure( TestFormFieldInit(fw)

prog( (CompsNameList)

;Ϊ@»ΓΥυ”–ΒΡΤςΦΰΟϊΖQ

CompsNameList = axlDBGetDesign()->components~>name

;‘O(sh®®)÷ΟΤςΦΰΝ–±μÖ^(q®±)”ρ

axlFormSetField(fw "ComponentList" CompsNameList)

return(t)

))

;ΫγΟφÖ^(q®±)”ρμëëΣ(y®©ng)ΜΊ’{(di®Λo)Κ·îΒ(sh®¥)

procedure( TestFormAppCallBack(fw)

prog( (CompName CompId)

case(fw->curField

("ComponentList"

CompName = fw->curValue

CompId = axlSelectByName("COMPONENT" CompName)

;Ε®ΈΜΒΫ¨Π(du®§)œσ

axlZoomToDbid(CompId t)

;ο@ Ψ¨Π(du®§)œσ‘îΦö(x®§)–≈œΔ

axlShowObject(CompId)

)

("Quit"

;«εάμ§F(xi®Λn)àω(ch®Θng)

axlClearSelSet()

axlSetFindFilter(?enabled "NOALL" ?onButtons "NOALL")

axlFormClose(fw)

)

)

return(t)

))

5ΓΔÖΔΩΦΈΡôn

%CDSROOT%\doc

άΐΉ”ΘΚ

D:\DesignAdvance\Cadence\SPB_15.2\doc

ÖΔΩΦ ÷É‘(c®®)Ν–±μΘΚ

algroskill AXLΫ”ΩΎΚ·îΒ(sh®¥)ÖΔΩΦ ÷É‘(c®®)

Tips:

Ω¥Ω¥œ¬ΟφΒΡ¬ΖèΫœ¬ « ≤Ο¥•|ΈςΘ§±ΘΉC‰ΖΥάΡψ... ...

%CDSROOT%\share\pcb\example\skill

6ΓΔ’nΚσΝï(x®Σ)ν}

ΗψΕ°%CDSROOT%\share\pcb\example\skill¬ΖèΫœ¬Υυ”–ΒΡ≥Χ–ρ¥ζ¥aΘ§»ΜΚσΙßœ≤Ρψ»κιTΝΥ... ...

’Z(y®≥)―‘ΘΚ”Δ’Z(y®≥)

ΨW(w®Θng)÷ΖΘΚhttp://www.cadence.com/products/pcb/pcb_design/pages/default.aspx

νê³eΘΚPCB‘O(sh®®)”΄(j®§)

Cadence? « άΫγ…œΉν¥σΒΡκäΉ”‘O(sh®®)”΄(j®§)ΦΦ–g(sh®¥)ΚΆ≈δΧΉΖΰ³’(w®¥)ΒΡ EDA Ι©Ί¦…Χ÷°“ΜΓΘCadence? Allegro? ³t « Cadence ΆΤ≥ωΒΡœ»ΏM(j®§n) PCB ‘O(sh®®)”΄(j®§)≤ΦΨÄΙΛΨΏΓΘ Allegro ΧαΙ©ΝΥΝΦΚΟ«“ΫΜΜΞΒΡΙΛΉςΫ”ΩΎΚΆèä(qi®Δng)¥σΆξ…ΤΒΡΙΠΡήΘ§ΚΆΥϋ«ΑΕΥ°a(ch®Θn)ΤΖ Capture ΒΡΫY(ji®Π)ΚœΘ§ûι°î(d®Γng)«ΑΗΏΥΌΓΔΗΏΟήΕ»ΓΔΕύ¨”ΒΡèΆ(f®¥)κs PCB ‘O(sh®®)”΄(j®§)≤ΦΨÄΧαΙ©ΝΥΉνΆξΟάΫβ¦QΖΫΑΗΓΘ

Allegro ™μ”–Άξ…ΤΒΡ Constraint ‘O(sh®®)Ε®Θ§”Οëτ÷ΜμöΑ¥“Σ«σ‘O(sh®®)Ε®ΚΟ≤ΦΨÄ“é(gu®©)³tΘ§‘Ύ≤ΦΨÄïr(sh®Σ)≤ΜΏ`Ζ¥ DRC ΨΆΩ…“‘Ώ_(d®Δ)ΒΫ≤ΦΨÄΒΡ‘O(sh®®)”΄(j®§)“Σ«σΘ§èΡΕχΙù(ji®Π)ΦsΝΥü©§çΒΡ»ΥΙΛôz≤ιïr(sh®Σ)ιgΘ§ΧαΗΏΝΥΙΛΉς–߬ ΘΓΗϋΡήâρΕ®ΝxΉν–ΓΨĨ£ΜρΨÄιL(zh®Θng)Β»ÖΔîΒ(sh®¥)“‘ΖϊΚœ°î(d®Γng)ΫώΗΏΥΌκä¬ΖΑε≤ΦΨÄΒΡΖNΖN–η«σΓΘ

ή¦Φΰ÷–ΒΡ Constraint MangerΧαΙ©ΝΥΚÜ(ji®Θn)ùçΟςΝΥΒΡΫ”ΩΎΖΫ±ψ Ι”Ο’Ώ‘O(sh®®)Ε®ΚΆ≤ιΩ¥ Constraint –ϊΗφΓΘΥϋ≈cCadence? OrCAD? Capture ΒΡΫY(ji®Π)ΚœΉ¨ E.E. κäΉ”ΙΛ≥Χéü‘ΎάL÷ΤΨĬΖàDïr(sh®Σ)ΨΆΡή‘O(sh®®)Ε®ΚΟ“é(gu®©)³tîΒ(sh®¥)™ΰ(j®¥)Θ§≤ΔΡή“ΜΤπéßΒΫAllegroΙΛΉς≠h(hu®Δn)Ψ≥÷–Θ§Ή‘³”(d®Αng)‘Ύî[ΝψΦΰΦΑ≤ΦΨÄïr(sh®Σ)“ά’’“é(gu®©)³tΧéάμΦΑôz≤ιΘ§ΕχΏ@–©“é(gu®©)³tîΒ(sh®¥)™ΰ(j®¥)ΒΡΫ¦(j®©ng)ρû(y®Λn)÷ΒΨυΩ…÷ΊèΆ(f®¥) Ι”Ο‘ΎœύΆ§–‘Ό|(zh®§)ΒΡκä¬ΖΑε‘O(sh®®)”΄(j®§)…œΓΘ

Allegro ≥ΐΝΥ…œ ωΒΡΙΠΡήΆβΘ§Τδèä(qi®Δng)¥σΒΡΉ‘³”(d®Αng)ΆΤîD push ΚΆΌNΨÄ hug ΉΏΨÄ“‘ΦΑΆξ…ΤΒΡΉ‘³”(d®Αng)–όΨÄΙΠΡήΗϋ «Ϋo”ΟëτΧαΙ©‰O¥σΒΡΖΫ±ψΘΜèä(qi®Δng)¥σΒΡΌNàDΙΠΡήΘ§Ω…“‘ΧαΙ©Εύ”ΟëτΆ§ïr(sh®Σ)Χéάμ“ΜâKèΆ(f®¥)κsΑεΉ”Θ§èΡΕχ¥σ¥σΒΊΧαΗΏΝΥΙΛΉς–߬ ΓΘΜρ «άϊ”ΟΏxΌè(g®Αu)ΒΡ«–àDΙΠΡή¨Δκä¬ΖΑφ«–Ζ÷≥…Ης²Ä(g®®)Ö^(q®±)âKΘ§Ή¨ΟΩ²Ä(g®®)Ö^(q®±)âKΗς”–¨Θ¬öΒΡ»ΥΆ§ïr(sh®Σ)ΏM(j®§n)––‘O(sh®®)”΄(j®§) Θ§Ώ_(d®Δ)ΒΫΆ§ΖίàDΕύ»ΥΆ§ïr(sh®Σ)‘O(sh®®)”΄(j®§)≤ΔΡήΩsΕΧïr(sh®Σ)≥ΧΒΡΡΩΒΡ ΓΘ

”Οëτ‘Ύ≤ΦΨÄïr(sh®Σ)ΉωΏ^ΗϋΟϊΓΔ¬™(li®Δn)ôC(j®©)ΜΞ™Q“‘ΦΑ–όΗΡΏâί΄ΚσΘ§Ω…“‘Ζ«≥ΘΖΫ±ψΒΊΜΊΨéΒΫ Capture ΨĬΖàD÷–Θ§ΨĬΖàD–όΗΡΚσ“≤Ω…“‘Ζ«≥ΘΖΫ±ψΒΊΗϋ–¬ΒΫ Allegro ÷–ΘΜ”ΟëτΏÄΩ…“‘‘Ύ Capture ≈c Allegro ÷°ιg¨Π(du®§)¨Π(du®§)œσΒΡΜΞœύϋc(di®Θn)ΏxΦΑ–όΗΡΓΘ

¨Π(du®§)”Ύ‰I(y®®)ΫγΥυ÷Ί“ïΒΡψ~≤≠ΒΡάL÷ΤΚΆ–όΗΡΙΠΡήΘ§ Allegro ΧαΙ©ΝΥΚÜ(ji®Θn)ÜΈΖΫ±ψΒΡÉ»(n®®i)¨”Ζ÷ΗνΙΠΡήΘ§“‘ΦΑΡήâρ?q®±)Π’ΐΊ?f®¥)Τ§É»(n®®i)¨”ΒΡôzιÜΓΘ¨Π(du®§)”Ύδ¹ψ~“≤Ω…Ζ÷³”(d®Αng)ëB(t®Λi)ψ~Μρ «λoëB(t®Λi)ψ~Θ§“‘Ήςûιδ¹¥σΒΊΜρ «ΉΏ¥σκäΝς÷°≤ΜΆ§ëΣ(y®©ng)”ΟΓΘ³”(d®Αng)ëB(t®Λi)ψ~ΒΡÖΔîΒ(sh®¥)Ω…“‘Ζ÷≥…¨Π(du®§)Υυ”–ψ~ΓΔÜΈ“Μψ~ΜρÜΈ“Μ¨Π(du®§)œσΒΡ≤ΜΆ§≥ΧΕ»‘O(sh®®)Ε®Θ§“‘Ώ_(d®Δ)ΒΫψ~≤≠¨Π(du®§)ΗςΫ”ϋc(di®Θn)Ω…‘O(sh®®)≤ΜΆ§Ϋ”άm(x®¥)–ßΙϊΜριgΨύ÷ΒΒ»“Σ«σΘ§¹μ(l®Δi)≈δΚœ“ρ‘O(sh®®)”΄(j®§)ΧΊ–‘Εχ”–ΒΡΧΊ β‘O(sh®®)Ε®ΓΘ

‘Ύίî≥ωΒΡ≤ΩΖ÷Θ§ΒΉΤ§ίî≥ωΙΠΡήΑϋΚ§ 274D ΓΔ 274X ΓΔ Barco DPF ΓΔ MDA “‘ΦΑ÷±Ϋ”ίî≥ω ODB++ Β»Εύ‰”Μ·Ηώ ΫîΒ(sh®¥)™ΰ(j®¥)°î(d®Γng)»ΜΏÄ÷ß≥÷…ζ°a(ch®Θn)Υυ–ηΒΡ Pick & Place ΓΔNC Drill ΚΆ Bare-Board Test »»‘≠ ΦîΒ(sh®¥)™ΰ(j®¥)ίî≥ωΓΘ

Allegro ΥυΧαΙ©ΒΡèä(qi®Δng)¥σίî»κίî≥ωΙΠΡήΗϋ «ΖΫ±ψ≈cΤδΥϋœύξP(gu®Γn)ή¦ΦΰΒΡ€œΆ®Θ§άΐ»γ ADIVA ΓΔ UGS(Fabmaster) ΓΔ VALOR ΓΔ Agilent ADSΓ≠ Μρ «ôC(j®©)‰΄(g®Αu)ΒΡ DXF ΓΔ IDFΓ≠Γ≠Γ≠ ΓΘ

ûιΝΥΆΤèV’ϊ²Ä(g®®)œ»ΏM(j®§n) EDA –àω(ch®Θng) ,Allegro ΧαΙ©ΝΥ OrCAD Layout ΓΔ PADS ΓΔ P-CAD Β»Ϋ”ΩΎΘ§Ή¨œκόD(zhu®Θn)™Q PCB Layout ή¦ΦΰΒΡ Ι”Ο’ΏΘ§¨Π(du®§)”Ύ≈f”–ΒΡàDônΡήμ‰άϊόD(zhu®Θn)™Q÷Ν Allegro ÷–ΓΘ Allegro ”–÷χ ≤ΌΉςΖΫ±ψΘ§Ϋ”ΩΎ”―ΚΟΘ§ΙΠΡήèä(qi®Δng)¥σΘ§’ϊΚœ–‘ΚΟ Β»÷TΕύÉû(y®≠u)ϋc(di®Θn)Θ§ «“ΜΦ“ΙΪΥΨΆΕΌY EDA ή¦ΦΰΒΡάμœκΏx™ώ

ΓΓΓΓκS÷χ»Υ²É¨Π(du®§)Ά®–≈–η«σΒΡ≤ΜîύΧαΗΏΘ§“Σ«σ–≈Χ•(h®Λo)ΒΡ²ςίîΚΆΧéάμΒΡΥΌΕ»‘Ϋ¹μ(l®Δi)‘ΫΩλ.œύëΣ(y®©ng)ΒΡΗΏΥΌPCBΒΡëΣ(y®©ng)”Ο“≤‘Ϋ¹μ(l®Δi)‘ΫèVΘ§‘O(sh®®)”΄(j®§)“≤‘Ϋ¹μ(l®Δi)‘ΫèΆ(f®¥)κs.ΗΏΥΌκä¬Ζ”–É…²Ä(g®®)ΖΫΟφΒΡΚ§ΝxΘΚ“Μ «νl¬ ΗΏΘ§Ά®≥Θ’J(r®®n)ûιîΒ(sh®¥)Ή÷κä¬ΖΒΡνl¬ Ώ_(d®Δ)ΒΫΜρ «≥§Ώ^45MHz÷Ν50MHzΘ§Εχ«“ΙΛΉς‘ΎΏ@²Ä(g®®)νl¬ ÷°…œΒΡκä¬Ζ“―Ϋ¦(j®©ng)’ΦΒΫΝΥ’ϊ²Ä(g®®)œΒΫy(t®·ng)ΒΡ»ΐΖ÷÷°“ΜΘ§ΨΆΖQûιΗΏΥΌκä¬Ζ.ΝμΆβèΡ–≈Χ•(h®Λo)ΒΡ…œ…ΐ≈cœ¬ΫΒïr(sh®Σ)ιgΩΦë]Θ§°î(d®Γng)–≈Χ•(h®Λo)ΒΡ…œ…ΐïr(sh®Σ)ιg–Γ”Ύ6±Ε–≈Χ•(h®Λo)²ςίî―”ïr(sh®Σ)ïr(sh®Σ)Φ¥’J(r®®n)ûι–≈Χ•(h®Λo) «ΗΏΥΌ–≈Χ•(h®Λo)Θ§¥Υïr(sh®Σ)ΩΦë]ΒΡ≈c–≈Χ•(h®Λo)ΒΡΨΏσwνl¬ üo(w®≤)ξP(gu®Γn).

ΓΓΓΓ2 ΗΏΥΌPCB‘O(sh®®)”΄(j®§)ΒΡΜυ±ΨÉ»(n®®i)»ί

ΓΓΓΓΗΏΥΌκä¬Ζ‘O(sh®®)”΄(j®§)‘Ύ§F(xi®Λn)¥ζκä¬Ζ‘O(sh®®)”΄(j®§)÷–Υυ’ΦΒΡ±»άΐ‘Ϋ¹μ(l®Δi)‘Ϋ¥σΘ§‘O(sh®®)”΄(j®§)κyΕ»“≤‘Ϋ¹μ(l®Δi)‘ΫΗΏΘ§ΥϋΒΡΫβ¦Q≤ΜÉH–η“ΣΗΏΥΌΤςΦΰΘ§Ηϋ–η“Σ‘O(sh®®)”΄(j®§)’ΏΒΡ÷«ΜέΚΆΉ–Φö(x®§)ΒΡΙΛΉςΘ§±Ίμö’J(r®®n)’φ―–ΨΩΖ÷ΈωΨΏσw«ι¦rΘ§Ϋβ¦Q¥φ‘ΎΒΡΗΏΥΌκä¬ΖÜ•ν}.“ΜΑψ’f¹μ(l®Δi)÷ς“ΣΑϋά®»ΐΖΫΟφΒΡ‘O(sh®®)”΄(j®§)ΘΚ–≈Χ•(h®Λo)Άξ’ϊ–‘‘O(sh®®)”΄(j®§)ΓΔκä¥≈Φφ»ί‘O(sh®®)”΄(j®§)ΓΔκä‘¥Άξ’ϊ–‘‘O(sh®®)”΄(j®§).

ΓΓΓΓ2.1 –≈Χ•(h®Λo)Άξ’ϊ–‘(signal integrity)‘O(sh®®)”΄(j®§)

ΓΓΓΓ–≈Χ•(h®Λo)Άξ’ϊ–‘ «÷Η–≈Χ•(h®Λo)‘Ύ–≈Χ•(h®Λo)ΨÄ…œΒΡΌ|(zh®§)ΝΩ.–≈Χ•(h®Λo)ΨΏ”–ΝΦΚΟΒΡ–≈Χ•(h®Λo)Άξ’ϊ–‘ «÷Η°î(d®Γng)‘Ύ–η“ΣΒΡïr(sh®Σ)ΚρΘ§ΨΏ”–Υυ±Ί–ηΏ_(d®Δ)ΒΫΒΡκäâΚκäΤΫîΒ(sh®¥)÷Β.≤νΒΡ–≈Χ•(h®Λo)Άξ’ϊ–‘≤Μ «”…Ρ≥“Μ“ρΥΊ¨ß(d®Θo)÷¬ΒΡΘ§Εχ «”…ΑεΦâ(j®Σ)‘O(sh®®)”΄(j®§)÷–ΕύΖN“ρΥΊΙ≤Ά§“ΐΤπΒΡ.ΧΊ³e «‘ΎΗΏΥΌκä¬Ζ÷–Θ§Υυ Ι”ΟΒΡ–ΨΤ§ΒΡ«–™QΥΌΕ»Ώ^ΩλΓΔΕΥΫ”‘ΣΦΰ≤Φ‘O(sh®®)≤ΜΚœάμΓΔκä¬ΖΒΡΜΞ¬™(li®Δn)≤ΜΚœάμΒ»ΕΦïΰ(hu®§)“ΐΤπ–≈Χ•(h®Λo)ΒΡΆξ’ϊ–‘Ü•ν}.ΨΏσw÷ς“ΣΑϋά®¥°?d®Γng)_ΓΔΖ¥…δΓΔΏ^¦_≈cœ¬¦_ΓΔ’ώ éΓΔ–≈Χ•(h®Λo)―”ΏtΒ».

ΓΓΓΓ2.1.1 ¥°?d®Γng)_(crosstalk)

ΓΓΓΓ¥°?d®Γng)_ «œύύèÉ…½l–≈Χ•(h®Λo)ΨÄ÷°ιgΒΡ≤Μ±Ί“ΣΒΡώνΚœΘ§–≈Χ•(h®Λo)ΨÄ÷°ιgΒΡΜΞΗ–ΚΆΜΞ»ί“ΐΤπΨÄ…œΒΡ‘κ¬ï.“ρ¥Υ“≤ΨΆΑ―ΥϋΖ÷ûιΗ––‘¥°?d®Γng)_ΚΆ»ί–‘¥°?d®Γng)_Θ§Ζ÷³e“ΐΑl(f®Γ)ώνΚœκäΝςΚΆώνΚœκäâΚ.°î(d®Γng)–≈Χ•(h®Λo)ΒΡΏÖΨâΥΌ¬ ΒΆ”Ύ1nsïr(sh®Σ)Θ§¥°?d®Γng)_Ü•ν}ΨΆëΣ(y®©ng)‘™ΩΦë].»γΙϊ–≈Χ•(h®Λo)ΨÄ…œ”–ΫΜΉÉΒΡ–≈Χ•(h®Λo)κäΝςΆ®Ώ^ïr(sh®Σ)Θ§ïΰ(hu®§)°a(ch®Θn)…ζΫΜΉÉΒΡ¥≈àω(ch®Θng)Θ§Χé”Ύ¥≈àω(ch®Θng)÷–ΒΡœύύèΒΡ–≈Χ•(h®Λo)ΨÄïΰ(hu®§)Η–ëΣ(y®©ng)≥ω–≈Χ•(h®Λo)κäâΚ.“ΜΑψPCBΑ娔ΒΡÖΔîΒ(sh®¥)ΓΔ–≈Χ•(h®Λo)ΨÄιgΨύΓΔρ¨(q®±)³”(d®Αng)ΕΥΚΆΫ” ’ΕΥΒΡκäöβΧΊ–‘ΦΑ–≈Χ•(h®Λo)ΨÄΒΡΕΥΫ”ΖΫ Ϋ¨Π(du®§)¥°?d®Γng)_ΕΦ”–“ΜΕ®ΒΡ”Αμë.‘ΎCadenceΒΡ–≈Χ•(h®Λo)Ζ¬’φΙΛΨΏ÷–Ω…“‘Ά§ïr(sh®Σ)¨Π(du®§)6½lώνΚœ–≈Χ•(h®Λo)ΨÄΏM(j®§n)––¥°?d®Γng)_ΚσΖ¬’φΘ§Ω…“‘‘O(sh®®)÷ΟΒΡ£ΏΟηÖΔîΒ(sh®¥)”–ΘΚPCBΒΡΫικä≥ΘîΒ(sh®¥)Θ§ΫιΌ|(zh®§)ΒΡΚώΕ»Θ§≥Νψ~ΚώΕ»Θ§–≈Χ•(h®Λo)ΨÄιL(zh®Θng)Ε»ΚΆ¨£Ε»Θ§–≈Χ•(h®Λo)ΨÄΒΡιgΨύ.Ζ¬’φïr(sh®Σ)ΏÄ±Ίμö÷ΗΕ®“Μ²Ä(g®®) ή«÷ΚΠΒΡ–≈Χ•(h®Λo)ΨÄΘ§“≤ΨΆ «ΩΦ≤λΝμΆβΒΡ–≈Χ•(h®Λo)ΨĨΠ(du®§)±Ψ½lΨĬΖΒΡΗ…î_«ι¦rΘ§ΦΛ³ν(l®§)‘O(sh®®)÷Οûι≥ΘΗΏΜρ «≥ΘΒΆΘ§Ώ@‰”ΨΆΩ…“‘€y(c®®)ΒΫΤδΥϊ–≈Χ•(h®Λo)ΨĨΠ(du®§)±Ψ½l–≈Χ•(h®Λo)ΨÄΒΡΗ–ëΣ(y®©ng)κäâΚΒΡΩ²ΚΆΘ§èΡΕχΩ…“‘ΒΟΒΫùMΉψ“Σ«σΒΡΉν–ΓιgΨύΚΆΉν¥σ≤Δ––ιL(zh®Θng)Ε».

ΓΓΓΓ2.1.2 Ζ¥…δ(reflection)

ΓΓΓΓΖ¥…δΚΆΈ“²ÉΥυ÷ΣΒάΒΡΙβΫ¦(j®©ng)Ώ^≤ΜΏBάm(x®¥)ΒΡΫιΌ|(zh®§)ïr(sh®Σ)ΕΦïΰ(hu®§)”–≤ΩΖ÷ΡήΝΩΖ¥…δΜΊ¹μ(l®Δi)“Μ‰”Θ§ΨΆ «–≈Χ•(h®Λo)‘Ύ²ςίîΨÄ…œΒΡΜΊ≤®.¥Υïr(sh®Σ)–≈Χ•(h®Λo)ΙΠ¬ ¦]”–»Ϊ≤Ω²ςίî?sh®¥)ΫΊ?f®¥)ίdΧéΘ§”–“Μ≤ΩΖ÷±ΜΖ¥…δΜΊ¹μ(l®Δi)ΝΥ.‘ΎΗΏΥΌΒΡPCB÷–¨ß(d®Θo)ΨıΊμöΒ»–ßûι²ςίîΨÄΘ§Α¥’’²ςίîΨÄάμ’™Θ§»γΙϊ‘¥ΕΥ≈cΊ™(f®¥)ίdΕΥΨΏ”–œύΆ§ΒΡΉηΩΙΘ§Ζ¥…δΨΆ≤Μïΰ(hu®§)Αl(f®Γ)…ζΝΥ.Εΰ’ΏΉηΩΙ≤ΜΤΞ≈δïΰ(hu®§)“ΐΤπΖ¥…δΘ§Ί™(f®¥)ίdïΰ(hu®§)¨Δ“Μ≤ΩΖ÷κäâΚΖ¥…δΜΊ‘¥ΕΥ.Ηυ™ΰ(j®¥)Ί™(f®¥)ίdΉηΩΙΚΆ‘¥ΉηΩΙΒΡξP(gu®Γn)œΒ¥σ–Γ≤ΜΆ§Θ§Ζ¥…δκäâΚΩ…Ρήûι’ΐΘ§“≤Ω…ΡήûιΊ™(f®¥).»γΙϊΖ¥…δ–≈Χ•(h®Λo)Κήèä(qi®Δng)Θ§·BΦ”‘Ύ‘≠–≈Χ•(h®Λo)…œΘ§ΚήΩ…ΡήΗΡΉÉΏâί΄†νëB(t®Λi)Θ§¨ß(d®Θo)÷¬Ϋ” ’îΒ(sh®¥)™ΰ(j®¥)εe(cu®Α)’`.»γΙϊ‘Ύïr(sh®Σ)γä–≈Χ•(h®Λo)…œΩ…Ρή“ΐΤπïr(sh®Σ)γä―Ί≤ΜÜΈ’{(di®Λo)Θ§ΏM(j®§n)Εχ“ΐΤπ’`”|Αl(f®Γ).“ΜΑψ≤ΦΨÄΒΡéΉΚΈ–Έ†νΓΔ≤Μ’ΐ¥_ΒΡΨÄΕΥΫ”ΓΔΫ¦(j®©ng)Ώ^ΏBΫ”ΤςΒΡ²ςίîΦΑκä‘¥ΤΫΟφΒΡ≤ΜΏBάm(x®¥)Β»“ρΥΊΨυïΰ(hu®§)¨ß(d®Θo)÷¬¥ΥνêΖ¥…δ. ΝμΆβ≥Θ”–“Μ²Ä(g®®)ίî≥ωΕύ²Ä(g®®)Ϋ” ’Θ§Ώ@ïr(sh®Σ)≤ΜΆ§ΒΡ≤ΦΨÄ≤Ώ¬‘°a(ch®Θn)…ζΒΡΖ¥…δ¨Π(du®§)ΟΩ²Ä(g®®)Ϋ” ’ΕΥΒΡ”Αμë“≤≤ΜœύΆ§Θ§Υυ“‘≤ΦΨÄ≤Ώ¬‘“≤ «”ΑμëΖ¥…δΒΡ“Μ²Ä(g®®)≤ΜΩ…Κω“ïΒΡ“ρΥΊ.

ΓΓΓΓ2.1.3 Ώ^¦_(overshoot)ΚΆœ¬¦_(undershoot)

ΓΓΓΓΏ^¦_ «”…”Ύκä¬Ζ«–™QΥΌΕ»Ώ^Ωλ“‘ΦΑ…œΟφΧαΒΫΒΡΖ¥…δΥυ“ΐΤπΒΡ–≈Χ•(h®Λo)ΧχΉÉΘ§“≤ΨΆ «–≈Χ•(h®Λo)ΒΎ“Μ²Ä(g®®)Ζε÷Β≥§Ώ^ΝΥΖε÷ΒΜρΙ»÷ΒΒΡ‘O(sh®®)Ε®κäâΚ.œ¬¦_ «÷Ηœ¬“Μ²Ä(g®®)Ι»÷ΒΜρΖε÷Β.Ώ^Ζ÷ΒΡΏ^¦_Ρήâρ“ΐΤπ±ΘΉo(h®¥)Εΰ‰OΙήΙΛΉςΘ§ ¨ß(d®Θo)÷¬Ώ^‘γΒΊ ß–ßΘ§΅ά(y®Δn)÷ΊΒΡΏÄïΰ(hu®§)™pâΡΤςΦΰ.Ώ^Ζ÷ΒΡœ¬¦_Ρήâρ“ΐΤπΦΌΒΡïr(sh®Σ)γäΜρîΒ(sh®¥)™ΰ(j®¥)εe(cu®Α)’`.Υϋ²ÉΩ…“‘Ά®Ώ^‘ωΦ”Ώm°î(d®Γng)ΕΥΫ””η“‘€p…ΌΜρœϊ≥ΐ.

ΓΓΓΓ2.1.4 ’ώ é(ringing)ΚΆ≠h(hu®Δn)ά@’ώ é(rounding)

ΓΓΓΓ’ώ éΒΡ§F(xi®Λn)œσ «Ζ¥èΆ(f®¥)≥ω§F(xi®Λn)Ώ^¦_ΚΆœ¬¦_.–≈Χ•(h®Λo)ΒΡ’ώ éΚΆ≠h(hu®Δn)ά@’ώ é”…ΨÄ…œΏ^Ε»ΒΡκäΗ–ΚΆκä»ί“ΐΤπΒΡΫ” ’ΕΥ≈c²ςίîΨÄΚΆ‘¥ΕΥΒΡΉηΩΙ≤ΜΤΞ≈δΕχ°a(ch®Θn)…ζΒΡΘ§Ά®≥ΘΑl(f®Γ)…ζ‘ΎΏâί΄κäΤΫιTœόΗΫΫϋΘ§Εύ¥ΈΩγ‘ΫΏâί΄κäΤΫιTœόïΰ(hu®§)¨ß(d®Θo)÷¬Ώâί΄ΙΠΡήΈ…¹y.’ώ éΚΆ≠h(hu®Δn)ά@’ώ éΆ§Ζ¥…δ“Μ‰”“≤ «”…ΕύΖN“ρΥΊ“ΐΤπΒΡΘ§’ώ éΩ…“‘Ά®Ώ^Ώm°î(d®Γng)?sh®¥)ΡΕΥΫ”Μρ «ΗΡΉÉPCBÖΔîΒ(sh®¥)”η“‘€p–ΓΘ§ΒΪ «≤ΜΩ…ΡήΆξ»Ϊœϊ≥ΐ.

ΓΓΓΓ‘ΎCadenceΒΡ–≈Χ•(h®Λo)Ζ¬’φή¦Φΰ÷–Θ§¨Δ“‘…œΒΡ–≈Χ•(h®Λo)Άξ’ϊ–‘Ü•ν}ΕΦΖ≈‘ΎΖ¥…δÖΔîΒ(sh®¥)÷–»ΞΕ»ΝΩ.‘ΎΫ” ’ΚΆρ¨(q®±)³”(d®Αng)ΤςΦΰΒΡIBISΡΘ–Άéλ(k®¥)÷–Θ§Έ“²É÷Μ–η“Σ‘O(sh®®)÷Ο≤ΜΆ§ΒΡ²ςίîΨÄΉηΩΙÖΔîΒ(sh®¥)ΓΔκäΉη÷ΒΓΔ–≈Χ•(h®Λo)²ςίîΥΌ¬ “‘ΦΑΏx™ώΈΔéßΨÄΏÄ «é߆νΨÄΘ§ΨΆΩ…“‘Ά®Ώ^Ζ¬’φΙΛΨΏ÷±Ϋ””΄(j®§)Υψ≥ω–≈Χ•(h®Λo)ΒΡ≤®–Έ“‘ΦΑœύëΣ(y®©ng)ΒΡîΒ(sh®¥)™ΰ(j®¥)Θ§Ώ@‰”ΨΆΩ…“‘’“≥ωΤΞ≈δΒΡ²ςίîΨÄΉηΩΙ÷ΒΓΔκäΉη÷ΒΓΔ–≈Χ•(h®Λo)²ςίîΥΌ¬ Θ§‘Ύ¨Π(du®§)ëΣ(y®©ng)ΒΡPCBή¦ΦΰAllegro÷–Θ§ΨΆΩ…“‘Ηυ™ΰ(j®¥)œύ¨Π(du®§)ëΣ(y®©ng)ΒΡ²ςίîΨÄΉηΩΙ÷ΒΚΆ–≈Χ•(h®Λo)²ςίîΥΌ¬ ΒΟΒΫΗς¨”÷–œύ¨Π(du®§)ëΣ(y®©ng)–≈Χ•(h®Λo)ΨÄΒΡ¨£Ε»(–ηΧα«Α‘O(sh®®)ΚΟ·B¨”ΒΡμ‰–ρΚΆΗςÖΔîΒ(sh®¥)).Ώx™ώκäΉηΤΞ≈δΒΡΖΫ Ϋ“≤”–ΕύΖNΘ§Αϋά®‘¥ΕΥΕΥΫ”ΚΆ≤Δ––ΕΥΫ”Β»Θ§Ηυ™ΰ(j®¥)≤ΜΆ§ΒΡκä¬ΖΏx™ώ≤ΜΆ§ΒΡΖΫ Ϋ.‘Ύ≤ΦΨÄ≤Ώ¬‘…œ“≤Ω…“‘Ώx™ώ≤ΜΆ§ΒΡΖΫ ΫΘΚΨ’Μ®–ΆΓΔ–«–ΆΓΔΉ‘Ε®Νx–ΆΘ§ΟΩΖNΖΫ ΫΕΦ”–ΤδÉû(y®≠u)»±ϋc(di®Θn)Θ§Ω…“‘Ηυ™ΰ(j®¥)≤ΜΆ§ΒΡκä¬ΖΖ¬’φΫY(ji®Π)Ιϊ¹μ(l®Δi)¥_Ε®ΨΏσwΒΡΏx™ώΖΫ Ϋ.

ΓΓΓΓ2.1.5 –≈Χ•(h®Λo)―”Ώt(delay)

ΓΓΓΓκä¬Ζ÷–÷ΜΡήΑ¥’’“é(gu®©)Ε®ΒΡïr(sh®Σ)–ρΫ” ’îΒ(sh®¥)™ΰ(j®¥)Θ§Ώ^ιL(zh®Θng)ΒΡ–≈Χ•(h®Λo)―”ΏtΩ…Ρή¨ß(d®Θo)÷¬ïr(sh®Σ)–ρΚΆΙΠΡήΒΡΜλ¹yΘ§‘ΎΒΆΥΌΒΡœΒΫy(t®·ng)÷–≤Μïΰ(hu®§)”–Ü•ν}Θ§ΒΪ «–≈Χ•(h®Λo)ΏÖΨâΥΌ¬ Φ”ΩλΘ§ïr(sh®Σ)γäΥΌ¬ ΧαΗΏΘ§–≈Χ•(h®Λo)‘ΎΤςΦΰ÷°ιgΒΡ²ςίîïr(sh®Σ)ιg“‘ΦΑΆ§≤Ϋïr(sh®Σ)ιgΨΆïΰ(hu®§)ΩsΕΧ.ρ¨(q®±)³”(d®Αng)Ώ^ίdΓΔΉΏΨÄΏ^ιL(zh®Θng)ΕΦïΰ(hu®§)“ΐΤπ―”ïr(sh®Σ).±Ίμö‘Ύ‘Ϋ¹μ(l®Δi)‘ΫΕΧΒΡïr(sh®Σ)ιgνA(y®¥)Υψ÷–“ΣùMΉψΥυ”–ιT―”ïr(sh®Σ)Θ§Αϋά®Ϋ®ΝΔïr(sh®Σ)ιgΘ§±Θ≥÷ïr(sh®Σ)ιgΘ§ΨÄ―”ΏtΚΆΤΪ–±. ”…”Ύ²ςίîΨÄ…œΒΡΒ»–ßκä»ίΚΆκäΗ–ΕΦïΰ(hu®§)¨Π(du®§)–≈Χ•(h®Λo)ΒΡîΒ(sh®¥)Ή÷«–™Q°a(ch®Θn)…ζ―”ΏtΘ§Φ”…œΖ¥…δ“ΐΤπΒΡ’ώ éΜΊά@Θ§ ΙΒΟîΒ(sh®¥)™ΰ(j®¥)–≈Χ•(h®Λo)≤ΜΡήùMΉψΫ” ’ΕΥΤςΦΰ’ΐ¥_Ϋ” ’Υυ–η“ΣΒΡïr(sh®Σ)ιgΘ§èΡΕχ¨ß(d®Θo)÷¬Ϋ” ’εe(cu®Α)’`.‘ΎCadenceΒΡ–≈Χ•(h®Λo)Ζ¬’φή¦Φΰ÷–Θ§¨Δ–≈Χ•(h®Λo)ΒΡ―”Ώt“≤Ζ≈‘ΎΖ¥…δΒΡΉ”ÖΔîΒ(sh®¥)÷–Ε»ΝΩΘ§”–SettledelayΓΔswitchdelayΓΔPropdelay.Τδ÷–«ΑÉ…²Ä(g®®)≈cIBISΡΘ–Άéλ(k®¥)÷–ΒΡ€y(c®®)‘΅Ί™(f®¥)ίd”–ξP(gu®Γn)Θ§ Ώ@É…²Ä(g®®)ÖΔîΒ(sh®¥)Ω…“‘Ά®Ώ^ρ¨(q®±)³”(d®Αng)ΤςΦΰΚΆΫ” ’ΤςΦΰΒΡ”Οëτ ÷É‘(c®®)ÖΔîΒ(sh®¥)ΒΟΒΫΘ§ Ω…“‘¨ΔΥϋ²É≈cΖ¬’φΚσΒΡSettledelayΓΔSwitchdelayΦ”“‘±»ί^Θ§»γΙϊ‘ΎSlowΡΘ Ϋœ¬ΒΟΒΫΒΡSwitchdelayΕΦ–Γ”Ύ”΄(j®§)ΥψΒΟΒΫΒΡ÷ΒΘ§≤Δ«“‘ΎFastΒΡΡΘ Ϋœ¬ΒΟΒΫΒΡSwitchdelayΒΡ÷ΒΕΦ¥σ”Ύ”΄(j®§)ΥψΒΟΒΫΒΡ÷ΒΘ§ΨΆΩ…“‘ΒΟ≥ωΈ“²É’φ’ΐ–η“ΣΒΡÉ…²Ä(g®®)ΤςΦΰ÷°ιgΒΡïr(sh®Σ)―”ΖΕ΅ζPropdelay.‘ΎΨΏσwΤςΦΰ≤ΦΖ≈ΒΡïr(sh®Σ)ΚρΘ§»γΙϊΤςΦΰΒΡΈΜ÷Ο≤ΜΚœΏmΘ§‘Ύ¨Π(du®§)ëΣ(y®©ng)ΒΡïr(sh®Σ)―”±μ÷–Ρ«≤ΩΖ÷ïΰ(hu®§)ο@ ΨΦt…ΪΘ§°î(d®Γng)Α―ΤδΈΜ÷Ο’{(di®Λo)’ϊΚœΏmΚσ¨Δïΰ(hu®§)ΉÉ≥…Υ{(l®Δn)…ΪΘ§±μ Ψ–≈Χ•(h®Λo)‘ΎΤςΦΰ÷°ιgΒΡ―”ïr(sh®Σ)“―Ϋ¦(j®©ng)ùMΉψPropdelay“é(gu®©)Ε®ΒΡΖΕ΅ζΝΥ.

ΓΓΓΓ2.2 κä¥≈Φφ»ί–‘(Electro Magnetic Compatibility)‘O(sh®®)”΄(j®§)

ΓΓΓΓκä¥≈Φφ»ίΑϋά®κä¥≈Η…î_ΚΆκä¥≈»Χ ήΘ§“≤ΨΆ «Ώ^ΝΩΒΡκä¥≈ί½…δ“‘ΦΑ¨Π(du®§)κä¥≈ί½…δΒΡΟτΗ–≥ΧΕ»É…²Ä(g®®)ΖΫΟφ. κä¥≈Η…î_”–²ς¨ß(d®Θo)Η…î_ΚΆί½…δΗ…î_É…ΖN.²ς¨ß(d®Θo)Η…î_ «÷Η“‘κäΝςΒΡ–Έ ΫΆ®Ώ^¨ß(d®Θo)κäΫιΌ|(zh®§)Α―“Μ²Ä(g®®)κäΨW(w®Θng)Ϋj(lu®Α)…œΒΡ–≈Χ•(h®Λo)²ς¨ß(d®Θo)ΒΫΝμ“Μ²Ä(g®®)κäΨW(w®Θng)Ϋj(lu®Α)Θ§PCB÷–÷ς“Σ±μ§F(xi®Λn)ûιΒΊΨÄ‘κ¬ïΚΆκä‘¥‘κ¬ï.ί½…δΗ…î_ «÷Η–≈Χ•(h®Λo)“‘κä¥≈≤®ΒΡ–Έ Ϋί½…δ≥ω»ΞΘ§èΡΕχ”ΑμëΒΫΝμ“Μ²Ä(g®®)κäΨW(w®Θng)Ϋj(lu®Α).‘ΎΗΏΥΌPCBΦΑœΒΫy(t®·ng)‘O(sh®®)”΄(j®§)÷–Θ§ΗΏνl–≈Χ•(h®Λo)ΨÄΓΔ–ΨΤ§ΒΡ“ΐΡ_ΓΔΫ”≤εΦΰΒ»ΕΦΩ…Ρή≥…ûιΨΏ”–ΧλΨÄΧΊ–‘ΒΡί½…δΗ…î_‘¥.¨Π(du®§)EMCΒΡ‘O(sh®®)”΄(j®§)Ηυ™ΰ(j®¥)‘O(sh®®)”΄(j®§)ΒΡ÷Ί“Σ–‘Ω…“‘Ζ÷ûιΥΡ²Ä(g®®)¨”¥ΈΘΚΤςΦΰΚΆPCBΦâ(j®Σ)‘O(sh®®)”΄(j®§)Θ§Ϋ”ΒΊœΒΫy(t®·ng)ΒΡ‘O(sh®®)”΄(j®§)Θ§ΤΝ±ΈœΒΫy(t®·ng)‘O(sh®®)”΄(j®§)“‘ΦΑûV≤®‘O(sh®®)”΄(j®§).Τδ÷–ΒΡ«ΑÉ…²Ä(g®®)Ήνûι÷Ί“ΣΘ§ΤςΦΰΚΆPCBΦâ(j®Σ)‘O(sh®®)”΄(j®§)÷ς“ΣΑϋά®”–‘¥ΤςΦΰΒΡΏx™ώΓΔκä¬ΖΑεΒΡ¨”·BΓΔ≤ΦΨ÷≤ΦΨÄΒ».Ϋ”ΒΊœΒΫy(t®·ng)ΒΡ‘O(sh®®)”΄(j®§)÷ς“ΣΑϋά®Ϋ”ΒΊΖΫ ΫΓΔΒΊΉηΩΙΩΊ÷ΤΓΔΒΊ≠h(hu®Δn)¬ΖΚΆΤΝ±Έ¨”Ϋ”ΒΊΒ».‘ΎCadenceΒΡΖ¬’φΙΛΨΏ÷–Θ§κä¥≈Η…î_ΒΡΖ¬’φÖΔîΒ(sh®¥)Ω…“‘‘O(sh®®)÷Ο‘ΎXΓΔYΓΔZ»ΐ²Ä(g®®)ΖΫœρ…œΒΡΨύκxΓΔνl¬ ΒΡΖΕ΅ζΓΔ‘O(sh®®)”΄(j®§)”ύΝΩΓΔΖϊΚœ‰Υ(bi®Γo)€ (zh®≥n)Β».¥ΥΖ¬’φ¨Ό”ΎΚσΖ¬’φΘ§÷ς“Σôzρû(y®Λn) «ΖώΖϊΚœ‘O(sh®®)”΄(j®§)“Σ«σΘ§“ρ¥ΥΘ§‘ΎΉω«ΑΤΎΙΛΉςïr(sh®Σ)Θ§Έ“²ÉΏÄ–η“ΣΑ¥’’κä¥≈Η…î_ΒΡάμ’™»Ξ‘O(sh®®)”΄(j®§)Θ§Ά®≥ΘΒΡΉωΖ® «¨ΔΩΊ÷Τκä¥≈Η…î_ΒΡΗςμ½(xi®Λng)‘O(sh®®)”΄(j®§)“é(gu®©)³tëΣ(y®©ng)”ΟΒΫ‘O(sh®®)”΄(j®§)ΒΡΟΩ²Ä(g®®)≠h(hu®Δn)Ιù(ji®Π)Θ§¨ç(sh®Σ)§F(xi®Λn)‘ΎΗς²Ä(g®®)≠h(hu®Δn)Ιù(ji®Π)…œΒΡ“é(gu®©)³tρ¨(q®±)³”(d®Αng)ΚΆΩΊ÷Τ.

ΓΓΓΓ2.3 κä‘¥Άξ’ϊ–‘(power integrity)‘O(sh®®)”΄(j®§)

ΓΓΓΓ‘ΎΗΏΥΌκä¬Ζ÷–Θ§ κä‘¥ΚΆΒΊΒΡΆξ’ϊ–‘“≤ «“Μ²Ä(g®®)Ζ«≥Θ÷Ί“ΣΒΡ“ρΥΊΘ§ “ρ?y®Λn)ικä‘¥ΒΡΆξ’ϊ–‘ΚΆ–≈Χ?h®Λo)ΒΡΆξ’ϊ–‘ «Οή«–œύξP(gu®Γn)ΒΡ.‘Ύ¥σΕύîΒ(sh®¥)«ι¦rœ¬Θ§”Αμë–≈Χ•(h®Λo)ΜϊΉÉΒΡ÷ς“Σ‘≠“ρ «κä‘¥œΒΫy(t®·ng).»γΘΚΒΊΖ¥è½‘κ¬ïΧΪ¥σΓΔ»ΞώνΚœκä»ί‘O(sh®®)”΄(j®§)≤ΜΚœΏmΓΔΕύκä‘¥ΜρΒΊΤΫΟφΒΊΖ÷Ην≤ΜΚΟΓΔΒΊ¨”‘O(sh®®)”΄(j®§)≤ΜΚœάμΓΔκäΝςΖ÷≈δ≤ΜΨυΒ»ΕΦïΰ(hu®§)éß¹μ(l®Δi)κä‘¥Άξ’ϊ–‘ΖΫΟφΒΡÜ•ν}Θ§“ΐΤπ–≈Χ•(h®Λo)ΒΡΜϊΉÉΕχ”ΑμëΒΫ–≈Χ•(h®Λo)ΒΡΆξ’ϊ–‘.Ϋβ¦QΒΡ÷ς“ΣΥΦ¬Ζ”–¥_Ε®κä‘¥Ζ÷≈δœΒΫy(t®·ng)Θ§¨Δ¥σ≥Ώ¥γκä¬ΖΑεΖ÷Ην≥…éΉâK–Γ≥Ώ¥γΑεΘ§Ηυ™ΰ(j®¥)ΒΊΤΫΟφΖ¥è½‘κ¬ï(Ground Bounce)(ΚÜ(ji®Θn)ΖQΒΊè½)¥_Ε®»Ξώνκä»ίΘ§“‘ΦΑ÷χ―έ”Ύ’ϊ²Ä(g®®)PCBΑεΩΦë]Β»éΉ²Ä(g®®)ΖΫΟφ.

ΓΓΓΓ‘Ύκä¬Ζ÷–”–¥σΒΡκäΝς”Ω³”(d®Αng)ïr(sh®Σ)ïΰ(hu®§)“ΐΤπΒΊè½Θ§»γ¥σΝΩ–ΨΤ§ΒΡίî≥ωΆ§ïr(sh®Σ)ι_ÜΔïr(sh®Σ)Θ§¨Δ”–“Μ²Ä(g®®)ί^¥σΒΡΥ≤ëB(t®Λi)κäΝς‘Ύ–ΨΤ§≈cΑεΒΡκä‘¥ΤΫΟφΝςΏ^Θ§–ΨΤ§Ζβ―b≈cκä‘¥ΤΫΟφΒΡκäΗ–ΚΆκäΉηïΰ(hu®§)“ΐΑl(f®Γ)κä‘¥‘κ¬ïΘ§Ώ@‰”ïΰ(hu®§)‘Ύ’φ’ΐΒΡΒΊΤΫΟφ…œ°a(ch®Θn)…ζκäâΚΒΡ≤®³”(d®Αng)ΚΆΉÉΜ·Θ§Ώ@ΖN‘κ¬ïïΰ(hu®§)”ΑμëΤδΥϋ‘ΣΤςΦΰΒΡ³”(d®Αng)Ής.‘O(sh®®)”΄(j®§)÷–€p–ΓΊ™(f®¥)ίdκä»ίΓΔ‘ω¥σΊ™(f®¥)ίdκäΉηΓΔ€p–ΓΒΊκäΗ–ΓΔ€p…ΌΤςΦΰΆ§ïr(sh®Σ)ι_ξP(gu®Γn)ΒΡîΒ(sh®¥)ΡΩΨυΩ…“‘€p…ΌΒΊè½.”…”ΎΒΊκäΤΫΟφΖ÷ΗνΘ§άΐ»γΒΊ¨”±ΜΖ÷ΗνûιîΒ(sh®¥)Ή÷ΒΊΓΔΡΘîMΒΊΓΔΤΝ±ΈΒΊΒ»Θ§°î(d®Γng)îΒ(sh®¥)Ή÷–≈Χ•(h®Λo)ΉΏΒΫΡΘîMΒΊΨÄÖ^(q®±)”ρïr(sh®Σ)Θ§ΨΆïΰ(hu®§)°a(ch®Θn)…ζΒΊΤΫΟφΜΊΝς‘κ¬ï.Ά§ïr(sh®Σ)Ηυ™ΰ(j®¥)Ώx”ΟΒΡΤςΦΰ≤ΜΆ§Θ§κä‘¥¨”“≤Ω…Ρήïΰ(hu®§)±ΜΖ÷ΗνûιéΉΖN≤ΜΆ§κäâΚ¨”Θ§¥Υïr(sh®Σ)ΒΊè½ΚΆΜΊΝς‘κ¬ïΗϋ–ηΧΊ³eξP(gu®Γn)ΉΔ.‘Ύκä‘¥Άξ’ϊ–‘ΒΡ‘O(sh®®)”΄(j®§)÷–κä‘¥Ζ÷≈δœΒΫy(t®·ng)ΚΆ»Ξώνκä»ίΒΡΏx™ώΚή÷Ί“Σ.“ΜΑψ ΙΒΟκä‘¥œΒΫy(t®·ng)(κä‘¥ΚΆΒΊΤΫΟφ)÷°ιgΒΡΉηΩΙ‘ΫΒΆ‘ΫΚΟ.Ω…“‘Ά®Ώ^“é(gu®©)Ε®Ήν¥σΒΡκäâΚΚΆκäΝςΉÉΜ·ΖΕ΅ζ¹μ(l®Δi)¥_Ε®Έ“²ÉœΘΆϊΏ_(d®Δ)ΒΫΒΡΡΩ‰Υ(bi®Γo)ΉηΩΙΘ§»ΜΚσΆ®Ώ^’{(di®Λo)’ϊκä¬Ζ÷–ΒΡœύξP(gu®Γn)“ρΥΊ Ικä‘¥œΒΫy(t®·ng)Ης≤ΩΖ÷ΒΡΉηΩΙ≈cΡΩ‰Υ(bi®Γo)ΉηΩΙ±ΤΫϋ.¨Π(du®§)”Ύ»Ξώνκä»ίΘ§±ΊμöΩΦë]κä»ίΒΡΦΡ…ζÖΔîΒ(sh®¥)Θ§Ε®ΝΩΒΡ”΄(j®§)Υψ≥ω»Ξώνκä»ίΒΡ²Ä(g®®)îΒ(sh®¥)“‘ΦΑΟΩ²Ä(g®®)κä»ίΒΡ»ί÷ΒΚΆΨΏσwΖ≈÷ΟΈΜ÷ΟΘ§±MΝΩΉωΒΫκä»ί“Μ²Ä(g®®)≤ΜΕύΘ§“Μ²Ä(g®®)≤Μ…Ό.‘ΎCadenceΖ¬’φΙΛΨΏ÷–Θ§¨ΔΫ”ΒΊΖ¥è½ΖQûιΆ§≤Ϋι_ξP(gu®Γn)‘κ¬ï(Simultaneous switch noise)ΓΘ‘ΎΖ¬’φïr(sh®Σ)¨Δκä‘¥ιgΒΡΦΡ…ζκäΗ–ΓΔκä»ίΚΆκäΉηΘ§ “‘ΦΑΤςΦΰΖβ―bΒΡΦΡ…ζκäΗ–ΓΔκä»ίΚΆκäΉηΕΦΉωΩΦë]Θ§ΫY(ji®Π)Ιϊ±»ί^ΖϊΚœ¨ç(sh®Σ)κH«ι¦r.ΏÄΩ…“‘Ηυ™ΰ(j®¥)œΒΫy(t®·ng) Ι”ΟΒΡκä¬Ζνê–Ά≈cΙΛΉςνl¬ Θ§‘O(sh®®)÷ΟΚΟΤΎΆϊΒΡœύξP(gu®Γn)÷Η‰Υ(bi®Γo)ÖΔîΒ(sh®¥)ΚσΘ§”΄(j®§)Υψ≥ωΚœΏmΒΡκä»ί¥σ–Γ“‘ΦΑΉνΦ―ΒΡ≤ΦΖ≈ΈΜ÷ΟΘ§‘O(sh®®)”΄(j®§)ΨΏ”–ΒΆΉηΩΙΒΡΫ”ΒΊΜΊ¬Ζ¹μ(l®Δi)Ϋβ¦Qκä‘¥Άξ’ϊ–‘Ü•ν}ΓΘ

ΓΓΓΓ3 ΗΏΥΌPCBΒΡ‘O(sh®®)”΄(j®§)ΖΫΖ®

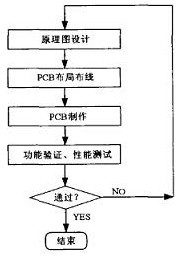

ΓΓΓΓ3.1 ²ςΫy(t®·ng)ΒΡ‘O(sh®®)”΄(j®§)ΖΫΖ®

ΓΓΓΓ»γàD1 «²ςΫy(t®·ng)ΒΡ‘O(sh®®)”΄(j®§)ΖΫΖ®Θ§‘ΎΉνΚσ€y(c®®)‘΅÷°«ΑΘ§¦]”–Ήω»ΈΚΈΒΡΧéάμΘ§Μυ±ΨΕΦ «“άΩΩ‘O(sh®®)”΄(j®§)’ΏΒΡΫ¦(j®©ng)ρû(y®Λn)¹μ(l®Δi)Άξ≥…ΒΡ.‘Ύ¨Π(du®§)‰”ôC(j®©)€y(c®®)‘΅ôzρû(y®Λn)ïr(sh®Σ)≤≈Ω…“‘≤ι’“ΒΫÜ•ν}Θ§¥_Ε®Ü•ν}‘≠“ρ.ûιΝΥΫβ¦QÜ•ν}Θ§ΚήΩ…Ρή”÷“ΣèΡν^ι_ Φ‘O(sh®®)”΄(j®§)“Μ±ι.üo(w®≤)’™ «èΡι_Αl(f®Γ)÷ήΤΎΏÄ «ι_Αl(f®Γ)≥…±Ψ…œΩ¥Θ§Ώ@ΖN÷ς“Σ“άΌ΅‘O(sh®®)”΄(j®§)’ΏΫ¦(j®©ng)ρû(y®Λn)ΒΡΖΫΖ®≤ΜΡήùMΉψ§F(xi®Λn)¥ζ°a(ch®Θn)ΤΖι_Αl(f®Γ)ΒΡ“Σ«σΘ§Ηϋ≤ΜΡήΏmëΣ(y®©ng)§F(xi®Λn)¥ζΗΏΥΌκä¬ΖΗΏèΆ(f®¥)κs–‘ΒΡ‘O(sh®®)”΄(j®§).Υυ“‘±ΊμöΫη÷ζœ»ΏM(j®§n)ΒΡ‘O(sh®®)”΄(j®§)ΙΛΨΏ¹μ(l®Δi)Ε®–‘ΓΔΕ®ΝΩΒΡΖ÷ΈωΘ§ΩΊ÷Τ‘O(sh®®)”΄(j®§)Νς≥Χ.

ΓΓΓΓ3.2 Cadence‘O(sh®®)”΄(j®§)ΖΫΖ®

ΓΓΓΓ§F(xi®Λn)‘Ύ‘Ϋ¹μ(l®Δi)‘ΫΕύΒΡΗΏΥΌ‘O(sh®®)”΄(j®§) «≤…”Ο“ΜΖN”–άϊ”ΎΦ”Ωλι_Αl(f®Γ)÷ήΤΎΒΡΗϋ”––ßΒΡΖΫΖ®.œ» «Ϋ®ΝΔ“ΜΧΉùMΉψ‘O(sh®®)”΄(j®§)–‘Ρή÷Η‰Υ(bi®Γo)ΒΡΈοάμ‘O(sh®®)”΄(j®§)“é(gu®©)³tΘ§Ά®Ώ^Ώ@–©“é(gu®©)³t¹μ(l®Δi)œό÷ΤPCB≤ΦΨ÷≤ΦΨÄ.‘ΎΤςΦΰΑ≤―b÷°«ΑΘ§œ»ΏM(j®§n)––Ζ¬’φ‘O(sh®®)”΄(j®§).‘ΎΏ@ΖNΧ™îM€y(c®®)‘΅÷–Θ§‘O(sh®®)”΄(j®§)’ΏΩ…“‘¨Π(du®§)±»‘O(sh®®)”΄(j®§)÷Η‰Υ(bi®Γo)¹μ(l®Δi)‘u(p®Σng)Ιά–‘Ρή.ΕχΏ@–©ξP(gu®Γn)φIΒΡ«ΑΧα“ρΥΊ «“ΣΫ®ΝΔ“Μ׹ቨΠ(du®§)–‘Ρή÷Η‰Υ(bi®Γo)ΒΡΈοάμ‘O(sh®®)”΄(j®§)“é(gu®©)³tΘ§Εχ“é(gu®©)³tΒΡΜυΒA(ch®≥)”÷ «Ϋ®ΝΔ‘ΎΜυ”ΎΡΘ–ΆΒΡΖ¬’φΖ÷ΈωΚΆ€ (zh®≥n)¥_νA(y®¥)€y(c®®)κäöβΧΊ–‘÷°…œΒΡΘ§Υυ“‘≤ΜΆ§κAΕΈΒΡΖ¬’φΖ÷Έωο@ΒΟΖ«≥Θ÷Ί“Σ.Cadenceή¦ΦΰቨΠ(du®§)ΗΏΥΌPCBΒΡ‘O(sh®®)”΄(j®§)ι_Αl(f®Γ)ΝΥΉ‘ΦΚΒΡ‘O(sh®®)”΄(j®§)Νς≥ΧΘ§»γàD2ΥϋΒΡ÷ς“ΣΥΦœκ «”ΟΚΟΒΡΖ¬’φΖ÷Έω‘O(sh®®)”΄(j®§)¹μ(l®Δi)νA(y®¥)ΖάÜ•ν}ΒΡΑl(f®Γ)…ζΘ§±MΝΩ‘ΎPCB÷ΤΉς«ΑΫβ¦Q“Μ«–Ω…ΡήΑl(f®Γ)…ζΒΡÜ•ν}.≈cΉσΏÖ²ςΫy(t®·ng)ΒΡ‘O(sh®®)”΄(j®§)Νς≥Χœύ±»Θ§Ήν÷ς“ΣΒΡ≤ν³e «‘ΎΝς≥Χ÷–‘ωΦ”ΝΥΩΊ÷ΤΙù(ji®Π)ϋc(di®Θn)Θ§Ω…“‘”––ßΒΊΩΊ÷Τ‘O(sh®®)”΄(j®§)Νς≥Χ.Υϋ¨Δ‘≠άμàD‘O(sh®®)”΄(j®§)ΓΔPCB≤ΦΨ÷≤ΦΨÄΚΆΗΏΥΌΖ¬’φΖ÷ΈωΦ·≥…”Ύ“ΜσwΘ§Ω…“‘Ϋβ¦Q‘Ύ‘O(sh®®)”΄(j®§)÷–Ης²Ä(g®®)≠h(hu®Δn)Ιù(ji®Π)¥φ‘ΎΒΡ≈cκäöβ–‘ΡήœύξP(gu®Γn)ΒΡÜ•ν}.Ά®Ώ^¨Π(du®§)ïr(sh®Σ)–ρΓΔ–≈‘κΓΔ¥°?d®Γng)_ΓΔκä‘¥ΫY(ji®Π)‰΄(g®Αu)ΚΆκä¥≈Φφ»ίΒ»ΕύΖΫΟφΒΡ“ρΥΊΏM(j®§n)––Ζ÷ΈωΘ§Ω…“‘‘Ύ≤ΦΨ÷≤ΦΨÄ÷°«Α¨Π(du®§)œΒΫy(t®·ng)ΒΡ–≈Χ•(h®Λo)Άξ’ϊ–‘ΓΔκä‘¥Άξ’ϊ–‘ΓΔκä¥≈Η…î_Β»Ü•ν}ΉςΉνÉû(y®≠u)ΒΡ‘O(sh®®)”΄(j®§).

ΓΓΓΓàD1 ²ςΫy(t®·ng)ΗΏΥΌ‘O(sh®®)”΄(j®§)Νς≥Χ

ΓΓΓΓàD2 CadenceΗΏΥΌ‘O(sh®®)”΄(j®§)Νς≥Χ

ΓΓΓΓ4 ΫY(ji®Π)’Z(y®≥)

ΓΓΓΓΗΏΥΌPCB‘O(sh®®)”΄(j®§) «“Μ²Ä(g®®)ΚήèΆ(f®¥)κsΒΡœΒΫy(t®·ng)ΙΛ≥ΧΘ§÷Μ”–Ϋη÷ζ”ΎΡ«–©≤ΜÉHΡή”΄(j®§)Υψ‘O(sh®®)”΄(j®§)÷–”ΟΒΫΒΡΟΩ²Ä(g®®)‘ΣΤςΦΰΒΡΈοάμΧΊ–‘ΚΆκäöβΧΊ–‘ΒΡ”ΑμëΦΑΤδœύΜΞΉς”ΟΘ§ΏÄ±ΊμöΡήèΡ‘O(sh®®)”΄(j®§)ΒΡPCB÷–Ή‘³”(d®Αng)Χα»ΓΚΆΫ®ΝΔΡΘ–ΆΘ§≤Δ«“ΨΏ”–ΧαΙ©¨Π(du®§)¨ç(sh®Σ)κH‘O(sh®®)”΄(j®§)≤ΌΉς°a(ch®Θn)…ζ³”(d®Αng)ëB(t®Λi)ΧΊ–‘Οη ωΒΡΖ¬’φΤςΒ»èä(qi®Δng)¥σΙΠΡήΒΡEDAή¦ΦΰΙΛΨΏΘ§≤≈ΡήΗϋ»ΪΟφΒΊΫβ¦Q“‘…œ–≈Χ•(h®Λo)Άξ’ϊ–‘ΓΔκä¥≈Η…î_ΓΔκä‘¥Άξ’ϊ–‘Β»Ü•ν}.‘ΎΨΏσw‘O(sh®®)”΄(j®§)Ώ^≥Χ÷–Θ§‘ΎôMœρ…œ“Σ«σΗς≤ΩΖ÷ΒΡ‘O(sh®®)”΄(j®§)»ΥÜTΆ®ΝΠΚœΉςΘ§‘ΎΩvœρ…œ“Σ«σ‘O(sh®®)”΄(j®§)ΒΡΗς²Ä(g®®)κAΕΈΨCΚœΩΦë]Θ§Α―‘O(sh®®)”΄(j®§)ΚΆΖ¬’φΊû¥©”Ύ’ϊ²Ä(g®®)‘O(sh®®)”΄(j®§)Ώ^≥ΧΘ§¨ç(sh®Σ)§F(xi®Λn)Ώ^≥ΧΒΡΩ…ΩΊ–‘Θ§ΨΏσw÷Η‰Υ(bi®Γo)ΒΡΝΩΜ·.÷Μ”–Ώ@‰”≤≈ΡήΉωΒΫΗΏ–ßΒΡ‘O(sh®®)”΄(j®§).

]]>»Ϊ«ρκäΉ”‘O(sh®®)”΄(j®§)³™(chu®Λng)–¬νI(l®Ϊng)œ»Τσ‰I(y®®)Cadence‘O(sh®®)”΄(j®§)œΒΫy(t®·ng)ΙΪΥΨΘ§ΫώΧλ–ϊ≤ΦΆΤ≥ωΤδΉν–¬ΑφCadence? Allegro? ≈c OrCAD?”ΓΥΔκä¬Ζ(PCB) ή¦ΦΰΘ§Υϋ™μ”–ΒΡ»Ϊ–¬ΙΠΡή≈cΧΊ–‘ΡήâρΧαΗΏPCBΙΛ≥ΧéüΒΡΩÉ(j®©)–ß≈c–߬ ΓΘAllegro≈cOrCAD PCB Design 16.3Αφ±ΨûιPCBΙΛ≥Χéüéß¹μ(l®Δi)ΝΥ‰O¥σΒΡ–¬Éû(y®≠u)³ί(sh®§)Θ§Αϋά®ΗΡΏM(j®§n)ΫKΕΥ°a(ch®Θn)ΤΖ–Γ–ΆΜ·‘O(sh®®)”΄(j®§)ΡήΝΠ≤Δ€p…Ό‘≠–ΆôC(j®©)‘O(sh®®)”΄(j®§)ΒΡΖ¥èΆ(f®¥)¥ΈîΒ(sh®¥)Θ§ ΙΒΟ‘O(sh®®)”΄(j®§)÷ήΤΎΗϋΨΏΩ…νA(y®¥)€y(c®®)–‘ΓΘ

±ΨΑφ±ΨΑϋά®“Μ–©–¬‘ωΙΠΡήΚΆΜΞΏBΟήΕ»ΒΡΗΡΏM(j®§n)Θ§»γ³²?c®®)α≤ΦΨÄΘ§îU(ku®Α)’ΙΒΡΗΏΟήΕ»ΜΞΏBΘ®HDIΘ©“é(gu®©)³tΓΔPCBΒΡ»ΐΨSΘ®3DΘ©ο@ Ψ≈cRFκä¬ΖΒΡΖ«¨Π(du®§)ΖQ±ήΉ¨ΓΘΆΊ’ΙΒΡΈΔΩΉ·B¨”“é(gu®©)³t‘ ‘S”Οëτ³™(chu®Λng)Ϋ®‰OûιèΆ(f®¥)κsΒΡHDI‘O(sh®®)”΄(j®§)Θ§Εχ≈c»α–‘ΑείÜάΣΈ«ΚœΒΡΕύΨÄ Ϋ«ζ–ΈΩ²ΨÄ≤ΦΨÄïΰ(hu®§)Φ”Ωλ³²?c®®)α‘O(sh®®)”΄(j®§)ΓΘ¥ΥΆβΘ§Φ·≥…ΒΡ3D PCBûg”[ΤςΉ¨‘O(sh®®)”΄(j®§)éüΩ…“‘Ω¥ΒΫ‘ΣΦΰ≈cHDIΈΔ¨ß(d®Θo)ΩΉÉ»(n®®i)≤ΩΘ§èΡΕχûιôC(j®©)–Β‘O(sh®®)”΄(j®§)àF(tu®Δn)ξ†(du®§)œϊ≥ΐΝΥ≤Μ±Ί“ΣΒΡΒϋ¥ζΓΘAllegro PCB RFΏxΦΰΏÄΆ®Ώ^ Ι”Ο“Μ²Ä(g®®)ΜρΕύ²Ä(g®®)RF‘ΣΦΰΒΡΖ«¨Π(du®§)ΖQ±ήΉ¨éΆ÷ζΙΛ≥ΧéüΦ”Ωλ³™(chu®Λng)Ϋ®ΨΪ¥_RFκä¬ΖΒΡΥΌΕ»ΓΘ

ΓΑΈ“²ÉÖΔ≈cΝΥ16.3Αφ±ΨΒΡΕύ²Ä(g®®)κAΕΈΒΡ€y(c®®)‘΅Θ§¨Π(du®§)Τδ”ΓœσΖ«≥Θ…νΩΧΘ§Γ± Kaleidescape CanadaΙΪΥΨΗΏΦâ(j®Σ)PCB‘O(sh®®)”΄(j®§)éüVincent Di Lello’fΓΘΓΑΏ@²Ä(g®®)–¬Αφ±ΨΒΡΗΡΝΦΚήΚΟΒΊΫβ¦QΝΥΈ“²ÉΒΡ–Γ–ΆΜ·‘O(sh®®)”΄(j®§)Ü•ν}Θ§Έ“²ÉΤΎ¥ΐ÷χΏ@²Ä(g®®)–¬Αφ±ΨΑl(f®Γ)≤ΦΚσΡήâρ±MΩλ¨ΔΤδëΣ(y®©ng)”Ο”ΎΈ“²ÉΒΡ‘O(sh®®)”΄(j®§)Νς≥Χ÷–ΓΘΓ±

–¬ΑφAllegro≈cOrCAD Ι”ΟΕύκAΕΈνA(y®¥)Αl(f®Γ)≤ΦΒΡΖΫ Ϋ¥_±ΘÉ»(n®®i)»ί≈cΌ|(zh®§)ΝΩΡήâρΖϊΚœΩΆëτΒΡ–η“ΣΓΘ¹μ(l®Δi)Ή‘±±ΟάΓΔöW÷όΓΔ¹Ü÷όΚΆ»’±ΨΒΡ20ΕύΦ“ΩΆëτÖΔ≈cΝΥΕύκAΕΈ€y(c®®)‘΅”΄(j®§)³ùΓΘÖΔ≈c€y(c®®)‘΅”΄(j®§)³ùΒΡΩΆëτ≈cCadenceΒΡΚœΉςΜοΑιΑϋά®NVIDIAΓΔEmersonΓΔKaleidescapeΓΔFreedom CADΓΔNordCADΓΔFlowCADΓΔGraser≈cTektronixΓΘ

16.3Αφ±Ψ÷–ΏÄΑϋΚ§¨Π(du®§)OrCADœΒΝ–°a(ch®Θn)ΤΖëΣ(y®©ng)”Ο–ß¬ ≈cΩ…”Ο–‘ΒΡ“ΜœΒΝ–¥σΖυΗΡΝΦΓΘάΐ»γOrCAD Capture CIS»γΫώΧαΙ©ΝΥΉ‘³”(d®Αng)≤ΦΨÄΙΠΡή“‘―ΗΥΌ‘ωΦ”ΏBΨÄΘ§ΏÄ”–»Ϊ–¬ΒΡ»ΐΨSΖβ―bο@ ΨΙΠΡήΓΘOrCAD PCB EditorΧαΙ©ΝΥ»ΐΨS≤ιΩ¥≈cΓΑΖ≠ΑεΓ±‘O(sh®®)”΄(j®§)/Ψéί΄“‘ΦΑÜΈΟφPCB‘O(sh®®)”΄(j®§)ΒΡΧχΨÄ÷ß≥÷ΓΘOrCAD Signal Explorer”–“Μ²Ä(g®®)Ϋ¦(j®©ng)ΗΡΝΦΒΡ”ΟëτΫγΟφΘ§”–ΆœΉßΚΆèΆ(f®¥)÷Τ’≥ΌNΙΠΡήΘ§”–«ΑΚσξP(gu®Γn)¬™(li®Δn)ΒΡ”“™τΙΠΡή≤Δ÷ß≥÷±ΨΒΊIBISΡΘ–ΆΓΘ

Ω…”Ο–‘ΗΡΏM(j®§n) «–¬ΑφAllegro PCB–≈Χ•(h®Λo)≈cκä‘¥Άξ’ϊ–‘ή¦ΦΰΒΡ”÷“Μ²Ä(g®®)÷Ίϋc(di®Θn)Θ§ΥϋΧαΙ©ΝΥ“Μ²Ä(g®®)»Ϊ–¬ΒΡ”ΟëτΫγΟφΘ§≤ΔûινA(y®¥)≤ΦΨÄΖ÷Έω≠h(hu®Δn)Ψ≥‘ωΦ”ΝΥ·B¨”Η–÷ΣΙΠΡήΓΘΆ®Ώ^¨Π(du®§)±ΨΒΊIBIS≈cSPICEΡΘ–ΆΑϋά®Cadence Virtuoso? Spectre? κä¬ΖΖ¬’φΡΘ–ΆΒΡ÷ß≥÷Θ§ I/OΨè¦_ΤςΫ®ΡΘ‰Υ(bi®Γo)€ (zh®≥n)“≤ΑϋΚ§‘ΎΤδ÷–ΓΘΝμΆβ“Μ²Ä(g®®)ΗΡΏM(j®§n)‘O(sh®®)”΄(j®§)÷ήΤΎΙήάμΒΡΒΊΖΫ «Ρήâρ”Ο¥σΝΩΦΣ±»ΧΊΦâ(j®Σ)–≈Χ•(h®Λo)ΩλΥΌ£ΏΟηPCBΘ§≤Δ«“―ΗΥΌ¥_Ε®ëΣ(y®©ng)‘™‘ΎΡΡάοΏM(j®§n)––‘îΦö(x®§)Ζ÷ΈωΘ§–≈Χ•(h®Λo)ïΰ(hu®§)Ηυ™ΰ(j®¥)Τδ–≈‘κ±»ΏM(j®§n)––≈≈Ν–ΓΘ

ΓΑΏ@²Ä(g®®)Ήν–¬ΑφAllegro”–ΚήΕύΒΡΗΡΏM(j®§n)Θ§ΡήâρΫβ¦Q³²–‘Μρ³²?c®®)α‘O(sh®®)”΄(j®§)…œΒΡ–Γ–ΆΜ·‘O(sh®®)”΄(j®§)Ü•ν}Θ§Γ±Freedom CAD Ήœ·Ώ\(y®¥n)†I(y®Σng)ΙΌScott Miller’fΓΘΓΑΉςûι“ΜΦ“‘O(sh®®)”΄(j®§)Ζΰ³’(w®¥)ΙΪΥΨΘ§Έ“²É“Μ÷±Κή”–≈d»ΛΧαΗΏΈ“²É?c®®)O(sh®®)”΄(j®§)éüΒΡ–ß¬ ΚΆ‘O(sh®®)”΄(j®§)÷ήΤΎΒΡΩ…νA(y®¥)€y(c®®)–‘ΓΘΈ“²É¨Δïΰ(hu®§)όD(zhu®Θn)“ΤΒΫ16.3Αφ±ΨΘ§“≤ΆΤΥ]Έ“²ÉΒΡΩΆëτ±MΩλόD(zhu®Θn)“ΤΓΘΓ±

‘™Αφ±ΨΫβ¦QΒΡΝμΆβ“Μ–©÷Ί“ΣÜ•ν} «≈c≤ΩΦΰîΒ(sh®¥)™ΰ(j®¥)Ιήάμ”–ξP(gu®Γn)ΓΘΦ·≥…ΒΡECADΓΔMCAD≤ΩΦΰ³™(chu®Λng)Ϋ®Θ§…ζ≥…≈cΑl(f®Γ)≤ΦΩ…“‘ΫΒΒΆ≤Μ±Ί“ΣΒΡ‘≠–ΆôC(j®©)≥ω‰”¥ΈîΒ(sh®¥)ΓΘΏ@²Ä(g®®)–¬≤ΩΦΰ¨ß(d®Θo)»κΙΠΡήΩ…“‘îU(ku®Α)’ΙνA(y®¥)Αl(f®Γ)≤Φ≈c≈Rïr(sh®Σ)≤ΩΦΰΒΡΙήάμ≈cΆ®÷ΣΘ§ΩsΕΧ‘O(sh®®)”΄(j®§)÷ήΤΎΓΘ¥ΥΆβΘ§ΙΛ≥ΧéüΩ…“‘Ά®Ώ^ Ι”Ο≈ζ€ (zh®≥n)ΒΡ≈cΆΤΥ]ΒΡ≤ΩΦΰΧφ™Q‘≠¹μ(l®Δi)ΒΡ≤ΩΦΰ¹μ(l®Δi)¨ç(sh®Σ)§F(xi®Λn)Ή‘³”(d®Αng)≤ΩΦΰΗϋ–¬Θ§“≤Ω…“‘Ά®Ώ^èU½â≤ΩΦΰΗζέô“‘¥_±Θ°a(ch®Θn)ΤΖΒΡΌ|(zh®§)ΝΩΓΘ

Allegro≈cOrCAD PCB Design 16.3Αφ¨Δ”Ύ2009Ρξ12‘¬≥θι_ ΦœρΩΆëτΧαΙ©œ¬ίdΓΘ

]]>SPB15.2 CD1ΓΪ3Θ§Α≤―b1ΓΔ2Θ§ΒΎ3ûιéλ(k®¥)Θ§≤ΜΑ≤―b

LicenseΑ≤―bΘΚ

‘O(sh®®)÷Ο≠h(hu®Δn)Ψ≥ΉÉΝΩlm_license_file D:Cadencelicense.dat

–όΗΡlicense÷–SERVER yyh ANY 5280ûιSERVER zeng ANY 5280

ΕΰΓΔ”ΟDesign Entry CIS(Capture)‘O(sh®®)”΄(j®§)‘≠άμàD

ΏM(j®§n)»κDesign Entry CIS Studio

‘O(sh®®)÷Ο≤ΌΉς≠h(hu®Δn)Ψ≥OptionsPreferencses:

ν¹…ΪΘΚcolors/Print

ΗώΉ”ΘΚGrid Display

κsμ½(xi®Λng)ΘΚMiscellaneous

.........≥Θ»ΓΡ§’J(r®®n)÷Β

≈δ÷Ο‘O(sh®®)”΄(j®§)àDΦàΘΚ

‘O(sh®®)Ε®ΡΘΑεΘΚOptionsDesign Template:Θ®ëΣ(y®©ng)”Ο”Ύ–¬àDΘ©

‘O(sh®®)Ε®°î(d®Γng)«ΑàDΦàOptionsSchematic Page Properities

³™(chu®Λng)Ϋ®–¬‘O(sh®®)”΄(j®§)

³™(chu®Λng)Ϋ®‘ΣΦΰΦΑ‘ΣΦΰéλ(k®¥)

FileNewLibrary(...Labrary1.OLB)

DesignNew Part...(New Part Properties)

Parts per 1/2/..(Ζβ―bœ¬‘ΣΦΰΒΡ²Ä(g®®)îΒ(sh®¥))

Pakage Type:Θ®÷Μ”–“Μ²Ä(g®®)‘ΣΦΰïr(sh®Σ)Θ§≤ΜΤπΉς”ΟΘ©

Homogeneous:èΆ(f®¥)ΚœΖβ―b‘ΣΦΰ÷–Θ®Εύ²Ä(g®®)‘ΣΦΰàDΫM≥…ïr(sh®Σ)Θ©ΟΩ²Ä(g®®)‘ΣΦΰàDΕΦ“Μ‰”Θ®defaultΏm”Ο”Ύ‰Υ(bi®Γo)€ (zh®≥n)Ώâί΄Θ©

Heterogeneous:èΆ(f®¥)ΚœΖβ―b‘ΣΦΰΘ®Εύ²Ä(g®®)‘ΣΦΰàDΫM≥…ïr(sh®Σ)Θ©÷– Ι”Ο≤Μ“Μ‰”ΒΡ‘ΣΦΰàD(ί^Ώm”Ο”Ύ¥σ‘ΣΦΰ)

“Μ²Ä(g®®)Ζβ―bœ¬Εύ²Ä(g®®)‘ΣΦΰàDΘ§“‘View ext part(previous part)«–™Q“ïàD

Part Numbering:

Alphabetic/numeric

Place(PIN...Rectangle)

Ϋ®ΝΔμ½(xi®Λng)ΡΩFileNewProject

Schematic ew page (Ω…“‘ΕύèààDΘΚ

ÜΈ¨”¥Έκä¬ΖàDιgΘ§“‘œύΆ§ΟϊΖQΒΡΓΑκä¬ΖΕΥΩΎΏBΫ”ΤςΓ±off-page connectorΏBΫ”

¨”¥Έ Ϋκä¬ΖàDΘΚ“‘ΖΫâKàDΘ®¨”¥ΈâKHierarchical Block...Θ©¹μ(l®Δi)¥ζΧφ¨ç(sh®Σ)κHκä¬ΖΒΡκä¬ΖàDΘ§“‘œύΆ§ΟϊΖQPortΒΡ≈δ¨Π(du®§)É»(n®®i)¨”κä¬ΖΘ§É»(n®®i)¨”κä¬Ζ÷°ιgΩ…“‘ΕύèàΘ§Ά§ÜΈ¨”ΏBΫ”

άL÷Τ‘≠άμàD

Ζ≈÷Ο‘ΣΤςΦΰΘΚPlace

‘ΣΦΰΘΚPartΘ®¹μ(l®Δi)Ή‘Libraries,œ»“ΣΧμΦ”éλ(k®¥)Θ©

κä‘¥ΚΆΒΊΘ®power gndΘ©

ΏBΫ”ΨĬΖ

wire

busΘΚ≈cwire÷°ιg±Ίμö“‘÷ßΨÄΏBΫ”Θ§≤Δ“‘ΨW(w®Θng)‰Υ(bi®Γo)(net alias)¨Π(du®§)ëΣ(y®©ng)Θ®wire:D0Θ§D1....D7;bus:D[0..7]Θ©

îΒ(sh®¥)™ΰ(j®¥)Ω²ΨÄΚΆîΒ(sh®¥)™ΰ(j®¥)Ω²ΨÄΒΡ“ΐ≥ωΨıΊμöΕ®Νxnet alias

–όΗΡ‘ΣΦΰ–ρΧ•(h®Λo)ΚΆ‘ΣΦΰ÷Β

³™(chu®Λng)Ϋ®Ζ÷Φâ(j®Σ)ΡΘâKΘ®Εύèàκä¬ΖàDΘ©

ΤΫΧΙ ΫΘ®ÜΈ¨”¥ΈΘ©κä¬ΖΘΚΗςκä¬Ζ÷°ιg–≈Χ•(h®Λo)ΏBΫ”Θ§“‘œύΆ§ΟϊΖQΒΡoff-page connectorΏBΫ”

¨”¥Έ Ϋκä¬ΖàDΘΚ“‘ΖΫâKàDΘ®¨”¥ΈâKHierarchical Block...Θ©¹μ(l®Δi)¥ζΧφ¨ç(sh®Σ)κHκä¬ΖΒΡκä¬ΖàDΘ§“‘œύΆ§ΟϊΖQPortΒΡ≈δ¨Π(du®§)É»(n®®i)¨”κä¬ΖΘ§É»(n®®i)¨”κä¬Ζ÷°ιgΩ…“‘ΕύèàΘ§Ά§ÜΈ¨”ΏBΫ”

‰Υ(bi®Γo)ν}ôΎΧéάμΘΚ

“ΜΑψ“―”–‰Υ(bi®Γo)ν}ôΎΘ§ΧμΦ”ΘΚPlaceTitle BlockΘ®Θ©

PCB¨”νA(y®¥)Χéάμ

‘ΣΦΰΒΡ¨Ό–‘

Ψéί΄‘ΣΦΰ¨Ό–‘

‘Ύ¨ß(d®Θo)»κPCB÷°«ΑΘ§±Ίμö’ΐ¥_Χν¨ë‘ΣΦΰΒΡΖβ―bΘ®PCB FootprintΘ©

ÖΔîΒ(sh®¥)’ϊσwΌx÷ΒΘ®ΩρΉΓΕύ²Ä(g®®)‘ΣΦΰΘ§»ΜΚσEdit PropertiesΘ©

Ζ÷νê¨Ό–‘Ψéί΄

Edit PropertiesNew ColumnClass:IC(IC,IO,Discrete»ΐνêΘ§‘ΎPCB÷–Ζ÷νêΖ≈÷Ο)

Ζ≈÷ΟΕ®ΝxΖΩιgΘ®RoomΘ©

Edit PropertiesNew ColumnRoom

ΧμΦ”ΈΡ±ΨΚΆàDœώ

ΧμΦ”ΈΡ±ΨΓΔΈΜàDΘ®Place...Θ©

‘≠άμàDάL÷ΤΒΡΚσάm(x®¥)ΧéάμΘ®«–™QΒΫμ½(xi®Λng)ΡΩΙήάμΤς¥ΑΩΎΘ§Ώx÷–*.DSNΈΡΦΰΘ§»ΜΚσΏM(j®§n)––ΚσΧéάμΓΣΓΣΓΣΓΣDRCôz≤ιΓΔ…ζ≥…ΨW(w®Θng)±μΦΑ‘ΣΤςΦΰ«εÜΈΘ©

‘O(sh®®)”΄(j®§)“é(gu®©)³tôz≤ιΘ®ToolsDesign Rules Check...Θ©

Design Rules Check

scope(ΖΕ΅ζ):entireΘ®»Ϊ≤ΩΘ©/selectionΘ®ΥυΏxΘ©

Mode(ΡΘ Ϋ)ΘΚ

occurences( ¬ΦΰΘΚ‘ΎΆ§“ΜάLàDμ™(y®®)É»(n®®i)Ά§“Μ¨ç(sh®Σ)σw≥ω§F(xi®Λn)Εύ¥ΈΒΡ¨ç(sh®Σ)σwκä¬ΖΘ©

instance(¨ç(sh®Σ)σwΘΚάLàDμ™(y®®)É»(n®®i)ΒΡ‘ΣΦΰΖϊΧ•(h®Λo))

»γ“ΜèΆ(f®¥)κs¨”¥Έκä¬ΖΘ§Ρ≥Ή”ΖΫâKκä¬Ζ÷ΊèΆ(f®¥) Ι”Ο3¥ΈΘ§ΨΆ–Έ≥…3¥Έ ¬ΦΰΘΜΉ”ΖΫâKκä¬ΖÉ»(n®®i)±Ψ…μΒΡ‘ΣΦΰ³t «¨ç(sh®Σ)σwΓΘ

ActionΘ®³”(d®Αng)ΉςΘ©ΘΚcheck design rules/delete DRC

ReportΘ®àσ(b®Λo)ΗφΘ©ΘΚ

Create DRC markers for warn(‘Ύεe(cu®Α)’`÷°ΧéΖ≈÷ΟΨ·Ηφ‰Υ(bi®Γo)”¦)

Check hierarchical port connection(¨”¥Έ ΫΕΥΩΎΏBΫ”)

Check off-page connector connection(ΤΫΧΙ ΫΕΥΩΎΏBΫ”)

Report identical part referenves(ôz≤ι÷ΊèΆ(f®¥)ΒΡ‘ΣΦΰ–ρΧ•(h®Λo))

Report invalid package (ôz≤ιüo(w®≤)–ßΒΡΖβ―b)

Report hierarchical ports and off-page connector(Ν–≥ωportΚΆoff-page ΏBΫ”)

Check unconnected net

Check SDT compatible

Report all net names

View output

ERC Matrix

‘ΣΦΰΉ‘³”(d®Αng)ΨéΧ•(h®Λo)Θ®ToolsAnnotateΘ©

scopeΘΚUpdate entire design/selection

ActionΘΜ

Incremental/unconfitional reference update

reset part reference to "?"

Add/delete Intersheet ReferenceΘ®‘ΎΖ÷μ™(y®®)àDΦàΒΡΕΥΩΎΒΡ–ρΧ•(h®Λo)Φ”…œ/³h≥ΐàDΦàΒΡΨéΧ•(h®Λo)Θ©

Combined property

Reset reference numbers to begin at 1 each page

Do not change the page number

Ή‘³”(d®Αng)Ηϋ–¬ΤςΦΰΜρΨW(w®Θng)Ϋj(lu®Α)ΒΡ¨Ό–‘Θ®ToolsUpdate Properties...Θ©

scopeΘΚUpdate entire design/selection

ActionΘΚ

use case inseneitive compares

convert the update property to uppercase

ynconditionally update the property

Do not change updated properties visibility

Cadence±μ ΨΘ§Βδ–ΆΗΏΥΌΑε‘O(sh®®)”΄(j®§)÷– ήΦs χΨÄΨW(w®Θng)ΒΡîΒ(sh®¥)ΝΩ“―Ϋ¦(j®©ng)èΡ’ΦΩ²ΨÄΨW(w®Θng)ΒΡ25%ΦΛ‘ωΒΫ75%“‘…œΓΘ‘O(sh®®)”΄(j®§)ξ†(du®§)Έι÷–SIΙΛ≥ΧéüΒΡ»Έ³’(w®¥) «Ζ÷ΈωΏ@–©ΨÄΨW(w®Θng)ΓΘΒΪ «Θ§ κS÷χ–η“ΣΖ÷ΈωΒΡΑε…œΨÄΨW(w®Θng)îΒ(sh®¥)ΝΩΦΑ–¬–ΨΤ§èΆ(f®¥)κs–‘ΒΡΩλΥΌ‘ωΦ”Θ§Ώ@ΖN»Έ³’(w®¥)“≤‘ΎΩλΥΌ‘ωΦ”ΓΘ”…”Ύ‘ ‘SκäöβΙΛ≥Χéüüo(w®≤)–η“άΌ΅SIΙΛ≥ΧéüΖ÷ΈωΥυ”– ήΦs χΨÄΨW(w®Θng)Φ¥Ω…ι_Αl(f®Γ)≤ΔΙήάμΤδ‘O(sh®®)”΄(j®§)÷–ΒΡΦs χΘ§“ρ¥ΥSPECCTRAQuest EE÷ß≥÷ΒΡ–¬ΒΡ‘O(sh®®)”΄(j®§)ΖΫΖ®Θ§ΧαΗΏΝΥ‘O(sh®®)”΄(j®§)ξ†(du®§)ΈιΒΡ–ß¬ Θ§ΫΒΒΆ¨Π(du®§)»Έ³’(w®¥)Ζ±÷ΊΒΡSIΙΛ≥ΧéüΒΡ“άΌ΅Θ§Ά®Ώ^ ΙκäöβΙΛ≥ΧéüΡήâρι_Αl(f®Γ)ΚΆΙήάμΥϊ²É?c®®)O(sh®®)”΄(j®§)÷–ΒΡκäöβ“é(gu®©)³tΕχ≤Μ–η“άΩΩSIΙΛ≥ΧéüΖ÷ΈωΥυ”––η“Σ“é(gu®©)³tΦs χΒΡΨW(w®Θng)Ϋj(lu®Α)Θ§¨ΔΡήâρΚήΚΟΒΊΩΊ÷ΤΗΫΦ”≥…±ΨΓΘ

™ΰ(j®¥)ΫιΫBΘ§§F(xi®Λn)‘Ύ‘O(sh®®)”΄(j®§)àF(tu®Δn)ξ†(du®§)±Ίμö¥_Ε® ήΦs χΒΡΨW(w®Θng)ϋc(di®Θn)≤ΔΑ―Υϋ²ÉΖ÷≥…É…ΫMΘΚ‘O(sh®®)”΄(j®§)―≠≠h(hu®Δn)Υυ±Ί–η«“–η“ΣSIΩλΥΌρû(y®Λn)ΉCΒΡΨW(w®Θng)ϋc(di®Θn)Θ§“‘ΦΑ≤Μ÷Ί“ΣΒΡΓΔüo(w®≤)–ηρû(y®Λn)ΉCΒΡΨW(w®Θng)ϋc(di®Θn)ΓΘΏ@ΖN¨ç(sh®Σ)έ`Ά®≥Θ“βΈΕ÷χ“ΣΟ¥Ώ^Ε…Φs χΡ«–©≤ΜΧΪ÷Ί“ΣΒΡΨW(w®Θng)ϋc(di®Θn)Θ§“ΣΟ¥Ηυ±Ψ≤ΜΏM(j®§n)––ΩΊ÷ΤΘ§“ρ¥Υïΰ(hu®§)ΧαΗΏκä¬ΖΑεΒΡ≥…±ΨΓΘ°î(d®Γng)Ά®Ώ^Ώ@ΖNΖΫ ΫΙήάμξP(gu®Γn)φIΨW(w®Θng)ϋc(di®Θn)ïr(sh®Σ)Θ§κä¬ΖΑε≥ωΙ ’œΒΡοL(f®Ξng)κU(xi®Θn)ïΰ(hu®§)‘ωΦ”Θ§èΡΕχ‘λ≥…≤ΜΩ…±ήΟβΒΡΑΚΌFΒΡ÷ΊèΆ(f®¥)ΝςΤ§ΓΘSPECCTRAQuest EE ΙκäöβΙΛ≥ΧéüΡήâρ¥_Ε®«ΑΕΥ≤ΜΧΪξP(gu®Γn)φIΒΡΨW(w®Θng)ϋc(di®Θn)ΒΡΉνΦ―Φs χΘ§Ά§ïr(sh®Σ)SIΙΛ≥Χéü“≤ΡήâρΑ―ΉΔ“βΝΠΦ·÷–ΒΫ–¬ΒΡ–ΨΤ§ΫMΚΆΖ«≥ΘξP(gu®Γn)φIΒΡΨW(w®Θng)ϋc(di®Θn)Θ§èΡΕχΙù(ji®Π) Γïr(sh®Σ)ιgΚΆΌYΫπΓΘ

SPECCTRAQuest EEΉςûιΖ¬’φΙΛΨΏΑϋΘ§ΑϋΚ§ΝΥΖ÷Φâ(j®Σ)Φs χΙήάμΤς(Constraint Manager)ΦΑSigXploreràD–ΈΜ·ΆΊ?f®¥)δΘ§ΝμΆβΏÄ≈cΆξ’ϊΒΡCadenceΦs χρ¨(q®±)³”(d®Αng)ΒΡΗΏΥΌ‘O(sh®®)”΄(j®§)Νς≥ΧΨoΟήΦ·≥…Θ§ΤδΑϋΚ§”Ο”ΎΗΏΥΌ‘O(sh®®)”΄(j®§)ΦΑΖ÷ΈωΒΡSPECCTRAQuest SI ExpertΓΔ”Ο”ΎàD–Έίî»κΒΡConcept HDLΓΔ”Ο”Ύ≤ΦΨÄΒΡAllegroΓΔ”Ο”ΎΉ‘³”(d®Αng)≤ΦΨÄΒΡSPECCTRAΓΔ“‘ΦΑ”Ο”ΎΕ®ΝxΓΔΙήάμΚΆρû(y®Λn)ΉC’ϊ²Ä(g®®)Νς≥Χ÷–Φs χΒΡConstraint ManagerΓΘ≤…”ΟSigXplorerΒΡκäöβΙΛ≥ΧéüΚΆSIΙΛ≥ΧéüΩ…“‘¨ç(sh®Σ)ïr(sh®Σ)Ι≤œμΦs χΡΘΑεΘ§Αϋά®”Ο”Ύ÷ς³”(d®Αng)ΓΔ³”(d®Αng)ëB(t®Λi)Öf(xi®Π)ΉςΒΡèΆ(f®¥)κsΆΊ?f®¥)δι_Αl(f®Γ)Θ§Ζ÷ΈωΓΘSPECCTRAQuest EEΏÄûικäöβΙΛ≥ΧéüΧαΙ©–¬ΒΡSIΖ÷ΈωΖΫΖ®÷ΗΡœΘ§ ΙΥϊ²ÉΡήâρΩλΥΌι_ ΦΦs χι_Αl(f®Γ)ΓΘ

]]>

CadenceΙΪ≤ΦΝΥVirtuoso Multi-Mode Simulation(MMSIM)ΒΡ6.2ΑφΘ§‘ΎΙ≤œμ‘SΩ…ôύ(qu®Δn)Α≤≈≈œ¬Φ{»κΝΥSpiceΓΔFast SpiceΓΔRFΚΆΜλΚœ–≈Χ•(h®Λo)Ζ¬’φΤςΓΘ‘™ΖΫΑΗ≥–÷ZΨΏ”–Ά®”ΟΒΡΨW(w®Θng)±μΚΆΡΘ–ΆΦ·≥…îΒ(sh®¥)™ΰ(j®¥)éλ(k®¥)Θ§‘ ‘S‘O(sh®®)”΄(j®§)éüèΡ“ΜΖNΖ¬’φ“ΐ«φ«–™QΒΫΝμ“ΜΖNΘ§≤Μïΰ(hu®§)°a(ch®Θn)…ζΦφ»ί–‘Ü•ν}ΜρΨéΉgÜ•ν}ΓΘ

Virtuoso MMSIMΧΉΦΰÉ»(n®®i)ΒΡΖ¬’φΤς™ΰ(j®¥)ΖQ“≤ΒΟΒΫΚή¥σ‘ωèä(qi®Δng)ΓΘάΐ»γΘ§Spectreκä¬ΖΖ¬’φΤςΧμΦ”ΝΥÉû(y®≠u)Μ·“ΐ«φΘ§±»²ςΫy(t®·ng)ΒΡSpiceΖ¬’φΤς–‘ΡήΗΡΏM(j®§n)3±ΕΘ§Εχ«“‘ωèä(qi®Δng)ΒΡMonte CarloΖ÷Έω“≤€p…ΌΝΥ10±ΕΒΡΖ¬’φΓΘ

Spectre XLΧμΦ”ΝΥΟφœρRFκä¬ΖΒΡ‘ωèä(qi®Δng)–Άνl”ρΕύΥΌ¬ ÷C≤®ΤΫΚβ“ΐ«φΘΜΟφœρΖ«ΨÄ–‘κä¬ΖΒΡïr(sh®Σ)”ρΓΑshootingΓ±ΥψΖ®ΘΜ”Ο”Ύ‘κ“τΚΆΕΕ³”(d®Αng)Ζ÷ΈωΒΡ–¬Νς≥ΧΘΜ“‘ΦΑΦ·≥…ΒΡΡΘîMΓΔRFΚΆICΖ¬’φΙΠΡήΓΘ

–¬Αφ±Ψ≥–÷ZΩsΕΧ”–¥σΝΩ≤νΖ÷–≈Χ•(h®Λo)ΒΡ‘O(sh®®)”΄(j®§)ι_Αl(f®Γ)ïr(sh®Σ)ιgΏ_(d®Δ)60%ΓΘ–¬ΑφAllegroΤΫ≈_(t®Δi)νA(y®¥)”΄(j®§)6‘¬Αl(f®Γ)≤ΦΓΘ

Allegro.jpg (94.5 KB)

2009-1-5 23:37

1,Α≤―bή¦Φΰ,“Μ¬Ζnext,Άξ»ΪΑ≤―b,¥_Ε®ΓΘ

2,¨ΔΓΕallegro.batΓΖΓΕ NOLIC.COMΓΖΓΕ choice ΓΖΚΆΓΕκp™τΤΤΫβΓΖΩΫΊêΒΫX:\Cadence\SPB_16.2 œ¬,Ά§ïr(sh®Σ)¨ΔNOLIC.COMΩΫΊêΒΫC:\WINDOWS\system32œ¬ΓΘ

3,¥_’J(r®®n)allegro.bat÷–¦]”–“‘œ¬¥ζ¥a:

cd %CDSROOT%\tools\Capture

nolic

nolic

cd %CDSROOT%\tools\pspice

nolic

nolic

»γΙϊ”–Θ§¨ΔΥϋ²É³h≥ΐΓΘ

4,κp™τΓΕκp™τΤΤΫβΓΖ,ΕύΏ\(y®¥n)––éΉ¥ΈΘ§÷ΝΒΫ?j®©ng)]”–εe(cu®Α)’`≥ω§F(xi®Λn)ΓΘ

5,”ΟUltraEditΜρWinHex¥ρι_\captureΡΩδ¦œ¬ΒΡcapture.exeΈΡΦΰΘ§ΏÄ”–\(zh®Αng)pspiceΡΩδ¦œ¬ΒΡimmgr.exeΓΔpspiceaa.exeΓΔpspice.exeΓΔstmed.exeΓΔpsp_eng.dllΓΔMagnetic Parts Editor.exeΓΔmodeled.exeΤΏ²Ä(g®®)ΈΡΦΰ,‘Ύ2ΏM(j®§n)÷Τœ¬≤ι’“Ή÷¥°ΓΑ00 83 C4 0C 8B 45 F8 8B E5 5D C3 55 8B EC 81 EC 84 01 00 00 57 C7 45 F8 00 00 00 00 C7 45 F4 Γ±,¨ΔΓΑ55 8B ECΓ± –όΗΡûιΓΑ33 C0 C3Γ±,±Θ¥φΈΡΦΰΘ§”¦ΉΓΘΚ”–“Μ²Ä(g®®)simsetup.dllΒΡΈΡΦΰ“ΜΕ®≤ΜΡή–όΗΡΘ§Ζώ³tΖ¬’φΒΡΙΠΡήΨΆïΰ(hu®§)≤Μ»Ϊ!!!

6,”Ο”¦ ¬±Ψ–¬Ϋ®“Μ²Ä(g®®)Ω’ΈΡΦΰ,ΟϋΟϊûιlicense.dat,Ζ≈‘ΎX:\Cadence\SPB_16.2œ¬.

7,–¬Ϋ®≠h(hu®Δn)Ψ≥ΉÉΝΩLM_LICENSE_FILE,÷ΗœρX:\Cadence\SPB_16.2\license.dat

8,ΤΤΫβΆξ≥…!

9,Α≤―bhotfix12.ΟΩ¥ΈΑ≤―bΆξhotfixΚσΕΦ“Σ‘Ό÷Ί–¬ΤΤΫβ“Μœ¬

ΉΔ“βΘΚ²Ä(g®®)³eöΔΕΨή¦Φΰàσ(b®Λo)Ηφnolic.com”–≤ΓΕΨΘ§¨Ό”Ύ’ΐ≥ΘΘ§»γnod32ΓΘ“ρ?y®Λn)ιnolic“Σ–όΗΡallegroΒΡΩ…àΧ(zh®Σ)––ΈΡΦΰΘ§Ώ\(y®¥n)––ïr(sh®Σ)ΉνΚΟïΚïr(sh®Σ)ξP(gu®Γn)ι]öΔΕΨή¦ΦΰΓΘ

]]>

±ΨΑφ±ΨΑϋά®“Μ–©–¬‘ωΙΠΡήΚΆΜΞΏBΟήΕ»ΒΡΗΡΏM(j®§n)Θ§»γ³²?c®®)α≤ΦΨÄΘ§îU(ku®Α)’ΙΒΡΗΏΟήΕ»ΜΞΏBΘ®HDIΘ©“é(gu®©)³tΓΔPCBΒΡ»ΐΨSΘ®3DΘ©ο@ Ψ≈cRFκä¬ΖΒΡΖ«¨Π(du®§)ΖQ±ήΉ¨ΓΘΆΊ’ΙΒΡΈΔΩΉ·B¨”“é(gu®©)³t‘ ‘S”Οëτ³™(chu®Λng)Ϋ®‰OûιèΆ(f®¥)κsΒΡHDI‘O(sh®®)”΄(j®§)Θ§Εχ≈c»α–‘ΑείÜάΣΈ«ΚœΒΡΕύΨÄ Ϋ«ζ–ΈΩ²ΨÄ≤ΦΨÄïΰ(hu®§)Φ”Ωλ³²?c®®)α‘O(sh®®)”΄(j®§)ΓΘ¥ΥΆβΘ§Φ·≥…ΒΡ3D PCBûg”[ΤςΉ¨‘O(sh®®)”΄(j®§)éüΩ…“‘Ω¥ΒΫ‘ΣΦΰ≈cHDIΈΔ¨ß(d®Θo)ΩΉÉ»(n®®i)≤ΩΘ§èΡΕχûιôC(j®©)–Β‘O(sh®®)”΄(j®§)àF(tu®Δn)ξ†(du®§)œϊ≥ΐΝΥ≤Μ±Ί“ΣΒΡΒϋ¥ζΓΘAllegro PCB RFΏxΦΰΏÄΆ®Ώ^ Ι”Ο“Μ²Ä(g®®)ΜρΕύ²Ä(g®®)RF‘ΣΦΰΒΡΖ«¨Π(du®§)ΖQ±ήΉ¨éΆ÷ζΙΛ≥ΧéüΦ”Ωλ³™(chu®Λng)Ϋ®ΨΪ¥_RFκä¬ΖΒΡΥΌΕ»ΓΘ

ΓΑΈ“²ÉÖΔ≈cΝΥ16.3Αφ±ΨΒΡΕύ²Ä(g®®)κAΕΈΒΡ€y(c®®)‘΅Θ§¨Π(du®§)Τδ”ΓœσΖ«≥Θ…νΩΧΘ§Γ± Kaleidescape CanadaΙΪΥΨΗΏΦâ(j®Σ)PCB‘O(sh®®)”΄(j®§)éüVincent Di Lello’fΓΘΓΑΏ@²Ä(g®®)–¬Αφ±ΨΒΡΗΡΝΦΚήΚΟΒΊΫβ¦QΝΥΈ“²ÉΒΡ–Γ–ΆΜ·‘O(sh®®)”΄(j®§)Ü•ν}Θ§Έ“²ÉΤΎ¥ΐ÷χΏ@²Ä(g®®)–¬Αφ±ΨΑl(f®Γ)≤ΦΚσΡήâρ±MΩλ¨ΔΤδëΣ(y®©ng)”Ο”ΎΈ“²ÉΒΡ‘O(sh®®)”΄(j®§)Νς≥Χ÷–ΓΘΓ±

–¬ΑφAllegro≈cOrCAD Ι”ΟΕύκAΕΈνA(y®¥)Αl(f®Γ)≤ΦΒΡΖΫ Ϋ¥_±ΘÉ»(n®®i)»ί≈cΌ|(zh®§)ΝΩΡήâρΖϊΚœΩΆëτΒΡ–η“ΣΓΘ¹μ(l®Δi)Ή‘±±ΟάΓΔöW÷όΓΔ¹Ü÷όΚΆ»’±ΨΒΡ20ΕύΦ“ΩΆëτÖΔ≈cΝΥΕύκAΕΈ€y(c®®)‘΅”΄(j®§)³ùΓΘÖΔ≈c€y(c®®)‘΅”΄(j®§)³ùΒΡΩΆëτ≈cCadenceΒΡΚœΉςΜοΑιΑϋά®NVIDIAΓΔEmersonΓΔKaleidescapeΓΔFreedom CADΓΔNordCADΓΔFlowCADΓΔGraser≈cTektronixΓΘ

16.3Αφ±Ψ÷–ΏÄΑϋΚ§¨Π(du®§)OrCADœΒΝ–°a(ch®Θn)ΤΖëΣ(y®©ng)”Ο–ß¬ ≈cΩ…”Ο–‘ΒΡ“ΜœΒΝ–¥σΖυΗΡΝΦΓΘάΐ»γOrCAD Capture CIS»γΫώΧαΙ©ΝΥΉ‘³”(d®Αng)≤ΦΨÄΙΠΡή“‘―ΗΥΌ‘ωΦ”ΏBΨÄΘ§ΏÄ”–»Ϊ–¬ΒΡ»ΐΨSΖβ―bο@ ΨΙΠΡήΓΘOrCAD PCB EditorΧαΙ©ΝΥ»ΐΨS≤ιΩ¥≈cΓΑΖ≠ΑεΓ±‘O(sh®®)”΄(j®§)/Ψéί΄“‘ΦΑÜΈΟφPCB‘O(sh®®)”΄(j®§)ΒΡΧχΨÄ÷ß≥÷ΓΘOrCAD Signal Explorer”–“Μ²Ä(g®®)Ϋ¦(j®©ng)ΗΡΝΦΒΡ”ΟëτΫγΟφΘ§”–ΆœΉßΚΆèΆ(f®¥)÷Τ’≥ΌNΙΠΡήΘ§”–«ΑΚσξP(gu®Γn)¬™(li®Δn)ΒΡ”“™τΙΠΡή≤Δ÷ß≥÷±ΨΒΊIBISΡΘ–ΆΓΘ

Ω…”Ο–‘ΗΡΏM(j®§n) «–¬ΑφAllegro PCB–≈Χ•(h®Λo)≈cκä‘¥Άξ’ϊ–‘ή¦ΦΰΒΡ”÷“Μ²Ä(g®®)÷Ίϋc(di®Θn)Θ§ΥϋΧαΙ©ΝΥ“Μ²Ä(g®®)»Ϊ–¬ΒΡ”ΟëτΫγΟφΘ§≤ΔûινA(y®¥)≤ΦΨÄΖ÷Έω≠h(hu®Δn)Ψ≥‘ωΦ”ΝΥ·B¨”Η–÷ΣΙΠΡήΓΘΆ®Ώ^¨Π(du®§)±ΨΒΊIBIS≈cSPICEΡΘ–ΆΑϋά®Cadence Virtuoso? Spectre? κä¬ΖΖ¬’φΡΘ–ΆΒΡ÷ß≥÷Θ§ I/OΨè¦_ΤςΫ®ΡΘ‰Υ(bi®Γo)€ (zh®≥n)“≤ΑϋΚ§‘ΎΤδ÷–ΓΘΝμΆβ“Μ²Ä(g®®)ΗΡΏM(j®§n)‘O(sh®®)”΄(j®§)÷ήΤΎΙήάμΒΡΒΊΖΫ «Ρήâρ”Ο¥σΝΩΦΣ±»ΧΊΦâ(j®Σ)–≈Χ•(h®Λo)ΩλΥΌ£ΏΟηPCBΘ§≤Δ«“―ΗΥΌ¥_Ε®ëΣ(y®©ng)‘™‘ΎΡΡάοΏM(j®§n)––‘îΦö(x®§)Ζ÷ΈωΘ§–≈Χ•(h®Λo)ïΰ(hu®§)Ηυ™ΰ(j®¥)Τδ–≈‘κ±»ΏM(j®§n)––≈≈Ν–ΓΘ

ΓΑΏ@²Ä(g®®)Ήν–¬ΑφAllegro”–ΚήΕύΒΡΗΡΏM(j®§n)Θ§ΡήâρΫβ¦Q³²–‘Μρ³²?c®®)α‘O(sh®®)”΄(j®§)…œΒΡ–Γ–ΆΜ·‘O(sh®®)”΄(j®§)Ü•ν}Θ§Γ±Freedom CAD Ήœ·Ώ\(y®¥n)†I(y®Σng)ΙΌScott Miller’fΓΘΓΑΉςûι“ΜΦ“‘O(sh®®)”΄(j®§)Ζΰ³’(w®¥)ΙΪΥΨΘ§Έ“²É“Μ÷±Κή”–≈d»ΛΧαΗΏΈ“²É?c®®)O(sh®®)”΄(j®§)éüΒΡ–ß¬ ΚΆ‘O(sh®®)”΄(j®§)÷ήΤΎΒΡΩ…νA(y®¥)€y(c®®)–‘ΓΘΈ“²É¨Δïΰ(hu®§)όD(zhu®Θn)“ΤΒΫ16.3Αφ±ΨΘ§“≤ΆΤΥ]Έ“²ÉΒΡΩΆëτ±MΩλόD(zhu®Θn)“ΤΓΘΓ±

‘™Αφ±ΨΫβ¦QΒΡΝμΆβ“Μ–©÷Ί“ΣÜ•ν} «≈c≤ΩΦΰîΒ(sh®¥)™ΰ(j®¥)Ιήάμ”–ξP(gu®Γn)ΓΘΦ·≥…ΒΡECADΓΔMCAD≤ΩΦΰ³™(chu®Λng)Ϋ®Θ§…ζ≥…≈cΑl(f®Γ)≤ΦΩ…“‘ΫΒΒΆ≤Μ±Ί“ΣΒΡ‘≠–ΆôC(j®©)≥ω‰”¥ΈîΒ(sh®¥)ΓΘΏ@²Ä(g®®)–¬≤ΩΦΰ¨ß(d®Θo)»κΙΠΡήΩ…“‘îU(ku®Α)’ΙνA(y®¥)Αl(f®Γ)≤Φ≈c≈Rïr(sh®Σ)≤ΩΦΰΒΡΙήάμ≈cΆ®÷ΣΘ§ΩsΕΧ‘O(sh®®)”΄(j®§)÷ήΤΎΓΘ¥ΥΆβΘ§ΙΛ≥ΧéüΩ…“‘Ά®Ώ^ Ι”Ο≈ζ€ (zh®≥n)ΒΡ≈cΆΤΥ]ΒΡ≤ΩΦΰΧφ™Q‘≠¹μ(l®Δi)ΒΡ≤ΩΦΰ¹μ(l®Δi)¨ç(sh®Σ)§F(xi®Λn)Ή‘³”(d®Αng)≤ΩΦΰΗϋ–¬Θ§“≤Ω…“‘Ά®Ώ^èU½â≤ΩΦΰΗζέô“‘¥_±Θ°a(ch®Θn)ΤΖΒΡΌ|(zh®§)ΝΩΓΘ

Allegro≈cOrCAD PCB Design 16.3Αφ¨Δ”Ύ2009Ρξ12‘¬≥θι_ ΦœρΩΆëτΧαΙ©œ¬ίdΓΘ

]]>ΕΦΟφ≈R÷χ»γΚΈ¨Δ ÷ν^ΒΡProtel‘O(sh®®)”΄(j®§)“Τ÷≤ΒΫCadence PCB‘O(sh®®)”΄(j®§)ή¦Φΰ÷–ΒΡÜ•ν}ΓΘ

ΓΓΓΓ‘ΎΏ@²Ä(g®®)Ώ^≥Χ°î(d®Γng)÷–≈ωΒΫΒΡÜ•ν}¥σ÷¬Ω…Ζ÷ûιÉ…ΖNΘΚ“Μ «‘O(sh®®)”΄(j®§)≤ΜΚήèΆ(f®¥)κsΘ§‘O(sh®®)”΄(j®§)éü÷ΜœκΫη÷ζCadence CCTΒΡèä(qi®Δng)¥σΉ‘³”(d®Αng)≤ΦΨÄΙΠΡήΆξ≥…≤ΦΨÄΙΛΉςΘΜΕΰ «‘O(sh®®)”΄(j®§)èΆ(f®¥)κsΘ§‘O(sh®®)”΄(j®§)éü–η“ΣΫη÷ζ–≈‘κΖ÷ΈωΙΛΨΏ¹μ(l®Δi)¨Π(du®§)‘O(sh®®)”΄(j®§)ΏM(j®§n)–––≈‘κΖ¬’φΘ§

‘O(sh®®)÷ΟΨÄΨW(w®Θng)ΒΡ≤ΦΨÄΆΊ?f®¥)δΫY(ji®Π)‰΄(g®Αu)Β»ΙΛΉςΓΘ

ΓΓΓΓ¨Π(du®§)”ΎΒΎ“ΜΖN«ι¦rΘ§“ΣΉωΒΡόD(zhu®Θn)Μ·ΙΛΉς±»ί^ΚÜ(ji®Θn)ÜΈΘ§Ω…“‘ Ι”ΟProtelΜρCadenceΧαΙ©ΒΡProtelΒΫCCTΒΡόD(zhu®Θn)™QΙΛΨΏ¹μ(l®Δi)Άξ≥…Ώ@“ΜΙΛΉςΓΘ¨Π(du®§)”ΎΒΎΕΰΖN«ι¦rΘ§“ΣΉωΒΡΙΛΉςœύ¨Π(du®§)èΆ(f®¥)κs“Μ–©Θ§œ¬Οφ¨ΔΏ@ΖNόD(zhu®Θn)Μ·ΒΡΖΫΖ®Ής“ΜΚÜ(ji®Θn)ÜΈΒΡΫιΫBΓΘ

ΓΓΓΓCadence–≈‘κΖ÷ΈωΙΛΨΏΒΡΖ÷Έω¨Π(du®§)œσ «Cadence AllegroΒΡbrdΈΡΦΰΘ§ΕχAllegroΩ…“‘Ήx»κΚœΚθΤδ“Σ«σΒΡΒΎ»ΐΖΫΨW(w®Θng)±μΘ§Protelίî≥ωΒΡTelexisΗώ ΫΒΡΨW(w®Θng)±μùMΉψAllegro¨Π(du®§)ΒΎ»ΐΖΫΨW(w®Θng)±μΒΡ“Σ«σΘ§Ώ@‰”ΨΆΩ…“‘¨ΔProtelΈΡΦΰΉΔ»κAllegroΓΘ

ΓΓΓΓΏ@άο”–É…ϋc(di®Θn)’à(q®Ϊng)Ήx’ΏΉΔ“βΓΘ Ήœ»Θ§AllegroΒΎ»ΐΖΫΨW(w®Θng)±μ‘Ύ$PACKAGEΕΈ≤Μ‘ ‘S”–ΓΑ.Γ±ΘΜΤδ¥ΈΘ§‘ΎProtel÷–Θ§Έ“²É”ΟBasName[0:N]ΒΡ–Έ Ϋ±μ ΨΩ²ΨÄΘ§”ΟBasName[x]±μ ΨΩ²ΨÄ÷–ΒΡ“ΜΗυ–≈Χ•(h®Λo)Θ§AllegroΒΎ»ΐΖΫΨW(w®Θng)±μ÷–Ω²ΨÄ÷–ΒΡ“ΜΗυ–≈Χ•(h®Λo)ΒΡ±μ Ψ–Έ ΫûιBas NameXΘ§Ήx’ΏΩ…“‘Ά®Ώ^÷±Ϋ”–όΗΡProtelίî≥ωΒΡTelesisΨW(w®Θng)±μΒΡΖΫΖ®Ϋβ¦QΏ@–©Ü•ν}ΓΘ

ΓΓΓΓAllegro‘ΎΉΔ»κΒΎ»ΐΖΫΨW(w®Θng)±μïr(sh®Σ)ΏÄ–η“ΣΟΩΖNνê–ΆΤςΦΰΒΡ‘O(sh®®)²δΟη ωΈΡΦΰDevice.txtΈΡΦΰΘ§ΥϋΒΡΗώ Ϋ»γœ¬ΘΚ

Package: package type

Class: classtype

Pincount: total pinnumber

Pinused: ...

ΓΓΓΓΤδ÷–≥Θ”ΟΒΡ «PACKAGEΘ§CLASSΘ§PINCOUNTΏ@éΉμ½(xi®Λng)ΓΘPACKAGEΟη ωΝΥΤςΦΰΒΡΖβ―bΘ§ΒΪAllegro‘ΎΉΔ»κΨW(w®Θng)±μïr(sh®Σ)ïΰ(hu®§)”ΟΨW(w®Θng)±μ÷–ΒΡPACKAGEμ½(xi®Λng)ΕχΚω¬‘‘O(sh®®)²δΟη ωΈΡΦΰ÷–ΒΡΏ@“Μμ½(xi®Λng)ΓΘCLASS¥_Ε®ΤςΦΰΒΡνê–ΆΘ§“‘±ψ–≈‘κΖ÷’έΘ§Cadence¨ΔΤςΦΰΖ÷ûιIC,IOΘ§DISCRETE»ΐνêΓΘPINCOUNT’fΟςΤςΦΰΒΡΙήΡ_îΒ(sh®¥)ΡΩΓΘ¨Π(du®§)”Ύ¥σΕύîΒ(sh®¥)ΤςΦΰΘ§Device.txtΈΡΦΰ÷–ΑϋΚ§”–Ώ@»ΐμ½(xi®Λng)ΨΆΉψâρΝΥΓΘ

ΓΓΓΓ”–ΝΥΒΎ»ΐΖΫΨW(w®Θng)±μΚΆ‘O(sh®®)²δΟη ωΈΡΦΰΘ§Έ“²ÉΨΆΩ…“‘¨ΔProtel÷–‘≠άμàD‘O(sh®®)”΄(j®§)“‘ΨW(w®Θng)±μΒΡ–Έ Ϋ¥ζ»κΒΫCadence PCB‘O(sh®®)”΄(j®§)ή¦Φΰ÷–Θ§Ϋ”œ¬¹μ(l®Δi)Θ§‘O(sh®®)”΄(j®§)éüΨΆΩ…“‘Ϋη÷ζCadence PCBή¦Φΰ‘ΎΗΏΥΌΗΏΟήΕ»PCB‘O(sh®®)”΄(j®§)ΖΫΟφΒΡèä(qi®Δng)¥σΙΠΡήΆξ≥…Ή‘ΦΚΒΡ‘O(sh®®)”΄(j®§)ΓΘ

]]>

”…TarayΙΪΥΨι_Αl(f®Γ)Θ§CadencerΒΡΩΆëτΩ…Ά®Ώ^‘≠ Φ‘O(sh®®)²δΙ©ëΣ(y®©ng)…ΧΘ®OEMΘ©Öf(xi®Π)ΉhΪ@ΒΟΘ§Ώ@“ΜΣö(d®≤)“Μüo(w®≤)ΕΰΒΡ¬™(li®Δn)ΚœΫβ¦QΖΫΑΗΧαΙ©ΝΥÉû(y®≠u)Μ·ΒΡcorrect-by-constructionFPGA“ΐΡ_Ζ÷≈δΘ§ΥϋΩ… ΙPCB≤ΦΨÄΏ^≥Χ÷–€p…Ό“ΐΡ_Éû(y®≠u)Μ·Βϋ¥ζ¥ΈîΒ(sh®¥)Θ§Ά§ïr(sh®Σ)€p…Ό¨ΔFPGA’ϊΚœPCB‘O(sh®®)”΄(j®§)Υυ–ηΒΡ¨”îΒ(sh®¥)ΓΘAllegro FPGA System PlannerΆ®Ώ^FPGA“ΐΡ_Ή‘³”(d®Αng)Ζ÷≈δΘ§ΏÄΩsΕΧΝΥΙΪΥΨëΣ(y®©ng)”ΟFPGA‘ΎPCBœΒΫy(t®·ng)…œΡΘîMASICΒΡïr(sh®Σ)ιgΓΘ

ΓΑΈ“΅L‘΅ΝΥΤδΥϋ≥–÷ZΚÜ(ji®Θn)Μ·FPGA I/OèΆ(f®¥)κs–‘Ü•ν}ΒΡΙΛΨΏΘ§ΒΪ¦]”–“Μ²Ä(g®®)”–œσTarayΙΪΥΨΏ@‰”ΒΡΫβ¦QΖΫΖ®Θ§Γ±HarrisΙΪΥΨGCSD–≈Χ•(h®Λo)Άξ’ϊTMTΊ™(f®¥)Ίü(z®Π)»ΥRoberto Cordero’fΒάΘ§ΓΑTarayΙΪΥΨΒΡFPGA I/OΨCΚœΦΦ–g(sh®¥) «Έ©“Μ“Μ²Ä(g®®)ΡήΉ¨Έ“²É?c®®)ΎœΒΫy(t®·ng)Φâ(j®Σ)ίî»κΈ“²ÉΒΡ‘O(sh®®)”΄(j®§)“βàDΒΡΘ§ΥϋΆξ»ΪΉ‘³”(d®Αng)¨Δ“ΐΡ_Ζ÷≈δ“Μ¥Έ’ϊΚœΒΫΕύ²Ä(g®®)FPGA÷–ΓΘTarayΙΪΥΨΒΡΦΦ–g(sh®¥)¨Δ≥…ûιCadenceΙΪΥΨ°a(ch®Θn)ΤΖ“Μ²Ä(g®®)èä(qi®Δng)”–ΝΠΒΡΫMΚœΓΘΓ±

¨Π(du®§)”Ύ»’“φ‘ωιL(zh®Θng)ΒΡîΒ(sh®¥)™ΰ(j®¥)ΆΧΆ¬ΝΩ“‘ΦΑ‘Ϋ¹μ(l®Δi)‘ΫΕύΒΡΙΠΡήΘ§Τδ°a(ch®Θn)ΤΖ¨ß(d®Θo)÷¬¥σΝΩ“ΐΡ_îΒ(sh®¥)ΒΡFPGAΨΏ”–ΨΏ”–ΗΏΥΌIOΒΡ–η«σΓΘΏ@–©FPGAsΏÄΨΏ”–ΗϋΗΏΦâ(j®Σ)ΒΡ¥φÉΠ(ch®≥)ΤςΫ”ΩΎΓΔΗϋΒΆΒΡΙΠΚΡΘ§èΡΕχΫβ¦QΩΆëτ¨Π(du®§)ι_Αl(f®Γ)ΗϋΦ”ΓΑΨG…ΪΓ±ΒΡ°a(ch®Θn)ΤΖ–η“ΣΓΘ Ι”ΟΏ@ΖNΗϋ¥σ»ίΝΩΓΔΗϋΕύΙΠΡήΚΆœ»ΏM(j®§n)ΗΏΥΌΫ”ΩΎΒΡFPGAΘ§‘ΎPCBœΒΫy(t®·ng)÷–ΓΔ“‘ΦΑ‘ΎPCB…œ Ι”ΟFPGAΏM(j®§n)––ASIC.ΡΘîMΒΡîΒ(sh®¥)ΡΩ’ΐ‘Ύ‘ωΦ”ΓΘ CadenceΙΪΥΨOrCADΚΆAllegro FPGA System PlannerΟφœρΡ«–©¨ΔFPGA”Ο”ΎPCBœΒΫy(t®·ng)ΕχΟφ≈RΧτëπ(zh®Λn)ΒΡœΒΫy(t®·ng)ΙΪΥΨΚΆICΙΪΥΨΓΘ

ΓΑ§F(xi®Λn)≥…ΒΡΕύFPGA‘≠–ΆΑε≤Δ≤ΜΩ² «ΡήùMΉψ‘O(sh®®)”΄(j®§)éüΒΡ“Σ«σΘ§Γ±XilinxΙΪΥΨΙη”≤Φΰ≈cëΣ(y®©ng)”ΟΌY…νΩ²±O(ji®Γn)Ed McGettigan’fΒάΘ§ΓΑ Ι”ΟΏ@ΖNFPGA I/OΨCΚœΦΦ–g(sh®¥)Θ§‘O(sh®®)”΄(j®§)’ΏΩ…³™(chu®Λng)‘λ≥ω“Μ²Ä(g®®)–¬ΒΡ‘≠–ΆœΒΫy(t®·ng)Θ§Ά§ïr(sh®Σ)±» Ι”Ο‰Υ(bi®Γo)€ (zh®≥n)ΒΡ“ΐΡ_Éû(y®≠u)Μ· ÷ΙΛΖΫ ΫΩλΒΟΕύΒΡïr(sh®Σ)ιg’“≥ωΕύΖNΜΞ¬™(li®Δn)≈cΫMΦΰΒΡ‘O(sh®®)”΄(j®§)ΖΫΖ®ΓΘΓ±

‘™ΦΦ–g(sh®¥)‘Ύ“ΜœΒΝ–Ω…îU(ku®Α)’ΙΫβ¦QΖΫΑΗ÷–ΨυΩ…Ϊ@ΒΟΘ§èΡOrCAD FPGA System PlannerΒΫAllegro FPGA System Planner L, XL “‘ΦΑGXLΘ§≤Δ≈cOrCAD Capture, OrCAD PCB DesignerΘ§Allegro Design Entry HDL ΚΆ Allegro PCB Design°a(ch®Θn)ΤΖΨoΟή’ϊΚœΓΘFPGA System PlannerΩs€pΝΥ¨ΔFPGA’ϊΚœΒΫPCBΒΡïr(sh®Σ)ιgΘ§Ά®Ώ^FPGAΌY‘¥ΒΡΉνΦ―Μ· Ι”ΟΘ§‘ωèä(qi®Δng)ΝΥFPGAΒΡ–‘ΡήΘ§≤ΔΆ®Ώ^€p…ΌΟήΦ·≤ΦΨ÷ΓΔèΆ(f®¥)κsΚΆ¥σΝΩ“ΐΡ_îΒ(sh®¥)ΒΡ FPGAΥυ–ηΒΡPCB¨”îΒ(sh®¥)èΡΕχΫΒΒΆΝΥPCBΒΡ…ζ°a(ch®Θn)≥…±ΨΓΘ

ΓΑCadence ΙΪΥΨΒΡFPGA System Planner“Μ²Ä(g®®)³™(chu®Λng)–¬ΒΡΫβ¦QΖΫΑΗΘ§ΟφœρΡ«–©Οφ≈R¨Δ§F(xi®Λn)Ϋώ¥σΝΩ“ΐΡ_îΒ(sh®¥)ΡΩΓΔèΆ(f®¥)κsΒΡFPGA’ϊΚœΒΫPCB‘O(sh®®)”΄(j®§)Νς≥ΧΧτëπ(zh®Λn)ΒΡ‘O(sh®®)”΄(j®§)àF(tu®Δn)ξ†(du®§)Γ±CadenceΙΪΥΨΗ±Ω²‘‘Charlie Giorgetti,’fΒάΘ§ΓΑΏ@’ΐ «Έ“²ÉΒΡΩΆëτΤΎ¥ΐèΡΈ“²ÉΏ@άοΪ@ΒΟΒΡΡήâρΩsΕΧPCB…œ”–¥σΝΩ“ΐΡ_îΒ(sh®¥)ΡΩΒΡFPGAΒΡ‘O(sh®®)”΄(j®§)÷ήΤΎ≤ΔΫΒΒΆΙήάμοL(f®Ξng)κU(xi®Θn)ΒΡΡ«ΖNΦΦ–g(sh®¥)ΓΔΉ‘³”(d®Αng)Μ·ΚΆ³™(chu®Λng)–¬ΓΘ