- ╩’║ŻĮ╠ė²╝»łFšōē» (http://www.hufushizhe.com/bbs/index.asp)

-- FPGA╝╝ągėæšōģ^ (http://www.hufushizhe.com/bbs/list.asp?boardid=2)

---- [▐D╠¹]FPGA (http://www.hufushizhe.com/bbs/dispbbs.asp?boardid=2&id=1286)

-- ░l▓╝ĢrķgŻ║2010-11-12 15:28:24

-- [▐D╠¹]FPGA

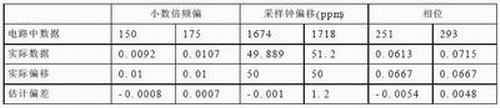

▒Ē4.1 ▓©ą╬łDųąöĄō■┼cīŹļHöĄō■ī”šš▒Ē

ąĪöĄ▒ČŅl┬╩Ų½ęŲ║═▓╔śėńŖŅl┬╩Ų½ęŲ─ŻēK╩Ūį┌š¹Ų½ąŻ═Ļų«║¾▓┼ėąą¦Ż¼┤╦ĢrĄ─ąĪöĄ▒ČŅl┬╩Ų½ęŲ╩ŪĮø▀^Ģrė“┤ųŲ½╣└ėŗąŻš²║¾Ą─╩ŻėÓ▓┐ĘųĪŻ▒Ē4.1┴ą│÷▓©ą╬ųąĄ─╣└ųĄ┼cīŹļHöĄō■Ą─ī”æ¬ĻPŽĄĪŻÅ─▒ĒųąĄ─öĄūųī”æ¬ĻPŽĄ┐╔ęį┐┤│÷Ż¼ļŖ┬Ęųą╣└ėŗĄ─ąĪöĄ▒ČŅlŲ½┼cīŹļHŅlŲ½Ą─▓Ņį┌0.1%ęįā╚ĪŻ▓╔śėńŖŲ½ęŲ╣└ėŗųĄ┼cīŹļHŲ½ęŲš`▓Ņ×ķ1ppmū¾ėęŻ¼▀@ęčØMūŃ┴╦▓╔śėńŖĄ─┤ųš{Š½Č╚Ż╗ŽÓ╬╗▌ö│÷×ķŪ░║¾Ę¹╠¢Ą─ąĪöĄ▒ČŲ½Ņl╦∙ę²ŲĄ─ŽÓ╬╗ą²▐DĪŻė╔┤╦å╬į¬ļŖ┬ĘŻ¼┐╔ęį£╩┤_Ąž╣└ėŗ│÷ąĪöĄ▒ČŅlŲ½║═▓╔śėńŖŲ½ęŲ╝░ŲõŽÓ╬╗ĪŻ

╝ÜČ©Ģr═¼▓Į╣└ėŗĄ─ļŖ┬ĘĘ┬šµ

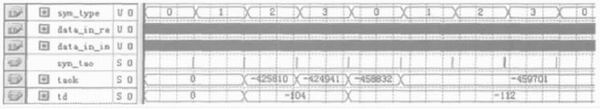

ĪĪĪĪłDųąĄ─data_re_in[15..0]║═data_im_in[15..0]▒Ē╩ŠĮø╣½╣▓ŽÓ╬╗ąŻš²║¾Ą─Å═öĄō■īŹ╠ō▓┐Ż╗syn_in╩Ū▌ö╚ļėąė├öĄō■Ą─Ų╩╝╬╗ų├├}ø_Ż╗sym_type[1..0]╩ŪŪ░Č╦▌ö╚ļĄ─Ę¹╠¢ŅÉą═Ż╗taok[22..0]║═td[9..0]Ęųäe×ķ╣└ėŗĄ─Ę¹╠¢Č©ĢrŲ½ęŲ║═Ųõš¹öĄ▓┐ĘųŻ╗syn_tao╩Ūtaok[22..0]Ą─ėąą¦öĄō■Ų╩╝├}ø_ą┼╠¢ĪŻ

łD4.3 Ę¹╠¢Č©ĢrŲ½ęŲ╣└ėŗå╬į¬Ą─ļŖ┬Ę▓©ą╬łD

łD4.3ųą╣▓ėą9éĆĘ¹╠¢ĪŻė╔ė┌▒Š╦ŃĘ©└¹ė├┴╦4éĆĘ¹╠¢Ą─╔ó▓╝ī¦ŅlŻ¼╣╩łD4.3ųąŻ¼Å─Ą┌╦─éĆĘ¹╠¢Ą─ĮY╩°╠Äķ_╩╝Ż¼į┌syn_tao║¾Ą─taok[22..0]▓┼╩Ū«öŪ░Ę¹╠¢Ą─Č©ĢrŲ½ęŲ╣└ėŗųĄĪŻ▓©ą╬ųąĄ─╣└ųĄ┼cīŹļHöĄō■Ą─ī”æ¬ĻPŽĄ╚ń▒Ē4.2╦∙╩ŠĪŻ

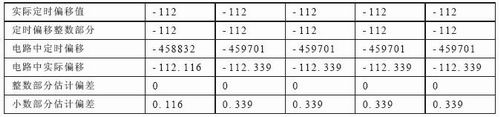

▒Ē4.2 ▓©ą╬łDųąöĄō■┼cīŹļHöĄō■ī”šš▒Ē

ĪĪĪĪ▒Ē4.2ųąĄ─Č©ĢrīŹļHŲ½ęŲ×ķ-112Ż¼Č°▓╗╩ŪĘ┬šµŚl╝■ųąĄ─-100Ż¼▀@╩Ūė╔ė┌į┌╚└¹ą┼Ą└Ą─Ę┬šµ─Żą═ųąŻ¼Ę¹╠¢Č©Ģr═¼▓ĮŅ^╬╗ų├(ųžą─╬╗ų├)╩Ūį┌Ą┌ę╗ŚlÅĮų«║¾12éĆ▓╔śė³c│÷¼FĄ─ĪŻė╔▒ĒųąöĄō■ī”æ¬ĻPŽĄ┐╔ų¬Ż¼Ę¹╠¢Č©ĢrŲ½ęŲ╣└ėŗå╬į¬┐╔£╩┤_Ąž╣└│÷Ę¹╠¢Č©ĢrŲ½ęŲĄ─š¹öĄ▓┐ĘųĪŻė╔ė┌▓╔śėńŖŲ½ęŲĪó╦ŃĘ©╣└ėŗš`▓Ņ╝░ļŖ┬Ę▀\╦Ńš`▓ŅĄ─ė░ĒæŻ¼ŲõąĪöĄ▓┐Ęų▓╗×ķ┴ŃŻ¼▀@┼cļŖ┬ĘĄ─Ę┬šµĮY╣¹ę╗ų┬ĪŻ

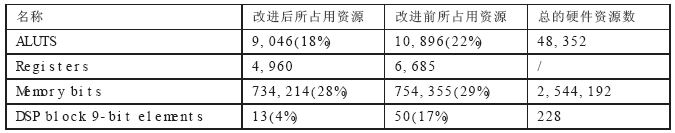

Ė─▀MŪ░║¾š╝ė├ė▓╝■┘Yį┤▒╚▌^

ĪĪĪĪ▒Ē4.3Įo│÷┴╦Ė─▀MŪ░║¾Ż¼Ņlė“═¼▓Į╦∙š╝ė├Ą─ė▓╝■┘Yį┤▒╚▌^Ż¼ŲõųąALUTSĪóRegistersĪóMemorybitsĪóDSPblock9-bitelementsĘųäe×ķūį▀mæ¬▓ķšę▒ĒĪó╝─┤µŲ„Īó┤µā”Ų„║═9ūų╣ØDSP╠Ä└ĒēKĪŻ═©▀^▒╚▌^┐╔ęį░l¼FŻ¼Ė─▀M║¾Ą─ĘĮ░Ė┐╔ęį╣Ø╩Ī┤¾┴┐Ą─ė▓╝■┘Yį┤ĪŻ

▒Ē4.3 Ė─▀MŪ░║¾Ą─ė▓╝■┘Yį┤ī”▒╚

ĮY╩°šZ

ĪĪĪĪŅl┬╩Ų½ęŲ╣└ėŗ┐╔ęįĘų×ķš¹öĄ▒ČŅlŲ½╣└ėŗå╬į¬ĪóąĪöĄ▒ČŅlŲ½Īó▓╔śėńŖŲ½ęŲ╣└ėŗå╬į¬║═Ę¹╠¢Č©ĢrŲ½ęŲ╣└ėŗå╬į¬ĪŻ▒Š╬─ų„ę¬ĮķĮBĖ„▓┐ĘųĄ─╦ŃĘ©ĘĮ░Ė╝░ļŖ┬ĘīŹ¼FĢr╦∙ė├Ą─FPGAį¬╝■Ą─╗∙▒ŠĮYśŗĪóįOėŗ╦╝┬ĘĪŻūŅ║¾═©▀^ī”ļŖ┬ĘĄ─Ę┬šµ▓©ą╬┐╔ęį┐┤│÷Ż¼▀@ą®Ņlė“═¼▓Į╦ŃĘ©║═FPGAļŖ┬Ę─▄ē“ØMūŃČÓ▌d▓©é„▌öŽĄĮyĄ─═¼▓Įę¬Ū¾ĪŻ