0 ę² čį

ĪĪĪĪ«öŪ░Ųš▒ķ╩╣ė├Ą─DSPšZę¶╠Ä└Ē╝╝ągų╗─▄ī”šZę¶▀Mąą║åå╬╠Ä└ĒŻ¼▓╗─▄▀m欚Z궜I䚥─ČÓśė╗»┌ģä▌ĪŻ▒Š╬─ĮķĮB└¹ė├MPC860║═VxWorksīŹ¼FŠC║ŽšZę¶═©ą┼ŲĮ┼_Ż¼ų¦│ųČÓ░Õ┐©ĪóČÓ┬ĘšZę¶īŹĢré„▌öŻ¼┐╔öUš╣ČÓ┬ĘšZę¶╣▓┬Ā╣”─▄ĪŻ└¹ė├MPC860Ą─═©ą┼║═ą┼╠¢╠Ä└Ē╣”─▄Ż¼ŪęVx-WorksŠ▀ėąš╝ė├┐šķgąĪĪół╠ąąą¦┬╩Ė▀ĪóĘĮ▒Ń▀MąąéĆąį╗»Č©ųŲ║═▌^║├Ą─╝µ╚▌ąįĄ╚╠ž³cŻ¼╦∙ęįįōŠC║ŽšZę¶═©ą┼ŲĮ┼_į┌╣”─▄Īóė▓╝■ĮYśŗĪó¾wĘeĪó╣”║─ęį╝░ņ`╗Ņąį╔ŽŠ▀ėą▌^┤¾ā×ä▌ĪŻ

ĪĪĪĪį┌įOėŗųą▒M┴┐▓╔ė├ŪČ╚ļ╩Įķ_░lųąĄ─│Żė├Ų„╝■Ż¼ęį▒Ń╔į╝ėĖ─äė╝┤┐╔æ¬ė├ė┌Ųõ╦¹įOėŗĪŻ┐╔ęįĖ∙ō■īŹļHąĶę¬Ė³Ė─ŽĄĮyųąšZę¶═©Ą└Ą─öĄ─┐║═öUš╣ČÓ┬ĘšZę¶╣▓┬Ā╣”─▄Ą╚ĪŻ

ĪĪĪĪ1 ŽĄĮyĮYśŗ╝░╣żū„įŁ└Ē

ĪĪĪĪ1Ż«1 ŽĄĮyĮM│╔╝░╠ž³c

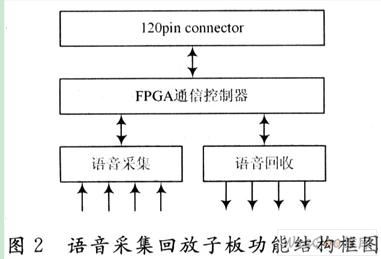

ĪĪĪĪš¹éĆ═©ą┼ŲĮ┼_ė╔šZę¶═©ą┼╠Ä└Ēų„░Õ║═šZę¶▓╔╝»╗žĘ┼ūė░ÕĮM│╔ĪŻšZę¶═©ą┼╠Ä└Ēų„░Õ░³└©CPU MPC860ĪóFLASH┤µā”Ų„ĪóSDRAM┤µā”Ų„Īó10Ż»100MbŻ»sŠWĮjĮė┐┌ĪóRS 232┤«┐┌ĪóBDMš{įćĮė┐┌ĪóConsoleĮė┐┌Īó╣®ļŖ║═Å═╬╗ļŖ┬Ę╝░120pin▀BĮėŲ„ĪŻ═©ą┼╠Ä└Ēų„░ÕĄ─║╦ą─MPC860╩ŪMotorola╣½╦ŠĄ─ę╗┐Ņė╔MC68360č▌ūāČ°üĒĄ─═©ė├å╬Ų¼╝»│╔ŪČ╚ļ╩Į╬ó╠Ä└ĒŲ„Ż¼▀mė├ė┌═©ą┼║═ŠWĮjŽĄĮyĪŻįō╬ó╠Ä└ĒŲ„ā╚▓┐ėąā╔éĆ╠Ä└ĒŲ„Ż║PowerPC║═32╬╗RISC╠Ä└ĒŲ„ĪŻPowerPC║╦═¼ā╚┤µ╣▄└Ēå╬į¬(MMU)ĪóųĖ┴Ņ║═öĄō■Cacheę╗═¼╠Ä└ĒĖ▀īė┤╬æ¬ė├Ż¼CPMätžōž¤═Ļ│╔Ą═īėöĄō■═©ą┼ĪŻā╔éĆ╠Ä└ĒŲ„ų„ę¬═©▀^╣▓ŽĒā╚┤µĮ╗╗źĪŻ═©ą┼╠Ä└Ē─ŻēK└¹ė├SCCŻ¼SMCŻ¼SPI║═I2C┤«ąą═©Ą└┼c═Ō▓┐įOéõ═©ą┼Ż¼ŲõųąSCC║═SMCų¦│ųĢrĘųÅ═ė├ĪŻįOėŗųąŻ¼SCC╣żū„į┌QMCģfūhTrans-parent ModeĪŻ═©ą┼╠Ä└Ē─ŻēK(CPM)ą┬į÷┴╦öĄūųą┼╠¢╠Ä└Ē(DSP)╣”─▄ĪŻšZę¶▓╔╝»╗žĘ┼ūė░Õė╔šZę¶▓╔╝»ļŖ┬ĘĪóšZę¶╗žĘ┼ļŖ┬ĘĪó╗∙ė┌FPGAīŹ¼FĄ─═©ą┼┐žųŲŲ„║═┼cšZę¶═©ą┼╠Ä└Ēų„░Õ▀BĮėĄ─120pin▀BĮėŲ„ĮM│╔ĪŻ

ĪĪĪĪė╔ė┌MPC860Ą─öĄō■é„▌ö╦┘Č╚ŽÓ▒╚ADC║═DACę¬┐ņ║▄ČÓŻ¼įOėŗŽÓæ¬Ą─▀ē▌ŗļŖ┬Ę┐žųŲšZ궥─▓╔╝»║═╗žĘ┼Īóģfš{MPC860║═öĄō■▓╔╝»Īó╗žĘ┼ļŖ┬Ęų«ķgĄ─═©ą┼╩Ū▒ŻūCŽĄĮyš²│Ż╣żū„Ą─ĻPµIĪŻ╬─ųąįOėŗ┴╦╗∙ė┌Altera╣½╦ŠĄ─Cycloneó“EP2C8ąŠŲ¼īŹ¼FĄ─═©ą┼┐žųŲŲ„üĒĮŌøQ▀@ę╗å¢Ņ}ĪŻ

ĪĪĪĪīó═©ą┼ŲĮ┼_Ęų×ķšZę¶═©ą┼╠Ä└Ēų„░Õ║═šZę¶▓╔╝»╗žĘ┼ūė░ÕĘųäeįOėŗīŹ¼FŻ¼╩Ū×ķ┴╦ĮĄĄ═ŽĄĮyķ_░lļyČ╚║═▒Ńė┌ŽĄĮyŠSūoĪó╔²╝ē║═öUš╣ĪŻ└²╚ńšZę¶═©ą┼╠Ä└Ēų„░Õ¤oąĶĖ─äė╝┤┐╔└¹ė├ęčėąĄ─▀BĮėŲ„ĪóFECŠWĮjĮė┐┌║═SDRAM┤µā”Ų„Ą╚┘Yį┤┼cęĢŅlŠÄĮŌ┤aąŠŲ¼ĪóęĢŅlē║┐sŻ»ĮŌē║┐sąŠŲ¼ĮM│╔ŠWĮjęĢŅlĘ■äšŲ„ĪŻ

ĪĪĪĪ1Ż«2 ╣”─▄ĮYśŗ║═╣żū„įŁ└Ē

ĪĪĪĪšZę¶═©ą┼╠Ä└Ēų„░ÕĄ─╣”─▄ĮYśŗ╚ńłD1╦∙╩ŠĪŻ

ĪĪĪĪŽĄĮy╔ŽļŖ║¾Ż¼šZę¶═©ą┼╠Ä└Ēų„░ÕÅ═╬╗ļŖ┬Ę«a╔·Å═╬╗ą┼╠¢Ż¼MPC860Įė╩šĄĮÅ═╬╗ą┼╠¢║¾Ż¼╠°▐DĄĮ0X100╠Äķ_╩╝ł╠ąąåóäė┤·┤aĪŻ░┤ššBSP┼õų├ų▓Įł╠ąąCPU│§╩╝╗»Īó░Õ╔ŽŲõ╦¹ė▓╝■ļŖ┬ĘĄ─│§╩╝╗»Īó▓┘ū„ŽĄĮy▀\ąą╦∙ąĶöĄō■ĮYśŗĄ─│§╩╝╗»ĪóåóäėVxWorks WINDā╚║╦ĪóäōĮ©UserRoot╚╬äšĪó│§╩╝╗»ŽĄĮyųąė├ĄĮĄ─┐╔▀xöUš╣─ŻēK(╚ńIŻ»OŽĄĮyĪó╬─╝■ŽĄĮyĪóŠWĮjģfūhĄ╚)ĪóäōĮ©╚╬äšusrAppInit()Ż¼┤╦ĢršZę¶═©ą┼ŲĮ┼_£╩éõŠ═ŠwŻ¼┐╔ęįł╠ąąšZę¶═©ą┼╚╬äšĪŻ▓╔╝»░ÕĄ─╣”─▄ĮYśŗ╚ńłD2╦∙╩ŠŻ¼šZę¶═©ą┼╠Ä└Ēų„░Õåóäė═Ļ«ģ║¾Ż¼šZę¶▓╔╝»╗žĘ┼ūė░Õ┐╔į┌═©ą┼┐žųŲŲ„┐žųŲŽ┬▓╔╝»║═╗žĘ┼šZ궯¼▓óī”šZę¶öĄō■▀Mąąē║┐sŠÄĮŌ┤a║═IPĘŌčbĪóĮŌĘŌčb╠Ä└ĒĪŻ

ĪĪĪĪ1Ż«3 öĄō■╠Ä└Ē┴„│╠

ĪĪĪĪMPC860T║═ADC AD7825Ż¼DAC AD7305ų«ķgĄ─═©ą┼ė╔═©ą┼┐žųŲŲ„┐žųŲĪŻ═©ą┼┐žųŲŲ„ė╔öĄō■ŠÅø_ģ^(Rx FIFOŻ¼Tx FIFO)Ż¼╗∙ė┌FSM(ėąŽ▐ĀŅæBÖC)īŹ¼FĄ─┐žųŲ▀ē▌ŗ(Rx controlŻ¼Tx control)║═8╬╗┤«▓óĪó▓ó┤«▐DōQŲ„Ż¼ĢrńŖļŖ┬ĘĮM│╔ĪŻŲõöĄō■Įė╩š▀^│╠×ķŻ║Įė╩š┐žųŲ▀ē▌ŗ(Rx control)┐žųŲADC AD7825īóĖ„éĆ═©Ą└Ą─šZę¶öĄūų╗»Ż¼▓ó░č▐DōQĮY╣¹┤µ╚ļĮė╩šŠÅø_ģ^(Rx FIFO)Ż¼ų▒ų┴Rx FIFOØMĢrRx controlķ_╩╝Ž“MPC860T╠ß╣®ų▄Ų┌ąįļ═¼▓Įą┼╠¢Ż¼Ņl┬╩×ķ32 kHzĪŻMPC860į┌ļ═¼▓Įą┼╠¢║═ĢrńŖą┼╠¢Ą─“īäėŽ┬ūx╚ĪRx FIFOųąĄ─öĄō■ĄĮSCCöĄō■Įė╩šŠÅø_ģ^ĪŻRx FIFOūx┐š(╝┤ūxųĖßśūĘ╔Ž┴╦īæųĖßś)║¾Ż¼Rx control═Żų╣Ž“MPC860░l╦═ļ═¼▓Įą┼╠¢ĮKų╣öĄō■é„▌öŻ¼═¼ĢrŽ“MPC860░l╦═ųąöÓą┼╠¢IRQ3Ż¼MPC860Ēææ¬ųąöÓ░čöĄō■Å─Įė╩šŠÅø_ģ^ūxĄĮĮė╩šring bufferųąĄ╚┤²æ¬ė├│╠ą“╠Ä└ĒĪŻŲõöĄō■░l╦═▀^│╠×ķŻ║MPC860═Ļ│╔IPĮŌĘŌčbĪóĮŌē║┐s║¾Ą─šZę¶öĄō■īóĢ■į┌Öz£yĄĮ░l╦═ŠÅø_ģ^┐╔ė├ĢrŻ¼▌ö│÷ĄĮSCC░l╦═ŠÅø_ģ^Ż¼═©ą┼┐žųŲŲ„╠ß╣®░l╦═ļ═¼▓Įą┼╠¢“īäėöĄō■é„▌öĄĮTx FIFO(░l╦═ŠÅø_ģ^)Ż¼┤²ĄĮTx FIFOØMĢr═Żų╣░l╦═ļ═¼▓Įą┼╠¢ĪŻöĄō■░l╦══Ļ║¾Ż¼CPMĢ■ŪÕ┴ŃŻ¼TxBD)ųąĄ─R╬╗▒Ē╩ŠMPC860┐╔Ž“SCC░l╦═ŠÅø_ģ^ųąčb╚ļą┬Ą─öĄō■Ż¼×ķŽ┬┤╬é„▌öū÷£╩éõĪŻ

ĪĪĪĪ1Ż«4 QMC═©ą┼ģfūh

ĪĪĪĪČÓ═©Ą└┐žųŲŲ„(QUICC Multichannel ControlerŻ¼QMC)╩Ū×ķ┴╦īŹ¼FĢrĘųÅ═ė├öĄō■é„▌öČ°įOėŗĄ─Ż¼╦³┐╔ęį░čĢrĘųÅ═ė├ļĄ─öĄō■Ęų░lĄĮČÓ▀_64éĆ▀ē▌ŗ═©Ą└ĪŻįō─Ż╩ĮŽ┬░č├┐ę╗ļĄ─öĄō■äØĘų│╔╚¶Ė╔éĆĢrŽČ(Timeslots)Ż¼├┐ĢrŽČ8 bĪŻį┌ĢrŽČĘų┼õ▒ĒųąęÄČ©├┐ĢrŽČöĄō■Å─ī┘ė┌─│éĆ═©Ą└Ż¼├┐éĆ═©Ą└Č╝ėąę╗ĮM╠žČ©Ą─ŠÅø_ģ^├Ķ╩÷Ę¹║═ŽÓæ¬Ą─ŠÅø_ģ^ĪŻę╗éĆĢrŽČĄ─öĄō■į┌╩š░lĢr▒╗Ę┼ų├į┌╠žČ©Ą─ŠÅø_ģ^└’Ż¼MPC860TŠ═┐╔░čĘų╔óĄ─öĄō■*į┌ę╗Ų░l╦═Ż¼╗“░č*į┌ę╗ŲĄ─öĄō■Ęų░lĄĮĖ„ūįīŻė├Ą─ŠÅø_ģ^Ż¼Č°▓╗ąĶę¬Ņ~═ŌĄ─╠Ä└ĒüĒģ^ĘųĖ„ĘNĖ„śėĄ─öĄō■┴„ĪŻ

ĪĪĪĪ2 BSP įOėŗīŹ¼F

ĪĪĪĪįOėŗųą▄ø╝■ķ_░lų„ę¬░³└©åóäė┤·┤aĄ─ŠÄīæĪó▓┘ū„ŽĄĮyĄ─ęŲų▓Īóė▓╝■“īäė│╠ą“║═šZ궊ÄĪóĮŌ┤a║═IPĘŌčbĪóĮŌĘŌčbæ¬ė├│╠ą“ĪŻŲ¬Ę∙ėąŽ▐Ż¼▒Š╬─āHĮķĮBBSPęŲų▓ĪŻBSP╝┤░Õ╝ēų¦│ų░³Ż¼Ųõ╣”─▄×ķė▓╝■Īó▄ø╝■│§╩╝╗»Īó╣ż│╠ė░Ž±Ą─Ž┬▌d║═įOéõ“īäėĄ╚ĪŻ

ĪĪĪĪ2Ż«1 BSPĄ─Č©ųŲ

ĪĪĪĪ¤ošō╩ŪBootRom▀Ć╩ŪVxWorksČ╝ę¬╩╣ė├BSP┤·┤aŻ¼BSPČ©ųŲąĶę¬Ė∙ō■ė▓░Õ┼õų├ĪóŽĄĮyįOėŗąĶŪ¾Īó▄ø╝■╣”─▄Ą╚īŹļHŪķørĪŻīŹļHķ_░l▀^│╠ųąŻ¼×ķ┴╦┐sČ╠«aŲĘķ_░lų▄Ų┌Ż¼═©│ŻęįWINDRIVER╣½╦ŠĄ─BSP─Ż░Õ╗“š▀Ą┌╚²ĘĮ╣½╦Š╠ß╣®Ą─┐╔╣®ģó┐╝Ą─BSP×ķ╗∙ĄAŻ¼Ė∙ō■▄øė▓╝■Š▀¾w┼õų├▀Mąąą▐Ė─Ż¼╠Ē╝ėą┬Ą─│╠ą““īäėą┬į÷ė▓╝■║═╣”─▄ĪŻ▒ŠšnŅ}ųąŽ╚░čAPC860ķ_░l░ÕĄ─BSPMPC860TEVB┐ĮžÉĄĮinstalldirŻ║Ż▄TornadoŻ▄targetŻ▄collfigŻ▄ppcs860─┐õøŽ┬Ż¼ų„ę¬ū÷Ž┬┴ąą▐Ė─ĪŻ

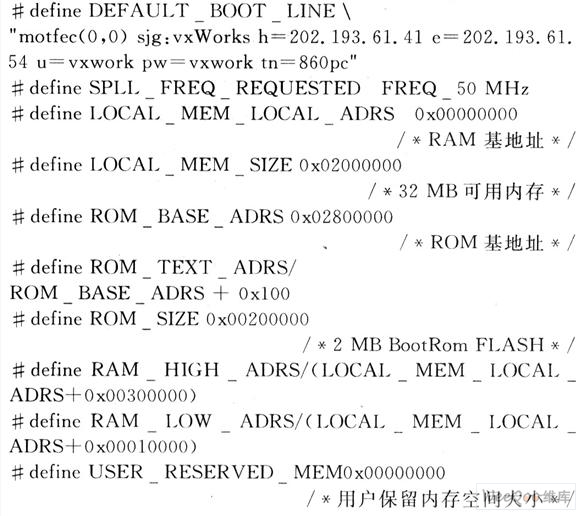

ĪĪĪĪ2Ż«1Ż«1 configŻ«h╬─╝■

ĪĪĪĪĖ∙ō■īŹļHŪķørŻ¼ąĶꬹ▐Ė─åóäėąąŻ¼ā╚┤µĄžųĘĪó╚▌┴┐Ą╚┼õų├Ż¼ą▐Ė─▓┐Ęų┤·┤a╚ńŽ┬Ż║

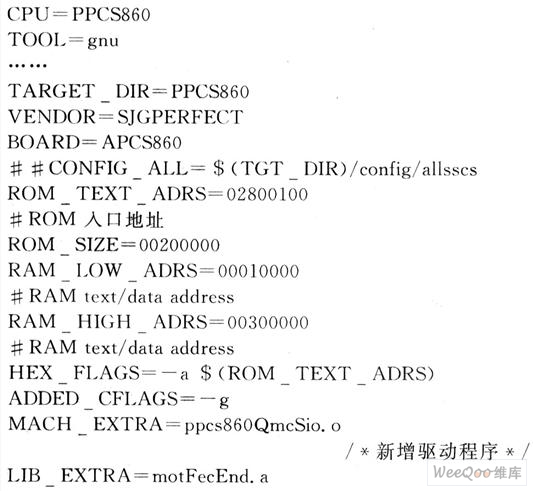

ĪĪĪĪ2Ż«1Ż«2 makefile╬─╝■Ą─ą▐Ė─

ĪĪĪĪmakefile╬─╝■Ą─ą▐Ė─Ż¼▓┐Ęų│╠ą“╚ńŽ┬Ż║

ĪĪĪĪ2Ż«1Ż«3 romInit╬─╝■ą▐Ė─

ĪĪĪĪromlnitŻ«s─ŻēK░³║¼┴╦VxWorksį┌ROMųąĄ─╚ļ┐┌³cromlnit()Ż¼╦³╩Ūå╬░Õ╔ŽļŖęį║¾ūŅŽ╚ł╠ąąĄ─ģRŠÄ│╠ą“┤·┤aĪŻįō║»öĄ╣”─▄░³└©╠Ä└ĒŲ„Ą─Å═╬╗Īóā╚┤µĄ─│§╩╝╗»ęį╝░Ųõ╦¹Ą─ūŅ╗∙▒Š║═▒žę¬Ą─│§╩╝╗»╣żū„ĪŻąĶꬹ▐Ė─Ą─ā╚╚▌╚ńŽ┬Ż║

ĪĪĪĪā╚▓┐┤µā”Ų„ė│╔õ╝─┤µŲ„IMMRĪŻįō╝─┤µŲ„ė├üĒś╦ūRā╚▓┐ĄžųĘ┐šķgĄ─╗∙ųĘŻ¼īóįō╝─┤µŲ„įOų├×ķĪ░FF000000Ī▒ĪŻ

ĪĪĪĪSIU─Ż╩Į┼õų├╝─┤µŲ„SIUMCRĪŻ░³└©ėą═Ō▓┐┐éŠĆų┘▓├Ų„┼õų├Ż¼═Ō▓┐masterĄ─ų¦│ųŻ¼DEBUGš{įćČ╦┐┌┼õų├Ż¼ŽĄĮyĮė┐┌ę²─_┼õų├ęį╝░Ųµ┼╝ąŻ“×ų¦│ųŻ¼īóįō╝─┤µŲ„įOų├×ķĪ░00E10000Ī▒ĪŻ

ĪĪĪĪBSPųąėæšōSDRAMĄ─│§╩╝╗»▀^│╠Ż¼╩ūŽ╚ī”MAMR╝─┤µŲ„Ą─│§╩╝╗»Ż¼į┘Ą├ĄĮUPMĄ─RAMĻć┴ą▒ĒĄ─ĄžųĘŻ¼╚╗║¾īóRAMĻć┴ą▒ĒĄžųĘųąĄ─ųĄīæ╚ļMPC860 RAM WORDS ARRAYųąŻ¼ūŅ║¾│§╩╝╗»ORęį╝░BR╝─┤µŲ„ĪŻ

ĪĪĪĪ2Ż«1Ż«4 ppcs860Ż«h

ĪĪĪĪppcs860Ż«h╩ŪģóöĄ┼õų├Ņ^╬─╝■Ż¼įō╬─╝■░³║¼┤¾┴┐║ĻČ©┴xŻ¼×ķ╩╣MPC860Tš²│Ż▀\ąąŪęSCC┤«┐┌╣żū„į┌QMCģfūh═Ė├„─Ż╩ĮŻ¼Ė∙ō■īŹļHąĶę¬ū÷┴╦╚ńŽ┬┼õų├Ż║

ĪĪĪĪ(1)ą▐Ė─ŽĄĮy│Ż┴┐ī”æ¬Ą─║ĻČ©┴xŻ║SCCxģóöĄį┌ļpČ╦┐┌RAMųą┤µā”Ą─Ų╩╝ĄžųĘĪóŠÅø_ģ^├Ķ╩÷Ę¹(BD)Ą─╗∙ĄžųĘĪóŠÅø_ģ^║═BDĄ─öĄ─┐Ą╚Ż╗

ĪĪĪĪ(2)┤«┐┌║═ĢrŽČĘų┼õ▒ĒĄ─│§╩╝╗»Ż¼ų„ę¬░³└©ĢrŽČĘų┼õĪóę²─_Ęų┼õĄ╚Ż¼═©▀^įOų├SI RAMģóöĄŻ¼ęÄČ©┴╦├┐éĆ▀ē▌ŗ═©Ą└ī”æ¬Ą─ĢrŽČ║═öĄō■┬Ęė╔Ż¼▒ŠŽĄĮyųą▀xō±SCC2║═TDMBĮė┐┌īŹ¼FQMC═©ą┼Ż¼ę²─_┼õų├╚ńŽ┬Ż║

ĪĪĪĪPC6 RSYNCŻ¼PA2 RXCŻ¼PA10 RXDŻ¼PA0 TXCĪŻPA11 TXD

ĪĪĪĪ(3)SCC2│§╩╝╗»Ż║įOų├SCC2╣żū„į┌QMC─Ż╩ĮŻ╗

ĪĪĪĪ(4)QMC╚½ŠųģóöĄ│§╩╝╗»Ż║MCBASE(ČÓ═©Ą└╗∙ĄžųĘųĖßś)Ż¼│§╩╝╗»×ķSCC2ī”æ¬═Ō▓┐BD▒ĒĄ─╗∙ĄžųĘŻ¼MRBLR(ūŅ┤¾Įė╩šŠÅø_ģ^ķLČ╚)Ż¼Įė╩šĪó░l╦═ĢrŽČĘų┼õ▒ĒŲ╩╝ĄžųĘĄ─ųĖßś(Rx S PTRŻ¼Tx S PTR)Ż¼Įė╩šĪó░l╦═ĢrŽČĘų┼õ▒Ē«öŪ░ĢrŽČĄ─ųĖßś(Rx PTRŻ¼TxPTR)Ż¼ųąöÓ裣h▒Ē╗∙ĄžųĘ(INTBASE)Ż¼ųąöÓ裣h▒ĒŽ┬ę╗┐╔ė├╚ļ┐┌Ą─ųĖßś(INTPTR)Ą╚Ż╗

ĪĪĪĪ(5)QMC╠žČ©═©Ą└ģóöĄ│§╩╝╗»Ż║TBASEŻ¼RBASE(įō▀ē▌ŗ═©Ą└Ą─ŠÅø_ģ^├Ķ╩÷Ę¹Ą─Ų╩╝ĄžųĘ)Ż¼TBPTRŻ¼RBPTR(«öŪ░░l╦═ĪóĮė╩šŠÅø_ģ^├Ķ╩÷Ę¹ųĖßś)Ż¼TMR-BLR(ūŅ┤¾Įė╩šÄ¼ķLČ╚)Ą╚ĪŻ

ĪĪĪĪ2Ż«1Ż«5 “īäė│╠ą“

ĪĪĪĪ“īäė│╠ą“ų▒Įėī”ė▓╝■▓┘ū„Ż¼īŹ¼Fė▓╝■║═▓┘ū„ŽĄĮyĪóæ¬ė├│╠ą“ų«ķgĄ─Į╗╗źĪŻąĶę¬ūįąąŠÄīæMPC860 SCC┤«┐┌“īäė│╠ą“ppcs860QmcSioŻ«cŻ¼═©ą┼ŲĮ┼_ųąSCC╣żū„į┌QMC Transparent─Ż╩ĮĪŻppcs860QmcSioŻ«c╬─╝■ųą░³║¼SIO_DRV_FUNCSĮYśŗ¾wųąČ©┴xĄ─5éĆ║»öĄ║═ųąöÓ╠Ä└Ē║»öĄppc860QmcInt()ĪóQmc▀ē▌ŗ═©Ą└Å═╬╗║»öĄppc860QmcChannelReset()ĪŻppc860SccIoctl()╠ß╣®┴╦ę╗ą®įOéõ┐žųŲ▀xĒŚŻ¼░³└©═Żų╣öĄō■é„╦═Īó▓ņ┐┤«öŪ░═©ą┼ĀŅæB(┐šķe▀Ć╩Ū├”)Īó▌åįā╗“ųąöÓ─Ż╩Į▀xō±Ą╚Ż╗ppc860sccInt()╠Ä└ĒQMC═©Ą└Ą─ųąöÓšłŪ¾Ż¼═©▀^ųąöÓĘĮ╩ĮīŹ¼FöĄō■Ą─╩š░l╣”─▄Ż╗ppc860SccStartuP()║»öĄåóäėę╗éĆ░l╦═ų▄Ų┌Ż╗ppc860SccCallbackInstall()░▓čb╗žš{║»öĄĪŻųąöÓ╠Ä└Ē║»öĄĄ─╣”─▄ėąŻ║

ĪĪĪĪ(1)╠ß╣®Įė╩šĪó░l╦═ųąöÓ╠Ä└Ē║»öĄŻ¼š{ė├╗žš{║»öĄ═Ļ│╔įOéõ║═▌^Ė▀īėģfūhų«ķgĄ─öĄō■é„╦═ĪŻ

ĪĪĪĪ(2)╠Ä└ĒöĄō■Įė╩š▀^│╠ųą│÷¼FĄ─Įė╩šöĄō■▀^ķLŻ¼öĄō■é„╦═▒╗Ų╚ĮKų╣Ą╚«É│ŻĪŻė╔ė┌▓╗ąĶę¬QMCĄ─▌åįā─Ż╩ĮŻ¼ę“┤╦ppc860SccPollInput()║═ppc860SccPollOutput()ęįNULL║»öĄĄ─ą╬╩ĮīŹ¼FĪŻ═¼Ģr▀ĆꬊÄīæsysSccSeri-alŻ«c╬─╝■Ż¼ą▐Ė─sysLibŻ«c╬─╝■║═usrConfigŻ«c╬─╝■ĪŻį┌sysSccQmcŻ«cųą╠ß╣®SCCįOéõ├Ķ╩÷Ę¹Ą─│§╩╝╗»└²│╠ĪóSCCųąöÓ▀BĮė└²│╠Ą╚Ż╗═©▀^ą▐Ė─sysLibŻ«c║═usrCon-figŻ«c╬─╝■ęįīŹ¼FVxWorksī”QMC“īäė│╠ą“Ą─š{ė├║═QMC“īäė│╠ą“┼cTTYŽĄĮyĄ─ÆņĮėĪŻ

ĪĪĪĪ2Ż«1Ż«6 ═©Ą└ųąöÓ╠Ä└Ē▀^│╠

ĪĪĪĪöĄō■╩š░lĄ─║╦ą─╩ŪųąöÓ╠Ä└Ē║»öĄĪŻQMCųąĄ─╦∙ėą▀ē▌ŗ═©Ą└╣▓ŽĒSCC2Ą─ųąöÓŻ¼SCC2ŠS│ųėąę╗éĆ╚½ŠųųąöÓ▒ĒŻ¼▒Ēųą├┐ę╗ĒŚ└’├µČ╝║¼ėą▀ē▌ŗ═©Ą└╠¢║═ųąöÓį┤Ż¼┐╔ęį▒╗“īäėūRäeęį╠Ä└Ē▓╗═¼ŪķørŽ┬│÷¼FĄ─╩┬╝■ĪŻųąöÓ░l╔·ĢrŻ¼“īäėÅ─SCCE╝─┤µŲ„└’├µ┼ąöÓ╚½ŠųųąöÓį┤Ż¼╚ń╣¹ųąöÓ╩Ūė╔▀ē▌ŗ═©Ą└ę²ŲŻ¼ųąöÓĘ■äš│╠ą“▒Ń▓ķšę╚½ŠųųąöÓ▒ĒęįšęĄĮįō▀ē▌ŗ═©Ą└Ż¼▓óÅ─ųąöÓŚl─┐└’├µÖz▓ķųąöÓą┼Žóęį┤_Č©╩Ū╩▓├┤ŅÉą═Ż¼į┘š{ė├ŽÓæ¬Ą─╩š░l║═Õeš`╠Ä└Ē║»öĄĪŻ

ĪĪĪĪ2Ż«1Ż«7 öĄō■Įė╩š║═░l╦═

ĪĪĪĪČÓ═©Ą└šZę¶═©ą┼ŽĄĮyųąMPC860T SCC┤«┐┌ĢrĘųÅ═ė├╝┤╣żū„į┌QMC─Ż╩ĮŻ¼▀ē▌ŗ═©Ą└Ą─═©ą┼ģfūh×ķTrasparent modeŻ¼įōģfūhāHé„▌öČ■▀MųŲöĄō■Ż¼▓╗ī”öĄō■┴„▀Mąą╬╗╝ē▓┘ū„Ż¼▓╗ģ^ĘųöĄō■ļųąĄ─Ė±╩Į╬╗ĪóŲų╣╬╗║═öĄō■╬╗Ą╚Ż¼▓╗ī”Įė╩šĄ─öĄō■ū÷ÖzÕe╠Ä└ĒŻ¼ę“Č°Š▀ėą▌^Ė▀Ą─öĄō■é„▌ö╦┘┬╩ĪŻ

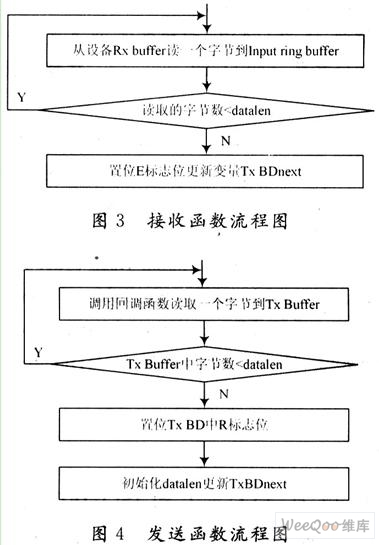

ĪĪĪĪĮė╩š║»öĄė╔ųąöÓĘ■äš└²│╠š{ė├ĪŻė╔ė┌╩Ū├┐Įė╩šę╗ļ«a╔·ę╗┤╬ųąöÓŻ¼╣╩Įė╩š║»öĄę▓├┐┤╬╠Ä└Ēę╗ļĄ─öĄō■ĪŻöĄō■Ą─Įė╩šė╔Įė╩š├Ķ╩÷Ę¹RxBD┐žųŲĪŻ«öę¬Įė╩šöĄō■ĢrŻ¼Įė╩š║»öĄ╩ūŽ╚ąĶę¬┤_Č©RxBDėąą¦Ż╗┤_Č©ø]ėąå¢Ņ}║¾Ż¼▓┼īóöĄō■Å─Įė╩šŠÅø_ģ^┐ĮžÉĄĮĮė╩šRing bufferŻ¼▓óÅ═╬╗RxBDŻ╗ʱätį┌▀MąąŽÓæ¬Õeš`╠Ä└Ē║¾Å═╬╗RxBDĪŻĮė╩š║»öĄ┴„│╠╚ńłD3╦∙╩ŠĪŻ

ĪĪĪĪöĄō■░l╦═▓╗š{ė├ųąöÓ╠Ä└Ē║»öĄŻ¼░l╦═║»öĄÖz£yĄĮ░l╦═ŠÅø_ģ^┐╔ė├(╝┤TxBDųąR╬╗×ķ1)║¾Ż¼š{ė├╗žš{║»öĄīóöĄō■Å─░l╦═Ring buffer┐ĮžÉĄĮ┤«┐┌░l╦═ŠÅø_ģ^(Txbuffer)ĪŻ▀@└’×ķ░l╦═╣”─▄ķ_▒┘ūŃē“┤¾Ą─Łhą╬ŠÅø_ģ^(ūŃęį╚▌╝{æ¬ė├│╠ą“├┐ę╗ļĄ─öĄō■)ĪŻ░l╦═║»öĄ┴„│╠╚ńłD4╦∙╩ŠĪŻ

ĪĪĪĪ2Ż«2 BSPš{įćĘĮĘ©║═ė÷ĄĮĄ─å¢Ņ}

ĪĪĪĪ2Ż«2Ż«1 š{įćĘĮĘ©

ĪĪĪĪķ_░lš{įćėąā╔ĘNĘĮĘ©Ż¼ę╗ĘN╩Ū╩╣ė├Ę┬šµŲ„═©▀^BDM(║¾Č╦š{įć─Ż╩Į)ę╗▓Į▓ĮĄžĖ·█Öš{įćŻ¼┴Ēę╗ĘN╩Ū═©▀^³c¤¶Ą─ĘĮ╩Į▀Mąą╦∙ų^Ą─Ī░║┌Ī▒š{ĪŻĪ░║┌Ī▒š{Ą─ĘĮĘ©╩Ū═©▀^Ī░¤¶Ī▒ķWĪóė├╩Š▓©Ų„£yŲ¼▀xĄ╚Ż¼Ė∙ō■═Ō▓┐¼FŽ¾║═╦∙ŠÄĄ─£yįć┤·┤a▀Mąą▒╚▌^Ęų╬÷üĒš{įć│╠ą“ĪŻ▀MąąĪ░║┌Ī▒š{Ą──┐Ą─╩Ūš{═©ą┼┤«┐┌▓┐Ęų┤·┤aŻ¼╦▐ų„ÖC┐╔ęį═©▀^┤«┐┌┼c─┐ś╦ÖCĄ─═©ą┼Ż¼╚╗║¾į┘š{įćŲõ╦¹▓┐ĘųĪŻš{įć┴„│╠Ęų│╔ā╔▓┐ĘųĪŻ╩ūŽ╚╩ŪŅAā╚║╦åóäė┤·┤a(Pre-Kernel Initializa-tion)Ż¼┤²ūŅąĪā╚║╦åóäėš²│Ż║¾į┘╠Ē╝ėIŻ»OŽĄĮyĪó╬─╝■ŽĄĮyĪóŠWĮjŽĄĮyĄ╚ĮM╝■║═š{įćæ¬ė├│╠ą“ĪŻ╩╣ė├Ę┬šµŲ„Vi-sion Probe═©▀^BDMĘĮ╩Įš{įćBSP▓óīóBootRomė│Ž±¤²╚ļFLASHĪŻ

ĪĪĪĪ2Ż«2Ż«2 š{įćųąė÷ĄĮĄ─å¢Ņ}

ĪĪĪĪ(1)ŽĄĮy¤oĘ©š²│ŻÅ═╬╗

ĪĪĪĪį┌š{įć▀^│╠ųąŻ¼░l¼FMPC860TĄ─CLKOUTę²─_¤o▌ö│÷ą┼╠¢Ż¼ŽĄĮy╔ŽļŖÅ═╬╗▀^│╠ø]ėą═Ļ│╔Ż¼ŽĄĮy¤oĘ©š²│Ż╣żū„ĪŻ│§▓Į┼ąöÓ╩Ūė▓╝■å¢Ņ}ĪŻė├╚fė├▒Ē║═╩Š▓©Ų„ų▓ĮÖz▓ķ╔ŽļŖÅ═╬╗Īóė▓╝■Å═╬╗Īó▄ø╝■Å═╬╗ĪóĢrńŖ▌ö╚ļ║═BDMš{įćĄ╚─ŻēKļŖ┬ĘŻ¼░l¼Fš²│ŻĪŻ┼ąöÓ╩ŪBGA║ĖĮė│÷¼Få¢Ņ}Ż¼īóąŠŲ¼╚ĪŽ┬Ż¼ųžą┬║ĖĮėŻ¼ŽĄĮyÅ═╬╗š²│ŻŻ¼ĢrńŖą┼╠¢▌ö│÷ĘĆČ©š²│ŻĪŻ

ĪĪĪĪ(2)ŠWĮj¤oĘ©┼c═ŌĮń═©ą┼

ĪĪĪĪ100 MbŻ»s┐ņ╦┘ęį╠½ŠW“īäė╝ė▌dųąŻ¼ŠWĮjīėģfūh¤oĘ©▀\ąąŻ¼─┐ś╦░Õ¤oĘ©┼c═ŌĮńŠWĮjĮ©┴ó┬ōŽĄĪŻ─┐ś╦░ÕŠWĮjåóäėĢr░l│÷Ą─MACĄžųĘą┼Žóļ═ŌĮń¤oĘ©╩šĄĮĪŻ═©▀^Ę┬šµŲ„░l¼F│╠ą“å╬▓Į▀\ąąš²│ŻĪŻĮø▀^Ę┤Å═įć“×║═£yįćŻ¼ūŅĮK░l¼Fę“SDRAM│§╩╝╗»│╠ą“ø]ėą▀\ąąī¦ų┬│╠ą“▀\ąą(ąĶę¬SDRAMų¦│ų═╗░l─Ż╩Į)│÷ÕeĪŻĖ³Ė─š{įćĘĮ╩ĮŻ¼īóBootRomķ_╩╝Ą─╦∙ėą│╠ą“¤²╚ļFLASHŻ¼╔ŽļŖåóäėŻ¼ŠWĮjš²│ŻŻ¼─┐ś╦░Õ┼c═ŌĮńĮ©┴ó┴╝║├Ą─ŠWĮj═©ą┼ĪŻ

ĪĪĪĪ3 ĮY šZ

ĪĪĪĪįōŽĄĮyį┌īŹļH£yįćųąįÆę¶┘|┴┐ĘĆČ©Ż¼£yįćĢr┬Ģę¶ŪÕ╬·Ż¼ø]ėą┤«ö_║═ļs궯¼ø]ėą▌^┤¾čė▀tŻ¼šf├„ė▓╝■įOėŗš²┤_═ĻéõŻ¼QMC“īäė│╠ą“║═šZ궊ÄĮŌ┤a║═IPĘŌčb┼cĮŌĘŌčbæ¬ė├│╠ą“ąį─▄ā×┴╝ĪŻ

ĪĪĪĪ╚ń╣¹░Õ┐©╔ŽšZę¶═©Ą└Ė³ČÓŻ¼ät├┐ļĄ─ĢrŽČį÷ČÓĪóķLČ╚į÷┤¾Ż¼ę“×ķFPGAā╚▓┐ļŖ┬Ę╦∙╠ß╣®Ą─Ą─ļ═¼▓Įą┼╠¢ų▄Ų┌▓ó▓╗Ė─ūāŻ¼╦∙ęįų╗╩ŪīŹļHöĄō■é„▌ö╦┘┬╩╠ßĖ▀Ż¼┐╔ęį▒ŻūCĖ„┬ĘšZ궥─═¼▓Į║═īŹĢrąįĪŻŽĄĮyųąQMC╣żū„į┌Transparent ModeŽ▐ųŲ┴╦╦³Ą─æ¬ė├ĘČć·Ż¼╚ń║╬Ė─▀M╩╣ŽĄĮyų¦│ųČÓĘN═©ą┼ģfūh╩ŪąĶę¬▀Mę╗▓Į蹊┐Ą─å¢Ņ}ĪŻ

╝ė║├ėč

╝ė║├ėč  ░lČ╠ą┼

░lČ╠ą┼

Post ByŻ║2010-12-1 9:18:56

Post ByŻ║2010-12-1 9:18:56