Ė┼ė[

ĪĪĪĪĖ▀Č╦įO(sh©©)ėŗ(j©¼)╣żŠ▀×ķ╔┘ėą╔§╩Ūø]ėąė▓╝■įO(sh©©)ėŗ(j©¼)╝╝ąg(sh©┤)Ą─╣ż│╠Ĥ║═┐ŲīW(xu©”)╝ę╠ß╣®¼F(xi©żn)ł÷┐╔ŠÄ│╠ķTĻć┴ąŻ©FPGAŻ®ĪŻ¤ošō─Ń╩╣ė├łDą╬╗»įO(sh©©)ėŗ(j©¼)│╠ą“Ż¼ANSI CšZčį▀Ć╩ŪVHDLšZčįŻ¼╚ń┤╦Å═(f©┤)ļsĄ─║Ž│╔╣ż╦ćĢ■▓╗Į¹ūī╚╦╚źŽļFPGAšµīŹ(sh©¬)Ą─▀\(y©┤n)ū„ŪķørĪŻį┌▀@éĆąŠŲ¼ųąĄ─│╠ą“į┌▀@ą®┐╔įO(sh©©)ų├╣ĶŲ¼ķgĄĮĄū╩Ū╚ń║╬╣żū„Ą─ĪŻ▒ŠĢ°Ģ■╩╣ĘŪöĄ(sh©┤)ūų╗»įO(sh©©)ėŗ(j©¼)╚╦åT├„░ūFPGAŻ©¼F(xi©żn)ł÷┐╔ŠÄ│╠ķTĻć┴ąŻ®Ą─╗∙ĄA(ch©│)ų¬ūR╝░Ųõ╣żū„įŁ└ĒĪŻ┤╦ą┼Žóį┌╩╣ė├Ė▀Č╦įO(sh©©)ėŗ(j©¼)╣żŠ▀Ģr═¼śė╩«Ęųėąė├Ż¼ŽŻ═¹┐╔ęį×ķ└ĒĮŌ▀@ę╗╠žäe╝╝ąg(sh©┤)╠ß╣®ę╗ą®ŠĆ╦„ĪŻ

FPGA-¼F(xi©żn)ł÷┐╔ŠÄ│╠ķTĻć┴ą

ĪĪĪĪ├┐ę╗ēKFPGAąŠŲ¼Č╝╩Ūė╔ėąŽ▐ČÓéĆĦėą┐╔ŠÄ│╠▀BĮėĄ─ŅA(y©┤)Č©┴xį┤ĮM│╔üĒīŹ(sh©¬)¼F(xi©żn)ę╗ĘN┐╔ųžśŗ(g©░u)öĄ(sh©┤)ūųļŖ┬ĘĪŻ

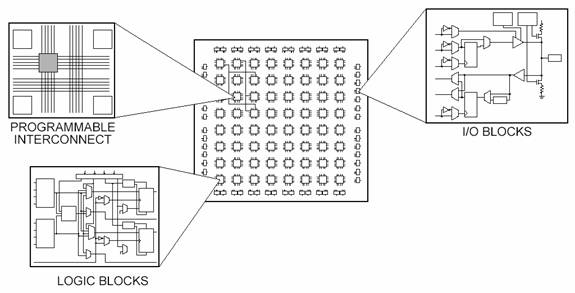

łD1.FPGA▓╗═¼śŗ(g©░u)│╔

ĪĪĪĪFPGAąŠŲ¼šf├„Ģ°ųąŻ¼░³║¼┴╦┐╔ŠÄ│╠▀ē▌ŗ─ŻēKĄ─öĄ(sh©┤)┴┐Īó╣╠Č©╣”─▄▀ē▌ŗ─ŻēKŻ©╚ń│╦Ę©Ų„Ż®Ą─öĄ(sh©┤)─┐╝░┤µā”Ų„┘Yį┤Ż©╚ńŪČ╚ļ╩ĮRAMŻ®Ą─┤¾ąĪĪŻFPGAąŠŲ¼ųą▀Ćėą║▄ČÓŲõ╦³Ą─▓┐ĘųŻ¼Ą½╩Ūęį╔ŽųĖś╦(bi©Īo)═©│Ż╩Ū×ķ╠žČ©æ¬(y©®ng)ė├▀xō±║═▒╚▌^FPGAĢrŻ¼ūŅųžę¬Ą─ģó┐╝ųĖś╦(bi©Īo)ĪŻ

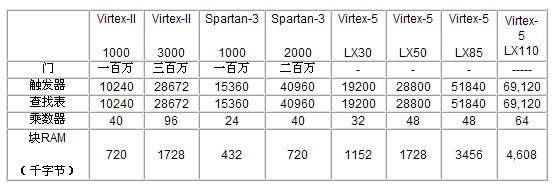

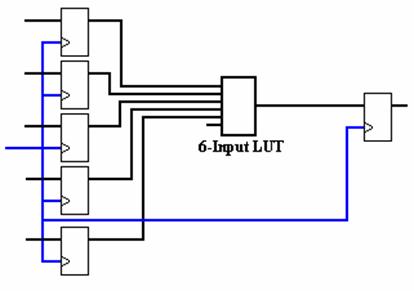

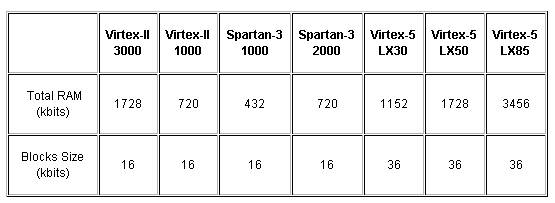

ĪĪĪĪį┌ūŅĄūīėŻ¼┐╔┼õų├▀ē▌ŗ─ŻēKŻ©╚ńŲ¼╗“▀ē▌ŗå╬į¬Ż®ėąų°ā╔ĘNūŅ╗∙▒ŠĄ─▓┐╝■Ż║ė|░l(f©Ī)Ų„║═▓ķšę▒ĒŻ©LUTŻ®ĪŻ▀@║▄ųžę¬Ż¼ę“?y©żn)ķĖ„ĘNFPGA╝ęūÕų«╦∙ęįĖ„▓╗ŽÓ═¼Ż¼Š═╩Ūę“?y©żn)ķė|░l(f©Ī)Ų„║═▓ķšę▒ĒĮM║ŽĄ─ĘĮ╩Į▓╗═¼ĪŻ└²╚ńŻ¼Virtex-II ŽĄ┴ąĄ─FPGA Ż¼╦³Ą─Ų¼Š▀ėąā╔éĆ▓ķšę▒Ē║═ā╔éĆė|░l(f©Ī)Ų„Ż¼Č°Virtex-5 FPGAĄ─Ų¼Š▀ėą4éĆ▓ķšę▒Ē║═4éĆė|░l(f©Ī)Ų„ĪŻ▓ķšę▒Ē▒Š╔ĒĄ─ĮY(ji©”)śŗ(g©░u)ę▓┐╔─▄Ė„▓╗ŽÓ═¼Ż©4▌ö╚ļ╗“6▌ö╚ļŻ®ĪŻĻP(gu©Īn)ė┌▓ķšę▒Ē╣żū„įŁ└ĒĄ─Ė³ČÓą┼Žóīóį┌║¾├µĄ─š┬╣Ø(ji©”)ųąĮo│÷ĪŻ

ĪĪĪĪ▒Ē1ųą┴ą│÷┴╦į┌NI LabVIEW FPGAė▓╝■─┐ś╦(bi©Īo)ųą╩╣ė├Ą─FPGAĄ─ųĖś╦(bi©Īo)ĪŻ▀ē▌ŗķTĄ─öĄ(sh©┤)┴┐╩Ūę╗ĘNīóFPGAąŠŲ¼┼cASIC╝╝ąg(sh©┤)▀M(j©¼n)ąą▒╚▌^Ą─é„Įy(t©»ng)ĘĮĘ©Ż¼Ą½╩Ū╦³▓ó▓╗─▄šµīŹ(sh©¬)Ąž▒Ē╩÷FPGAā╚(n©©i)▓┐Ą─¬Ü(d©▓)┴óå╬į¬Ą─öĄ(sh©┤)┴┐ĪŻ▀@Š═╩ŪXilinx╣½╦Šø]ėąį┌ą┬ą═Virtex-5ŽĄ┴ąųąųĖČ©▀ē▌ŗķTöĄ(sh©┤)┴┐Ą─įŁę“ų«ę╗ĪŻ

▒Ē1.▓╗═¼ŽĄ┴ąFPGAį┤ęÄ(gu©®)Ė±

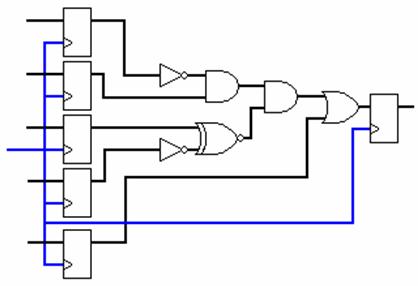

ĪĪĪĪ×ķ┴╦Ė³║├Ąž└ĒĮŌ▀@ą®ęÄ(gu©®)Ė±Ą─ęŌ┴xŻ¼īóŠÄ┤a┐╝æ]×ķ║Ž│╔Ą─öĄ(sh©┤)ūųļŖ┬Ę─Ż╩ĮĪŻī”╚╬║╬ę╗Č╬║Ž│╔┤·┤aŻ¼╗“łDą╬╗»╗“╬─▒Šą╬╩ĮŻ¼Č╝ėąŽÓæ¬(y©®ng)Ą─ļŖ┬ĘłDĘ┤ė│▀ē▌ŗĮM╝■įō╚ń║╬▀BŠĆĪŻ═©▀^ę╗Č╬║åå╬▓╝Ā¢▀ē▌ŗļŖ┬Ę┴╦ĮŌŽ┬ŽÓæ¬(y©®ng)Ą─╩ŠęŌłDĪŻłD2▒Ē╩ŠĄ─╩Ūé„▀f5éĆ▓╝Ā¢ą┼╠¢▓óŪę┐╔łDą╬╗»ėŗ(j©¼)╦Ń╦∙Ą├Ą─Č■▀M(j©¼n)ųŲųĄĄ─╣”─▄ĮMĪŻ

łD2.▌d╚ļ5éĆą┼╠¢Ą─║åå╬▓╝Ā¢▀ē▌ŗ

ĪĪĪĪį┌═©│ŻŪķørŽ┬Ż©LabVIEW SCTLĪ¬å╬ų▄Ų┌Č©ĢrŁh(hu©ón)┬Ę═ŌŻ®Ż¼łD2╦∙╩ŠŽÓæ¬(y©®ng)ļŖ┬ĘłD═¼łD3╦∙╩ŠŽÓĮ³ĪŻ

łD3.×ķłD2ųą▓╝Ā¢▀ē▌ŗĄ─ŽÓæ¬(y©®ng)ļŖ┬ĘłD

ĪĪĪĪļm╚╗║▄ļy├„░ūŻ¼Ą½╩ŪīŹ(sh©¬)ļH╔Ž▀@└’äō(chu©żng)Į©┴╦ā╔éĆ▓óąąĘųų¦Ą─ļŖ┬ĘĪŻūŅ╔Ž├µĄ─5Śl║┌ŠĆ▒╗Ę┤üĄĮĄ┌ę╗éĆĘųų¦Ż¼╦³į┌├┐éĆ▓╝Ā¢▓┘ū„ķg╠Ē╝ė┴╦ė|░l(f©Ī)Ų„ĪŻūŅŽ┬├µĄ─5Śl║┌ŠĆśŗ(g©░u)│╔┴╦Ą┌Č■éĆ▀ē▌ŗµ£ĪŻŲõųąę╗ų¦┬Ęį┌├┐▓Į▓┘ū„ų«ķgį÷╝ė┴╦═¼▓Į╝─┤µŲ„Ż¼┴Ēę╗Śl▀ē▌ŗµ£?zh©│n)Ū┤_▒Żł╠(zh©¬)ąąöĄ(sh©┤)ō■(j©┤)┴„Ą─ĪŻ▒ŠļŖ┬ĘłDš²│Ż╣żū„Ģr┐é╣▓ąĶę¬12éĆė|░l(f©Ī)Ų„║═12éĆ▓ķšę▒ĒĪŻ╔ŽČ╦Ęųų¦║═├┐éĆį¬╝■īóį┌ęį║¾š┬╣Ø(ji©”)Ęų╬÷ĪŻ

ė|░l(f©Ī)Ų„

łD4.ė|░l(f©Ī)Ų„Ę¹╠¢

ĪĪĪĪė|░l(f©Ī)Ų„╩ŪČ■▀M(j©¼n)ųŲęŲ╬╗╝─┤µŲ„Ż¼ė├ė┌═¼▓Į▀ē▌ŗęį╝░▒Ż┤µĢrńŖŻ©├}ø_Ż®ų▄Ų┌ā╚(n©©i)Ą─▀ē▌ŗĀŅæB(t©żi)ĪŻį┌├┐éĆĢrķgŻ©├}ø_Ż®▀ģ螯¼ė|░l(f©Ī)Ų„į┌▌ö╚ļĢrµiČ©1Ż©šµŻ®╗“0Ż©╝┘Ż®ųĄ▓óŪę▒Ż┤µ┤╦ųĄų▒ĄĮŽ┬┤╬ĢrńŖŻ©├}ø_Ż®▀ģčžĪŻį┌š²│ŻŪķørŽ┬Ż¼LabVIEW FPGAį┌├┐┤╬▓┘ū„ų«ķgČ╝įO(sh©©)ų├ę╗éĆė|░l(f©Ī)Ų„Ż¼ęį▒ŻūCėąūŃē“Ą─ĢrķgüĒł╠(zh©¬)ąą├┐▓Į▓┘ū„ĪŻī”┤╦┬╔Ą─└²═Ōų╗░l(f©Ī)╔·į┌SCTLĮY(ji©”)śŗ(g©░u)ųąīæ┤·┤aĄ─ŪķørĪŻį┌▀@éĆ╠ž╩ŌĄ─Łh(hu©ón)┬ĘĮY(ji©”)śŗ(g©░u)ųąŻ¼ė|░l(f©Ī)Ų„ų╗Ę┼ų├į┌ķ]Łh(hu©ón)Ą³┤·Ą─╩╝─®Č╬Ż¼▓óŪęė╔ŠÄ│╠š▀┐╝æ]Č©Ģrę“╦žüĒøQČ©╚ń║╬Ę┼ų├ĪŻī”SCTLā╚(n©©i)┤·┤a╚ń║╬═¼▓ĮĄ─Ė³ČÓā╚(n©©i)╚▌īóį┌ęį║¾š┬╣Ø(ji©”)ųąėæšōĪŻłD5▒Ē╩ŠĄ─╩ŪłD3Ą─╔ŽČ╦Ęųų¦Ż¼ė|░l(f©Ī)Ų„ė╔╝t╔½Ė▀┴┴▒Ē╩ŠĪŻ

łD5.└LųŲė╔╝t╔½Ė▀┴┴▒Ē╩Š│÷ė|░l(f©Ī)Ų„Ą─ļŖ┬ĘłD

▓ķšę▒Ē

łD6.ļp╦─▌ö╚ļ▓ķšę▒Ē

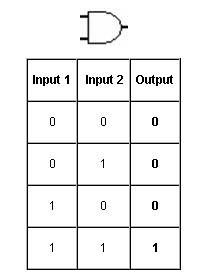

ĪĪĪĪłD6╦∙╩Š╩ŠęŌłDųąĄ─Ųõ╦¹▀ē▌ŗļŖ┬Ę═©▀^╩╣ė├╔┘┴┐▓ķšę▒Ēą╬╩ĮĄ─ļSÖC(j©®)┤µ╚Ī┤µā”Ų„īŹ(sh©¬)¼F(xi©żn)ĪŻ╬ęéā┐╔ęį║åå╬Ąž╝┘Č©FPGAųąŽĄĮy(t©»ng)ķTĄ─öĄ(sh©┤)┴┐┐╔ģó┐╝┼cĘŪķT(NAND)ęį╝░╗“ĘŪķT(NOR)Ą─öĄ(sh©┤)┴┐Ż¼Ą½īŹ(sh©¬)ļH╔ŽŻ¼╦∙ėąĄ─ĮM║Ž▀ē▌ŗŻ©┼cķTĪó╗“ķTĪó┼cĘŪķTĪó«É╗“ķTĄ╚Ż®Č╝╩Ū═©▀^▓ķšę▒Ē┤µā”Ų„ųąĄ─šµųĄ▒ĒüĒīŹ(sh©¬)¼F(xi©żn)ĪŻšµųĄ▒Ē╩Ū▌ö│÷ī”æ¬(y©®ng)ė┌├┐éĆ▌ö╚ļųĄĮM║ŽĄ─ŅA(y©┤)Č©┴x▒ĒŻ©¼F(xi©żn)į┌┐©ųZłDĄ─ųžę¬ąįį┌─ŃĄ─Ņ^─Xųą┐╔─▄Ģ■┬²┬²ĄŁ╗»Ż®ĪŻęįŽ┬╩Ūī”öĄ(sh©┤)ūų▀ē▌ŗļŖ┬Ęšn│╠Ą─┐ņ╦┘╗žŅÖŻ║▒╚╚ńŻ¼łD7╩Ū▓╝Ā¢▀ē▌ŗ┼cķT▓┘ū„▀^│╠ĪŻ

ĪĪĪĪ▀@╩Ūī”öĄ(sh©┤)ūų▀ē▌ŗšn│╠Ą─┐ņ╦┘╗žŅÖŻ║

ĪĪĪĪ└²╚ńŻ¼łD7ųą’@╩Š┴╦▓╝Ā¢ą═AND▓┘ū„ĪŻ

łD7.▓╝Ā¢ą═AND▓┘ū„

▒Ē2.▓╝Ā¢┼cķT▓┘ū„Ą─šµųĄ▒Ē

ĪĪĪĪ─Ń┐╔ęįšJ(r©©n)×ķ▌ö╚ļųĄ╩Ū╦∙ėą▌ö│÷ųĄĄ─öĄ(sh©┤)ūų╦„ę²Ż¼╚ń▒Ē3╦∙╩ŠĪŻ

▒Ē3.▓╝Ā¢┼cķT▓┴▓┘ū„Ą─šµųĄ▓ķšę▒ĒīŹ(sh©¬)¼F(xi©żn)

ĪĪĪĪVirtex-II║═Spartan-3ŽĄ┴ąFPGAąŠŲ¼ėąų°4▌ö╚ļ▓ķšę▒ĒüĒīŹ(sh©¬)¼F(xi©żn)šµš²Ą─4▌ö╚ļą┼╠¢Ą─16ĘNĮM║ŽĪŻłD8Š═╩Ūę╗éĆ╦─▌ö╚ļļŖ┬ĘīŹ(sh©¬)¼F(xi©żn)Ą─└²ūėĪŻ

łD8.▌ö╚ļ▓╝Ā¢▀ē▌ŗĄ─╦─ą┼╠¢ļŖ┬Ę

▒Ē4╦∙╩Š×ķ╩╣ė├ļp╦─▌ö╚ļ▓ķšę▒ĒīŹ(sh©¬)¼F(xi©żn)Ą─ŽÓæ¬(y©®ng)Ą─šµųĄ▒ĒĪŻ

▒Ē4.łD8ųą╦∙╩ŠŽÓæ¬(y©®ng)šµųĄ▒Ē

ĪĪĪĪVirtex-5ŽĄ┴ąĄ─FPGA╩╣ė├ļp┴∙▌ö╚ļ▓ķšę▒ĒŻ¼┐╔ęį═©▀^6éĆ▓╗═¼▌ö╚ļą┼╠¢Ą─64ĘNĮM║ŽüĒīŹ(sh©¬)¼F(xi©żn)šµųĄ▒ĒĪŻę“?y©żn)ķė|░l(f©Ī)Ų„ų«ķgĄ─ĮM║Ž▀ē▌ŗ╩«ĘųÅ═(f©┤)ļsŻ¼╦∙ęįį┌LabVIEW FPGAųą╩╣ė├SCTLę▓įĮüĒįĮųžę¬ĪŻŽ┬ę╗╣Ø(ji©”)īóųv╩÷SCTL╚ń║╬ā×(y©Łu)╗»└¹ė├LabVIEWųąĄ─FPGAį┤ĪŻ

SCTL

ĪĪĪĪ╔ŽÄū╣Ø(ji©”)ųą╩╣ė├Ą─┤·┤a└²ūė╝┘Č©┤·┤a╩ŪįO(sh©©)ų├į┌SCTL═Ō▓┐Ż¼▓ó×ķ▒ŻūCł╠(zh©¬)ąą═¼▓ĮöĄ(sh©┤)ō■(j©┤)┴┐ę▓═¼▓Į┴╦ĖĮ╝ėļŖ┬ĘĪŻSCTL╩ŪLabVIEW FPGAųąę╗éĆ╠ž╩ŌĮY(ji©”)śŗ(g©░u)Ż¼╔·│╔ę╗éĆĖ³×ķā×(y©Łu)╗»Ą─ļŖ┬ĘłDŻ¼ęįŲ┌═¹▀_(d©ó)ĄĮį┌ę╗éĆĢrńŖ(├}ø_)ų▄Ų┌ā╚(n©©i)ł╠(zh©¬)ąą═Ļ╦∙ėą▀ē▌ŗļŖ┬ĘĘųų¦ĪŻ└²╚ńŻ¼╚¶įO(sh©©)ų├SCTLį┌40MHZ▀\(y©┤n)ąąŻ¼ät╦∙ėą▀ē▌ŗļŖ┬ĘĘųų¦īóį┌25nsā╚(n©©i)ł╠(zh©¬)ąą═Ļ«ģĪŻ

ĪĪĪĪ╚ń╣¹į┌SCTLųąįO(sh©©)ų├Ū░└²ųą═¼śėĄ─▓╝Ā¢▀ē▌ŗļŖ┬ĘŻ©╚ńłD9╦∙╩ŠŻ®Ż¼ät╔·│╔╚ńłD10╦∙╩ŠĄ─ŽÓæ¬(y©®ng)ļŖ┬Ę╩ŠęŌłDĪŻ

łD9.ĖĮėąSTCLĄ─║åå╬▓╝Ā¢▀ē▌ŗ

łD10.łD9╦∙╩Š▓╝Ā¢▀ē▌ŗŽÓæ¬(y©®ng)Ą─ļŖ┬ĘłD

ĪĪĪĪ║▄├„’@Ż¼▀@ĘNīŹ(sh©¬)¼F(xi©żn)ĘĮĘ©║åå╬ČÓ┴╦ĪŻį┌Virtex-II╗“Spartan-3ŽĄ┴ąFPGAųąŻ¼ė|░l(f©Ī)Ų„ķgĄ─▀ē▌ŗąĶę¬ų┴╔┘2éĆ4▌ö╚ļ▓ķšę▒ĒŻ¼╚ńłD11╦∙╩ŠĪŻ

łD11.łD10ųąļŖ┬ĘłDĄ─ļp╦─▌ö╚ļ▓ķšę▒ĒīŹ(sh©¬)¼F(xi©żn)

ĪĪĪĪė╔ė┌Virtex-5ŽĄ┴ąFPGAėąų°6▌ö╚ļĄ─▓ķšę▒ĒŻ¼ė├æ¶┐╔ęįį┌ę╗éĆ▓ķšę▒ĒųąīŹ(sh©¬)¼F(xi©żn)ŽÓ═¼öĄ(sh©┤)┴┐Ą─▀ē▌ŗŻ¼╚ńłD12╦∙╩ŠĪŻ

łD12.łD10ųąļp┴∙▌ö╚ļ▓ķšę▒ĒīŹ(sh©¬)

ĪĪĪĪ▒Š└²ųą╩╣ė├Ą─SCTLŻ©╚ńłD9╦∙╩ŠŻ®įO(sh©©)ų├į┌40MHZŽ┬▀\(y©┤n)ąąŻ¼▀@ęŌ╬Čų°į┌╚╬ęŌė|░l(f©Ī)Ų„ų«ķg▀ē▌ŗļŖ┬Ę▒žĒÜį┌25nsā╚(n©©i)═Ļ│╔ł╠(zh©¬)ąąĪŻļŖūėį┌ļŖ┬Ęųąé„▓źĄ─╦┘Č╚øQČ©┴╦┤·┤ał╠(zh©¬)ąąĄ─ūŅ┤¾╦┘Č╚ĪŻĻP(gu©Īn)µI┬ĘŠĆ╩ŪėąūŅķLé„▓źčė▀tĄ─▀ē▌ŗļŖ┬ĘĘųų¦Ż¼╦³øQČ©┴╦įō▓┐ĘųļŖ┬Ęųą└ĒšōūŅ┤¾ĢrńŖ╦┘┬╩ĪŻVirtex-5 FPGA╔ŽĄ─ļp┴∙▌ö╚ļ▓ķšę▒Ē▓╗āH£p╔┘īŹ(sh©¬)¼F(xi©żn)ĮoČ©▀ē▌ŗļŖ┬Ę╦∙ąĶꬥ─▓ķšę▒Ē┐éöĄ(sh©┤)Ż¼Č°Ūę£p╔┘ļŖūė═©▀^▀ē▌ŗļŖ┬ĘĄ─é„▓źčė▀tŻ©ĢrķgŻ®ĪŻVirtex-5ŽĄ┴ąFPGAųąĄ─6▌ö╚ļ▓ķšę▒Ē▓╗āH┐╔ęį£p╔┘īŹ(sh©¬)¼F(xi©żn)╠žČ©▀ē▌ŗČ°ąĶꬥ─▓ķšę▒ĒĄ─öĄ(sh©┤)┴┐Ż¼Č°Ūę┐╔ęįĮĄĄ═▀ē▌ŗųąļŖ┴„Ą─é„▌öčėĢrĪŻ▀@ęŌ╬Čų°Ż¼─·┐╔║åå╬Ąž═©▀^▀xō±ę╗éĆ╗∙ė┌Virtex-5Ą─ė▓╝■ųĖś╦(bi©Īo)įO(sh©©)ų├ŽÓ═¼Ą─SCTLŻ¼ūĘŪ¾Ė³┐ņĄ─Ģrķg╦┘Č╚ĪŻ

ĪĪšł▓ķ┐┤Ž┬ĘĮ░ūŲżĢ°Ą─ī”▓▀┴ą▒ĒŻ¼½@╚ĪĖ³ČÓVirtex-5 FPGAŽÓĻP(gu©Īn)ą┼ŽóĪŻ

│╦öĄ(sh©┤)Ų„║═DSPŲ¼

ĪĪĪĪ┐┤ŲüĒ║åå╬Ą─ā╔öĄ(sh©┤)ŽÓ│╦▀\(y©┤n)╦Ńį┌öĄ(sh©┤)ūųļŖ┬ĘųąīŹ(sh©¬)¼F(xi©żn)ŲüĒ╩Ū╩«ĘųÅ═(f©┤)ļsĄ─Ż¼ę▓╩ŪśO×ķŽ¹║─┘Yį┤Ą─ĪŻ×ķ╠ß╣®ŽÓĻP(gu©Īn)ģó┐╝Ż¼łD14╦∙╩Š╩Ūę╗ĘN╩╣ė├ĮM║Ž▀ē▌ŗļŖ┬ĘīŹ(sh©¬)¼F(xi©żn)4Ī┴4ūų╣Ø(ji©”)│╦öĄ(sh©┤)Ų„Ą─╩ŠęŌłDĪŻ

łD14.ā╔éĆ4ūų╣Ø(ji©”)▌ö╚ļŽÓ│╦Ą─ļŖ┬ĘłD

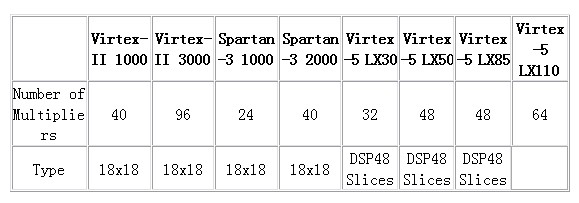

ĪĪĪĪįćŽļā╔éĆ32ūų╣Ø(ji©”)Ą─öĄ(sh©┤)ūųŽÓ│╦ę¬═©▀^2000ČÓ▓Į▓┘ū„▓┼─▄Ą├ĄĮĮY(ji©”)╣¹ĪŻę“┤╦Ż¼F(xi©żn)PGAŅA(y©┤)įO(sh©©)┴╦│╦öĄ(sh©┤)Ų„ļŖ┬ĘŻ¼į┌öĄ(sh©┤)īW(xu©”)║═ą┼╠¢╠Ä└Ēæ¬(y©®ng)ė├ųą▒Ż┤µī”▓ķšę▒Ē║═ė|░l(f©Ī)Ų„╩╣ė├ĪŻVirtex-II║═Spartan-3 FPGAōĒėą18Ī┴18bit│╦Ę©Ų„Ż¼╦∙ęįā╔éĆ32ūų╣Ø(ji©”)öĄ(sh©┤)ūųŽÓ│╦Ą─▀\(y©┤n)╦ŃąĶę¬╚²éĆ│╦Ę©Ų„üĒīŹ(sh©¬)¼F(xi©żn)ĪŻįSČÓą┼╠¢╠Ä└Ē╦ŃĘ©Č╝░³└©▀B│╦▀\(y©┤n)╦ŃĮY(ji©”)╣¹Ą─╣”─▄Ż¼ę“┤╦Virtex-5Ą╚Ė▀ąį─▄FPGAČ╝ŅA(y©┤)įO(sh©©)▒╗ĘQ×ķDSPŲ¼Ą─│╦öĄ(sh©┤)Ų„└█╝ėļŖ┬Ę.▀@ą®ŅA(y©┤)įO(sh©©)╠Ä└ĒĮM╝■Ż¼ę▓▒╗ĘQ×ķDSP48Ų¼Ż¼░³└©25Ī┴18bit│╦öĄ(sh©┤)Ų„ęį╝░╝ėĘ©Ų„ļŖ┬ĘŻ¼▒M╣▄─·┐╔å╬¬Ü(d©▓)╩╣ė├│╦öĄ(sh©┤)Ų„╣”─▄ĪŻ▒Ē5╦∙╩Š×ķ▓╗═¼F(xi©żn)PGAŽĄ┴ąDSPøQ▓▀ĪŻ

▒Ē5.▓╗═¼F(xi©żn)PGAĄ─DSPį┤

ēKļSÖC(j©®)┤µ╚Ī┤µā”Ų„Ż©RAMŻ®

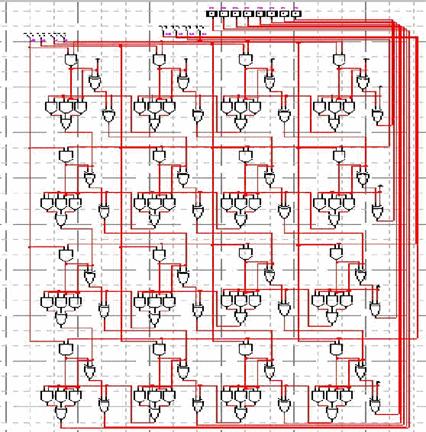

ĪĪĪĪ▀xō±FPGAĢrŻ¼ėøæøį┤╩Ū┴Ēę╗éĆąĶę¬┐╝æ]Ą─ĻP(gu©Īn)µIę“╦žĪŻŪČ╚ļFPGAąŠŲ¼ųąĄ─ė├æ¶ūįČ©┴xļSÖC(j©®)┤µ╚Ī┤µā”Ų„Ż©RAMŻ®Ż¼ī”ā”┤µöĄ(sh©┤)ō■(j©┤)įO(sh©©)ų├╗“ŲĮąąŁh(hu©ón)┬Ęų«ķgé„╦═öĄ(sh©┤)ųĄ║▄ėąÄ═ų·ĪŻ╗∙ė┌FPGAŽĄ┴ąŻ¼─·┐╔į┌16╗“36kbĮM╝■ųąįO(sh©©)ų├░Õ▌dRAMŻ¼╗“š▀╩╣ė├ė|░l(f©Ī)Ų„ęįöĄ(sh©┤)ĮMüĒł╠(zh©¬)ąąöĄ(sh©┤)ō■(j©┤)įO(sh©©)ų├Ż╗╚╗Č°Ż¼ī”ė┌FPGA▀ē▌ŗį┤üĒšfŻ¼┤¾ą═öĄ(sh©┤)ĮM║▄┐ņŠ═ūāĄ├╩«ĘųĪ░╔▌│▐Ī▒ĪŻė╔100éĆ32ūų╣Ø(ji©”)į¬╦žöĄ(sh©┤)ĮM┐╔Ž¹║─Virtex-II 1000 FPGAųą│¼▀^30ŻźĄ─ė|░l(f©Ī)Ų„Ż¼╗“š▀š╝ė├╔┘ė┌1ŻźĄ─ŪČ╚ļ╩ĮēKRAM.DSP╦ŃĘ©═©│ŻąĶę¬ūĘ█Öš¹éĆöĄ(sh©┤)ō■(j©┤)ēK╗“╩ŪÅ═(f©┤)ļsĄ╚╩ĮĄ─ŽĄöĄ(sh©┤)Ż¼Č°į┌ø]ėą░Õ▌d┤µā”Ų„ŪķørŽ┬Ż¼įSČÓ╠Ä└Ē╣”─▄į┌FPGAąŠŲ¼Ą─ė▓╝■▀ē▌ŗļŖ┬ĘųąČ╝▓╗▀mė├ĪŻłD16╦∙╩Š×ķ╩╣ė├ēKRAMūxīæ┤µā”Ų„Ą─łDą╬╗»╣”─▄ĪŻ

ĪĪĪĪ═¼śėŻ¼─Ńę▓┐╔ęį╩╣ė├ā╚(n©©i)┤µēKŻ¼īóę╗Č╬═Ļš¹ų▄Ų┌┤µā”×ķöĄ(sh©┤)ųĄ║═╦„ę²Ą─Ēśą“▒ĒŻ¼×ķ░Õ▌dą┼╠¢░l(f©Ī)╔·Ų„┤µā”ų▄Ų┌ąį▓©ą╬öĄ(sh©┤)ō■(j©┤)ĪŻ▌ö│÷ą┼╠¢Ą─ūŅĮKŅl┬╩ė╔Öz╦„öĄ(sh©┤)ųĄĄ─╦┘Č╚øQČ©Ż¼▀@śė─·Š═┐╔ė├┤╦ĘĮĘ©äėæB(t©żi)Ė─ūā▌ö│÷Ņl┬╩Ż¼Č°▓╗ąĶę¬▌ö╚ļ▓©ą╬ųąĄ─╝▒äĪūā╗»ĪŻ

łD16.ė├ė┌Ž╚▀M(j©¼n)Ž╚│÷ŠÅø_Ų„Ą─ēKRAM╣”─▄

ĪĪĪĪFPGA╣╠ėąĄ─▓óąął╠(zh©¬)ąąę¬Ū¾▀ē▌ŗļŖ┬ʬÜ(d©▓)┴óį¬╝■┐╔į┌▓╗ė├Ģrķg├}ø_Ž┬“ī(q©▒)äėĪŻį┌▓╗═¼▀\(y©┤n)ąą╦┘Č╚Ž┬Ą─▀ē▌ŗļŖ┬Ęų«ķgé„▀föĄ(sh©┤)ō■(j©┤)╩Ū║▄╝¼╩ųĄ─ĪŻ╩╣ė├Ž╚▀M(j©¼n)Ž╚│÷Ż©FIFOŻ®ŠÅø_Ų„ĢrŻ¼░Õ▌d┤µā”Ų„┐╔ė├üĒ╩Ūé„▌öĖ³╝ėŲĮĘĆ(w©¦n)ĪŻ╚ńłD16╦∙╩ŠŻ¼ė├æ¶┐╔ęįīóFIFOŠÅø_Ų„┼õų├│╔▓╗═¼┤¾ąĪęį┤_▒ŻöĄ(sh©┤)ō■(j©┤)į┌FPGAąŠŲ¼Ą─ĘŪ═¼▓Į▓┐╝■ķg▓╗Ģ■üG╩¦ĪŻ▒Ē6╦∙╩Š×ķŪČ╚ļ▓╗═¼F(xi©żn)PGAŽĄ┴ąĄ─ė├æ¶┐╔įO(sh©©)ų├┐ņRAMĪŻ

▒Ē6.▓╗═¼F(xi©żn)PGAĄ─ėøæøį┤

┐éĮY(ji©”)

ĪĪĪĪļSų°Ė▀Č╦╝╝ąg(sh©┤)Ą─░l(f©Ī)š╣ęį╝░ą┬Ė┼─ŅĄ─╔Ņ╚ļĖ┼└©Ż¼F(xi©żn)PGA╝╝ąg(sh©┤)Ąž▓╔ė├īó▓╗öÓį÷╝ėĪŻ╚╗Č°╠ĮŠ┐FPGAŲõųąŖW├žŻ¼Ėąć@▀@╣ĶŲ¼ųąį┌ĘĮ┐“łDķgģRŠÄ│÷Ą─ūā╗»Ż¼ę▓╩Ū╩«Ęųųžę¬Ą─ĪŻį┌░l(f©Ī)š╣ļAČ╬Ż¼╚ń╣¹─·Č«Ą├╚ń║╬└¹ė├║═ā×(y©Łu)╗»┘Yį┤Ż¼▒╚▌^║═▀xō±ė|░l(f©Ī)Ų„Īó▓ķšę▒ĒĪó│╦öĄ(sh©┤)Ų„║═ēKRAMĄ╚ė▓╝■ųĖś╦(bi©Īo)╩Ū╩«ĘųėąÄ═ų·Ą─ĪŻ▀@ą®╗∙▒ŠĄ─╣”─▄ēK▓ó▓╗╩Ū░³║¼╦∙ėą┘Yį┤Ą─═Ļš¹ŪÕå╬Ż¼Č°Ūę▀@Ų¬░ūŲżĢ°▓óø]ėą░³║¼ī”╦∙ėąFPGA▓┐╝■Ą─ėæšōĪŻė├æ¶┐╔ęį═©▀^Ž┬├µĄ─═Ų╦]┘Yį┤Ż¼└^└m(x©┤)īW(xu©”)┴Ģ(x©¬)ĻP(gu©Īn)ė┌FPGA║═öĄ(sh©┤)ūųė▓╝■įO(sh©©)ėŗ(j©¼)Ą─ų¬ūRĪŻ

ėęÖ┌

ėęÖ┌

╝ė║├ėč

╝ė║├ėč  ░l(f©Ī)Č╠ą┼

░l(f©Ī)Č╠ą┼

Post ByŻ║2010-11-12 14:38:51

Post ByŻ║2010-11-12 14:38:51