ś╦Ņ}Ż║╗∙ė┌TI C6000ŽĄ┴ąDSPĄ─CŻ»C++│╠ą“ā×╗»╝╝ąg

š¬ ꬯║į┌¼F┤·DSPĄ─ķ_░lųąŻ¼įĮüĒįĮČÓĄž▓╔ė├CŻ»c++ū„×ķķ_░lšZčįŻ¼Č°CŻ»C++│╠ą“Ą─ā×╗»│╔×ķDSPĪ»▄ø╝■ķ_░lĄ─ųžę¬Łh╣ØĪŻį┌┤╦ĮķĮBTI C6000Ą─▄ø╝■ķ_░l┴„│╠Ż¼ųž³cėæšōC6000ŽĄ┴ąĄ─CŻ»C++│╠ą“ā×╗»╝╝ągŻ¼░³└©ā×╗»┴„│╠Ż¼CŻ»C++┤·┤aā×╗»ĘĮĘ©Ż¼ŠÄīæŠĆą╬ģRŠÄ┤·┤aā×╗»ĘĮĘ©Ą╚ĪŻ×ķDSPĄ─C/C++▄ø╝■ķ_░l╠ß╣®┴╦╚½├µĄ─│╠ą“ā×╗»╝╝ąg║═ĘĮĘ©Ż¼ī”īŹļHŽĄĮyĄ─ķ_░lŠ▀ėąųžę¬Ą─¼FīŹęŌ┴xĪŻ

ĻPµIį~Ż║C6000Ż╗│╠ą“ā×╗»Ż╗▄ø╝■┴„╦«Ż╗ŠĆąįģRŠÄ

0 ę² čį

─┐Ū░į┌DSPŲĮ┼_╔ŽŠÄ│╠ČÓ╩╣ė├ģRŠÄšZčį┼cCšZčįŻ¼×ķ┴╦ūĘŪ¾┤·┤aĄ─Ė▀ą¦Ż¼▀^╚źę╗░Ńė├ģRŠÄšZčįüĒŠÄųŲĪŻDSP│╠ą“ģRŠÄšZčį║åØŹĖ▀ą¦Ż¼─▄ē“ų▒Įė▓┘ū„DSPĄ─ā╚▓┐╝─┤µŲ„Īó┤µā”┐šķgĪó═ŌįOŻ¼Ą½┐╔ūxąįĪó┐╔ą▐Ė─ąįĪó┐╔ęŲų▓ąį▌^▓ŅŻ╗ļSų°DSPæ¬ė├ĘČć·▓╗öÓčė╔ņŻ¼æ¬ė├Ą─╚š┌ģÅ═ļsŻ¼ģRŠÄšZčį│╠ą“į┌┐╔ūxąįĪó┐╔ą▐Ė─ąįĪó┐╔ęŲų▓ąį║═┐╔ųžė├ąįĄ─╚▒³c╚šęµ═╗│÷Ż¼▄ø╝■ąĶŪ¾┼c▄ø╝■╔·«a┴”ų«ķgĄ─├¼Č▄╚šęµć└ųžĪŻę²╚ļĖ▀╝ēšZčį(╚ńCšZčįŻ¼C++Ż¼Java)Ż¼┐╔ęįĮŌøQįō├¼Č▄ĪŻį┌Ė▀╝ēšZčįųąŻ¼CšZčį╩Ūę╗ĘN▌^×ķĖ▀ą¦Ą─Ė▀╝ēšZčįŻ¼į┌┐╔ūxąįĪó┐╔ęŲų▓ąįĄ╚ĘĮ├µā×ė┌ģRŠÄųĖ┴ŅĪŻĖ„éĆDSPąŠŲ¼╣½╦ŠČ╝ŽÓ└^═Ų│÷┴╦ŽÓæ¬Ą─CšZčįŠÄūgŲ„ĪŻ

Ą½ė╔ė┌DSFĮYśŗĄ─╠ž╩ŌąįŻ¼╩╣Ą├įōŲĮ┼_╔ŽĄ─CšZčįŠÄūgŲ„¤oĘ©│õĘų░lō]DSPŲ„╝■Ą─ąį─▄ā×ä▌ĪŻ═¼śė╣”─▄Ą─CšZčį│╠ą“Ż¼ą¦┬╩═∙═∙ų╗ėąų▒ĮėĢ°īæĄ─ģRŠÄ│╠ą“Ą─ÄūĘųų«ę╗╔§ų┴Äū╩«Ęųų«ę╗Ż¼ę“┤╦ėą▒žę¬Ė∙ō■DSPĄ─╠žąįī”CšZčįŠÄīæĄ─│╠ą“▀Mąą▀Mę╗▓ĮĄ─ā×╗»ĪŻ

l TMS320C6000╠Ä└ĒŲ„ĮķĮB

TMS320C6000╩ŪTMS320ŽĄ┴ą«aŲĘųąĄ─ą┬ę╗┤·Ė▀ąį─▄DSPąŠŲ¼Ż¼╣▓Ęų×ķā╔┤¾ŽĄ┴ąĪŻŲõųąČ©³cŽĄ┴ą×ķTMS320C62xx║═TMS320C64xxŻ╗ĖĪ³cŽĄ┴ą×ķTMS320C67xxĪŻė╔ė┌TMS320C6000Ą─ķ_░lų„ę¬├µŽ“öĄō■├▄╝»ą═╦ŃĘ©Ż¼╦³ėąų°žSĖ╗Ą─ā╚▓┐┘Yį┤║═ÅŖ┤¾Ą─▀\╦Ń─▄┴”Ż¼╦∙ęį▒╗ÅVĘ║Ąžæ¬ė├ė┌öĄūų═©ą┼║═łDŽ±╠Ä└ĒĄ╚ŅIė“ĪŻ

C6000ŽĄ┴ąCPUųąĄ─8éĆ╣”─▄å╬į¬┐╔ęį▓óąą▓┘ū„Ż¼▓óŪęŲõųąā╔éĆ╣”─▄å╬į¬×ķė▓╝■│╦Ę©▀\╦Ńå╬į¬Ż¼┤¾┤¾Ąž╠ßĖ▀┴╦│╦Ę©╦┘Č╚ĪŻDSP▓╔ė├Š▀ėą¬Ü┴ó│╠ą“┐éŠĆ║═öĄō■┐éŠĆĄ─╣■Ę┐éŠĆĮYśŗŻ¼āHŲ¼ā╚│╠ą“┐éŠĆīÆČ╚Š═┐╔▀_ĄĮ256╬╗Ż¼╝┤├┐ų▄Ų┌┐╔▓óąął╠ąą8Śl32╬╗ųĖ┴ŅŻ╗Ų¼ā╚ā╔╠ūöĄō■┐éŠĆĄ─īÆČ╚Ęųäe×ķ32╬╗Ż╗┤╦═ŌŻ¼DSP▀Ćėąę╗╠ū32╬╗DMAīŻė├┐éŠĆė├ė┌é„▌öĪŻņ`╗ŅĄ─┐éŠĆĮYśŗ╩╣Ą├öĄō■Ų┐Ņiī”ŽĄĮyąį─▄Ą─Ž▐ųŲ┤¾┤¾ŠÅĮŌĪŻC6000Ą─═©ė├╝─┤µŲ„ĮM─▄ų¦│ų32╬╗║═40╬╗Č©³cöĄō■▓┘ū„Ż¼┴Ē═ŌC67xx║═C64xx▀ĆĘųäeų¦│ų64╬╗ļpŠ½Č╚öĄō■║═64╬╗ļpūųČ©³cöĄō■▓┘ū„ĪŻ│²┴╦ČÓ╣”─▄å╬į¬═ŌŻ¼┴„╦«╝╝ąg╩Ū╠ßĖ▀DSP│╠ą“ł╠ąąą¦┬╩Ą─┴Ēę╗ų„ę¬╩ųČ╬ĪŻė╔ė┌TMS320C6000Ą─╠ž╩ŌĮYśŗŻ¼╣”─▄å╬į¬═¼Ģrł╠ąąĄ─Ė„ĘN▓┘ū„┐╔ė╔VLlWķLųĖ┴ŅĘų┼õ─ŻēKüĒ═¼▓Įł╠ąąŻ¼╩╣8Śl▓óąąųĖ┴Ņ═¼Ģr═©▀^┴„╦«ŠĆĄ─├┐éĆ╣Ø┼─Ż¼śO┤¾Ąž╠ßĖ▀┴╦ÖCŲ„Ą─═╠═┬┴┐ĪŻ

2 C6000▄ø╝■ķ_░l┴„│╠

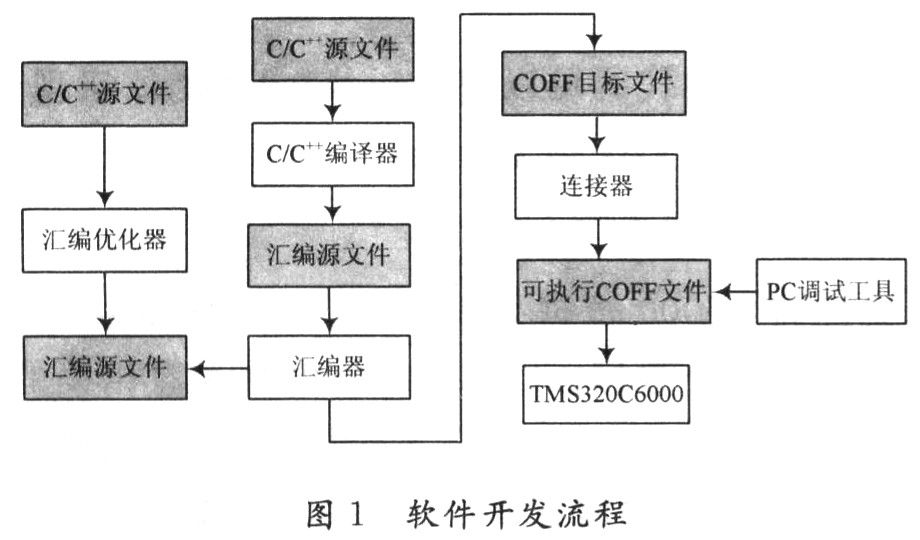

łD1×ķC6000Ą─▄ø╝■ķ_░l┴„│╠łDĪŻłDųąĻÄė░▓┐Ęų╩Ūķ_░lC┤·┤aĄ─│ŻęÄ┴„│╠Ż¼Ųõ╦¹▓┐Ęųė├ė┌▌oų·║═╝ė╦┘ķ_░lėæ│╠Ż«

CŻ»C++į┤╬─╝■╩ūŽ╚Įø▀^CŻ»C++ŠÄūgŲ„(CŻ»C++cornpiler)▐DōQ×ķC6000ģRŠÄį┤┤·┤aĪŻŠÄūgŲ„Īóā×╗»Ų„(optimizer)║═Į╗»B╣żŠ▀╩ŪCŻ»C++ŠÄūgŲ„Ą─ĮM│╔▓┐ĘųĪŻŠÄūgŲ„╩╣ė├æ¶─▄ę╗▓Į═Ļ│╔ŠÄūgĪóģRŠÄ║═▀BĮėŻ╗ā×╗»Ų„š{š¹║Žą▐Ė─┤·┤aęį╠ßĖ▀C│╠ą“Ą─ą¦┬╩Ż╗Į╗»B╣żŠ▀░čCŻ»C++šZŠõ║═ī”æ¬Ą─ģRŠÄšZŠõĮ╗»B┴ą│÷ĪŻ

ģRŠÄį┤┤·┤aį┘Įø▀^ģRŠÄŲ„(Assembier)ĘŁūg×ķÖCŲ„šZčį─┐ś╦╬─╝■ĪŻÖCŲ„šZčį╩Ū╗∙ė┌═©ė├─┐ś╦╬─╝■Ė±╩Į(Common Object File FormatŻ¼COFF)Ą─ĪŻ

▀BĮėŲ„(Linker)▀BĮė─┐ś╦╬─╝■Ż¼╔·│╔ę╗éĆ┐╔ł╠ąą╬─╝■ĪŻ╦³ę¬═Ļ│╔ĄžųĘĄ─ųžĘų┼õ(Relocation)║═ĮŌ╬÷═Ō▓┐ę²ė├(Resolve External References)ĪŻ

Ą├ĄĮ┐╔ł╠ąą╬─╝■ų«║¾Š═┐╔ęį▀Mąąš{įćĪŻ┐╔ė├▄ø╝■Ę┬šµŲ„(Simulator)į┌PCÖC╔Žī”ųĖ┴Ņ║═▀\ąąĢrķg▀MąąŠ½┤_Ę┬šµŻ╗ė├XDSė▓╝■Ę┬šµŲ„(Emulator)į┌─┐ś╦░Õ╔Ž▀Mąąš{įćĪŻ

š{įć═©▀^║¾╝┤┐╔Ž┬▌dĄĮ─┐ś╦░Õ▀Mąą¬Ü┴ó▀\ąąĪŻ

3 │╠ą“ā×╗»┴„│╠╝░ĘĮĘ©

3Ż«1 │╠ą“ā×╗»ļAČ╬

ė╔ė┌DSPæ¬ė├Ą─Å═ļsČ╚Ż¼į┌ė├CšZčį▀MąąDSP▄ø╝■ķ_░lĢrŻ¼ę╗░ŃŽ╚į┌╗∙ė┌═©ė├╬ó╠Ä└ĒŲ„Ą─PCÖC╗“╣żū„šŠ╔Žī”╦ŃĘ©▀MąąĘ┬šµŻ¼Ę┬šµ═©▀^║¾į┘īóC│╠ą“ęŲų▓ĄĮDSPŲĮ┼_ųąĪŻ

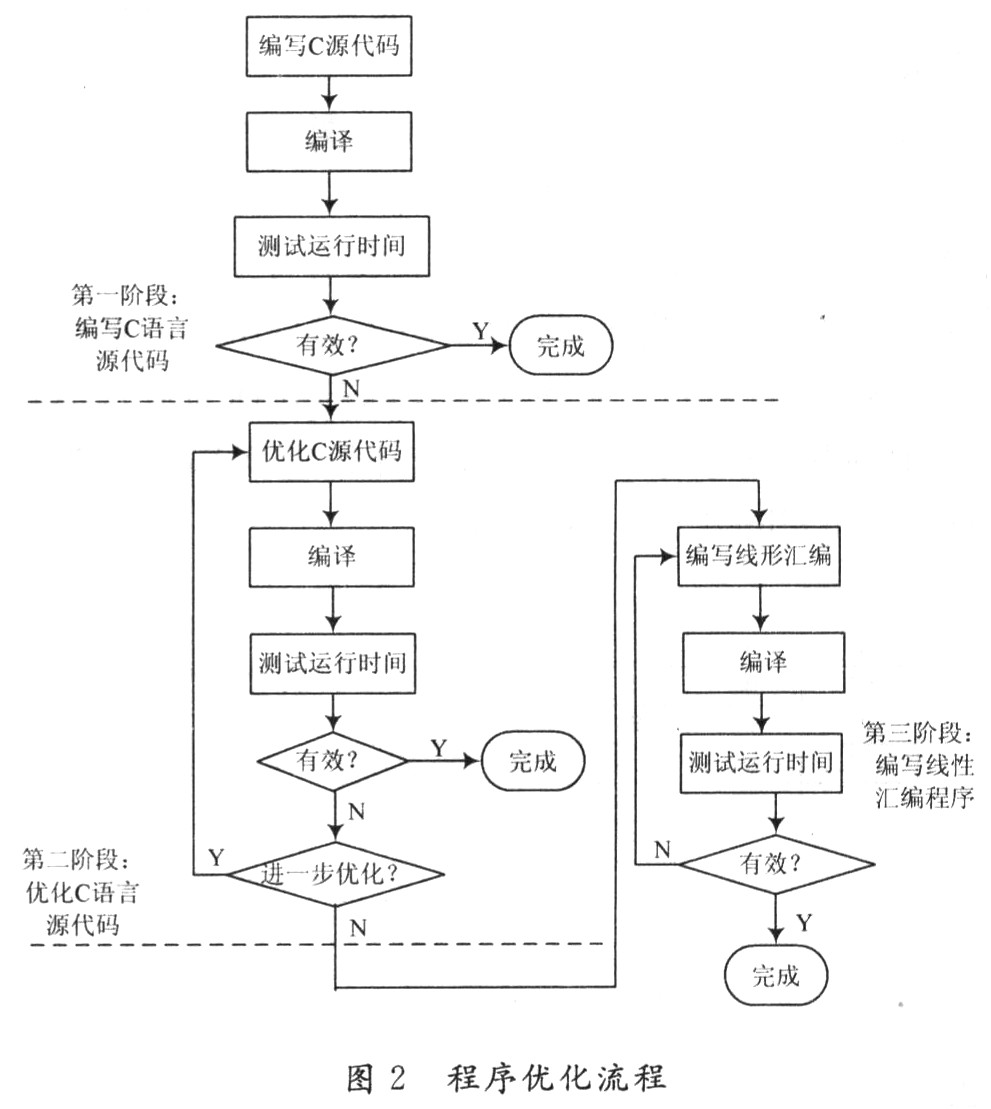

╦∙ęįŻ¼DSPĄ─▄ø╝■ķ_░l┼cā×╗»┴„│╠ų„ę¬Ęų×ķ3éĆļAČ╬Ż║C┤·┤aķ_░lļAČ╬Ż╗C┤·┤aā×╗»ļAČ╬Ż╗╩ų╣żģRŠÄ┤·┤aųžŠÄīæļAČ╬ĪŻ╚ńłD2╦∙╩ŠĪŻ

į┌łD2ųąŻ¼Ą┌ę╗ļAČ╬Ż║ø]ėąC6000ų¬ūRĄ─ė├æ¶─▄ķ_░lūį╝║Ą─C┤·┤aŻ¼╚╗║¾╩╣ė├CCSųąĄ─┤·┤aŲ╩╬÷╣żŠ▀Ż¼┤_Č©C┤·┤aųą┐╔─▄┤µį┌Ą─Ą═ą¦┬╩Č╬Ż¼×ķ▀Mę╗▓Į┤·┤aā×╗»ū÷║├£╩éõĪŻĄ┌Č■ļAČ╬Ż║C┤·┤aā×╗»ļAČ╬ĪŻį┌▀@éĆļAČ╬Ż¼ų„ę¬└¹ė├intrinsics║»öĄęį╝░ŠÄūgŲ„ŠÄūg▀xĒŚüĒ╠ßĖ▀┤·┤aĄ─ąį─▄ĪŻā×╗»║¾└¹ė├▄ø╝■─ŻöMŲ„Öz▓ķ┤·┤aĄ─ą¦┬╩Ż¼╚ń╚į▓╗─▄▀_ĄĮŲ┌═¹Ą─ą¦┬╩Ż¼ät▀M╚ļĄ┌╚²ļAČ╬ĪŻĄ┌╚²ļAČ╬Ż║īæŠĆąįģRŠÄā×╗»ĪŻį┌▀@éĆļAČ╬ųąŻ¼ė├æ¶░čūŅ║─┘MĢrķgĄ─┤·┤a│ķ╚Ī│÷üĒŻ¼ųžą┬ė├ŠĆąįģRŠÄīæŻ¼╚╗║¾╩╣ė├ģRŠÄā×╗»Ų„ā×╗»▀@ą®┤·┤aĪŻį┌Ą┌ę╗┤╬īæŠĆąįģRŠÄĢrŻ¼┐╔ęį▓╗┐╝æ]┴„╦«ŠĆ║═╝─┤µŲ„Ęų┼õĪŻ╚╗║¾Ż¼╠ßĖ▀ŠĆąįģRŠÄ┤·┤aąį─▄Ż¼═∙┤·┤aųą╠Ē╝ėĖ³ČÓĄ─╝Ü╣ØŻ¼╚ńĘų┼õ╝─┤µŲ„Ą╚ĪŻė╔ė┌▀@ę╗ļAČ╬╦∙ąĶĄ─Ģrķgę¬▒╚Ą┌Č■ļAČ╬ČÓŻ¼╦∙ęįš¹éĆ┤·┤aĄ─ā×╗»▒M┴┐Ę┼į┌Ą┌Č■ļAČ╬üĒ═Ļ│╔Ż¼Č°╔┘╩╣ė├ŠĆąįģRŠÄ┤·┤aā×╗»ĪŻ

3Ż«2 CŻ»C++┤·┤aā×╗»ĘĮĘ©

×ķ┴╦╩╣CŻ»C++┤·┤a½@Ą├ūŅ║├Ą─ąį─▄Ż¼┐╔ęį╩╣ė├ŠÄūg▀xĒŚĪó▄ø╝■┴„╦«Īóā╚┬ō║»öĄ║═裣hš╣ķ_Ą╚ĘĮĘ©üĒī”┤·┤a▀Mąąā×╗»Ż¼ęį╠ßĖ▀┤·┤ał╠ąą╦┘Č╚Ż¼▓ó£pąĪ┤·┤a│▀┤ńĪŻ

3Ż«2Ż«1 ŠÄūgŲ„▀xĒŚā×╗»

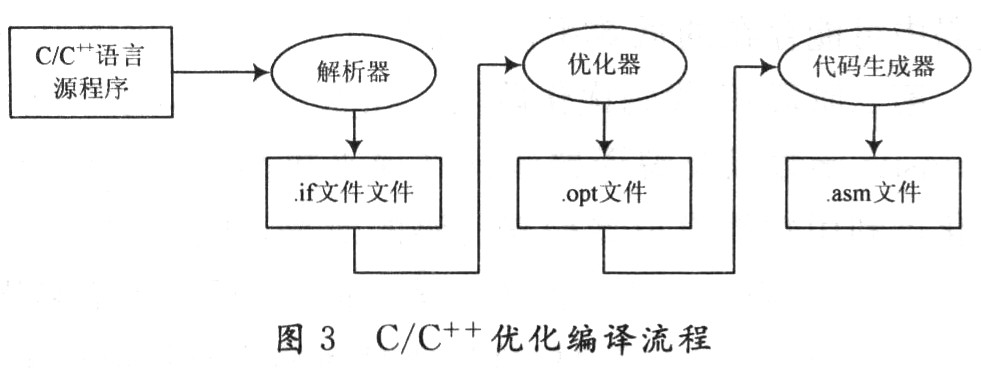

CŻ»C++ŠÄūgŲ„┐╔ęįī”┤·┤a▀Mąą▓╗═¼╝ēäeĄ─ā×╗»ĪŻĖ▀╝ēā×╗»ė╔īŻķTĄ─ā×╗»Ų„═Ļ│╔Ż¼Ą═╝ēĄ─║═─┐ś╦DSPėąĻPĄ─ā×╗»ė╔┤·┤a╔·│╔Ų„═Ļ│╔ĪŻłD3×ķŠÄūgŲ„Īóā×╗»Ų„║═┤·┤a╔·│╔Ų„Ą─ł╠ąąłDĪŻ

«öā×╗»Ų„▒╗╝ż╗ŅĢrŻ¼īó═Ļ│╔łD3╦∙╩ŠĄ─▀^│╠ĪŻCŻ»C++šZčįį┤┤·┤a╩ūŽ╚═©▀^ę╗éĆ═Ļ│╔ŅA╠Ä└ĒĄ─ĮŌ╬÷Ų„(Parser)Ż¼╔·│╔ę╗éĆųąķg╬─╝■(Ż«if)ū„×ķā×╗»Ų„(Optimi-zer)Ą─▌ö╚ļĪŻā×╗»Ų„╔·│╔ę╗éĆā×╗»╬─╝■(Ż«opt)Ż¼▀@éĆ╬─╝■ū„×ķ═Ļ│╔▀Mę╗▓Įā×╗»Ą─┤·┤a╔·│╔Ų„(Co

ūŅ║åå╬ł╠ąąā×╗»Ą─ĘĮĘ©╩Ū▓╔ė├cl6xŠÄūg│╠ą“Ż¼į┌├³┴ŅąąįOų├ę╗On▀xĒŚ╝┤┐╔ĪŻn╩Ūā×╗»Ą─╝ēäe(n×ķ0Ż¼1Ż¼2Ż¼3)Ż¼╦³┐žųŲā×╗»Ą─ŅÉą═║═│╠Č╚ĪŻ

3Ż«2Ż«2 ▄ø╝■┴„╦«ā×╗»

▄ø╝■┴„╦«╩ŪŠÄ┼┼裣hųĖ┴ŅŻ¼╩╣裣hĄ─ČÓ┤╬Ą³┤·▓óąął╠ąąĄ─╝╝ągĪŻ╩╣ė├ę╗02║═ę╗03▀xĒŚŠÄūgCŻ»C++│╠ą“ĢrŻ¼ŠÄūgŲ„Š═Å─│╠ą“ųą╩š╝»ą┼ŽóŻ¼ćLįćī”│╠ą“裣hū÷▄ø╝■┴„╦«ĪŻ

łD4’@╩Šę╗éĆ▄ø╝■┴„╦«čŁŁhĪŻłD4ųąAŻ¼BŻ¼CŻ¼D║═E▒Ē╩Š1┤╬Ą³┤·ųąĄ─Ė„ŚlųĖ┴ŅŻ╗A1Ż¼A2Ż¼A3Ż¼A4║═A5▒Ē╩Šę╗ŚlųĖ┴Ņł╠ąąĄ─Ė„ļAČ╬ĪŻčŁŁhųąŻ¼ę╗éĆų▄Ų┌ūŅČÓ┐╔▓óąął╠ąą5ŚlųĖ┴ŅŻ¼╝┤łDųąĻÄė░▓┐Ęų╦∙╩ŠĄ─裣h║╦(Loop Kernel)▓┐ĘųĪŻčŁŁh║╦Ū░├µĄ─▓┐ĘųĘQ×ķ┴„╦«čŁŁh╠Ņ│õ(Pipelined Loop Prolog)Ż¼čŁŁh║╦║¾├µ▓┐ĘųĘQ×ķ裣h┼┼┐š(Pipelined Loop Epilog)ĪŻ

3Ż«2Ż«3 ā╚┬ō║»öĄā×╗»

═©▀^Ž┬├µĄ─ĘĮĘ©Ė─▀MCšZčį│╠ą“Ż¼┐╔╩╣ŠÄūg│÷Ą─┤·┤aąį─▄’@ų°╠ßĖ▀Ż║

(1)╩╣ė├intrinsics(ā╚┬ō║»öĄ)╠µ┤·Å═ļsĄ─CŻ»C++┤·┤aŻ╗

(2)╩╣ė├ūų(Word)įLå¢┤µĘ┼į┌32╬╗╝─┤µŲ„Ą─Ė▀16╬╗║═Ą═16╬╗ūųČ╬Ą─öĄō■Ż╗

(3)╩╣ė├ļpūųįLå¢┤µĘ┼į┌64╬╗╝─┤µŲ„Ą─32╬╗öĄō■(āHųĖC64xxŻ»C67XX)ĪŻ

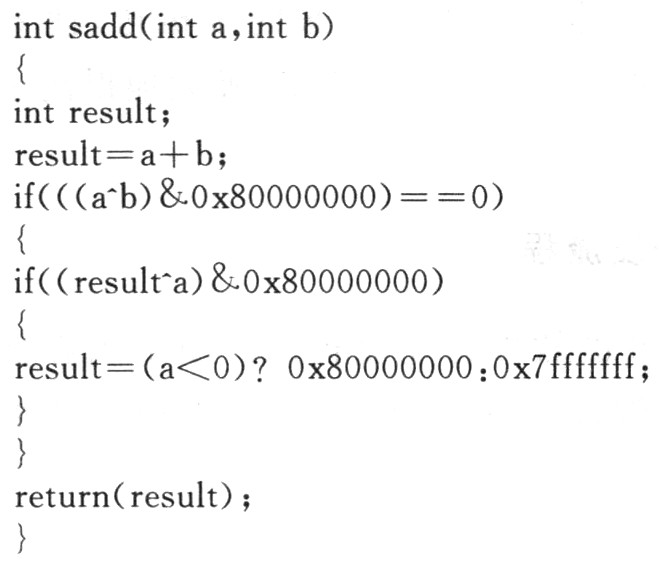

C6000ŠÄūgŲ„╠ß╣®┴╦įSČÓā╚┬ō║»öĄŻ¼╦³éāų▒Įėī”æ¬ų°C62XŻ»C64XŻ»C67XųĖ┴Ņ┐╔┐ņ╦┘ā×╗»C┤·┤aĪŻ▀@ą®ā╚┬ō║»öĄ▓╗ęūė├CŻ»C++šZčįīŹ¼FŲõ╣”─▄ĪŻā╚┬ō║»öĄė├Ū░Ž┬äØŠĆĪ░_Ī▒╠žäeś╦╩ŠŻ¼Ųõ╩╣ė├ĘĮĘ©┼cš{ė├║»öĄę╗śėĪŻ└²╚ńCšZčįĄ─’¢║═╝ėĘ©ų╗─▄īæ×ķąĶę¬ČÓų▄Ų┌Ą─║»öĄŻ║

▀@Č╬Å═ļsĄ─┤·┤a┐╔ęįė├_sadd()ā╚┬ō║»öĄīŹ¼FŻ¼╦³╩Ūę╗éĆå╬ų▄Ų┌Ą─C6xųĖ┴ŅĪŻ

result=_sadd(aŻ¼b)Ż╗

ę¬╠ßĖ▀C6000öĄō■╠Ä└Ē┬╩Ż¼æ¬╩╣ę╗ŚlLoadŻ»StoreųĖ┴Ņ─▄įLå¢ČÓéĆöĄō■ĪŻC6000ėą┼cā╚┬ō║»öĄŽÓĻPĄ─ųĖ┴ŅŻ¼└²╚ń_add2()Ż¼_mpyhl()Ż¼_mpylh()Ą╚Ż¼▀@ą®▓┘ū„öĄęį16╬╗öĄō■ą╬╩Į┤µā”į┌32╬╗╝─┤µŲ„Ą─Ė▀╬╗▓┐Ęų║═Ą═╬╗▓┐ĘųĪŻ«ö│╠ą“ąĶę¬ī”ę╗▀B┤«Č╠ą═öĄō■▀Mąą▓┘ū„ĢrŻ¼┐╔╩╣ė├ūų1┤╬įLå¢2éĆČ╠ą═öĄō■Ż¼╚╗║¾╩╣ė├C6000ŽÓæ¬ųĖ┴ŅüĒ╠Ä└ĒöĄō■ĪŻŽÓ╦ŲĄ─į┌C64x╗“C67xųąŻ¼ėąĢrąĶꬳ╠ąą64╬╗Ą─LDDWüĒįLå¢ā╔éĆ32╬╗öĄō■Ż¼4éĆ16╬╗öĄō■Ż¼╔§ų┴8éĆ8╬╗öĄō■ĪŻ

3Ż«2Ż«4 裣hš╣ķ_

裣hš╣ķ_╩ŪĖ─▀Mąį─▄Ą─┴Ēę╗ĘNŻ¼╝┤░čąĪ裣hĄ─Ą³┤·š╣ķ_Ż¼ęįūī裣hĄ─├┐┤╬Ą³┤·│÷¼Fį┌┤·┤aųąĪŻ▀@ĘNĘĮĘ©┐╔į÷╝ė▓óąął╠ąąĄ─ųĖ┴ŅöĄĪŻ«ö├┐┤╬Ą³┤·▓┘ū„ø]ėą│õĘų└¹ė├C6000ĮYśŗĄ─╦∙ėą┘Yį┤ĢrŻ¼┐╔╩╣ė├裣hš╣ķ_╠ßĖ▀ąį─▄ĪŻ

ėą3ĘN╩╣裣hš╣ķ_Ą─ĘĮĘ©Ż║

(1)ŠÄūgŲ„ūįäėł╠ąąčŁŁhš╣ķ_Ż╗

(2)į┌│╠ą“ųą╩╣ė├UNROLLé╬ųĖ┴ŅĮ©ūhŠÄūgŲ„ū÷裣hš╣ķ_Ż╗

(3)ė├æ¶ūį╝║į┌CŻ»C++┤·┤aųąš╣ķ_ĪŻ

3Ż«3 ģRŠÄā×╗»

į┌ī”CŻ»C++┤·┤a╩╣ė├┴╦╦∙ėąĄ─CŻ»C++ā×╗»╩ųČ╬ų«║¾Ż¼╚ń╣¹╚į╚╗▓╗ØMęŌ┤·┤aĄ─ąį─▄Ż¼Š═┐╔ęįīæŠĆąįģRŠÄ│╠ą“Ż¼╚╗║¾ė├ģRŠÄā×╗»Ų„▀Mąąā×╗»Ż¼╔·│╔Ė▀ąį─▄Ą─┤·┤aĪŻ

3Ż«3Ż«1 īæŠĆąįģRŠÄ

╩╣ė├C6000Ą─Ų╩╬÷╣żŠ▀(Profiling Tools)┐╔ęįšęĄĮ┤·┤aųąūŅ║─┘MĢrķgĄ─▓┐ĘųŻ¼Š═╩Ū▀@▓┐ĘųąĶę¬ė├ŠĆąįģRŠÄųžīæĪŻŠĆąįģRŠÄ┤·┤a┼cģRŠÄį┤┤·┤aŽÓ╦ŲŻ¼Ą½╩ŪŻ¼ŠĆąįģRŠÄ┤·┤aųąø]ėąųĖ┴Ņčė▀t║═╝─┤µŲ„╩╣ė├ą┼ŽóĪŻ▀@śėū÷Ą──┐Ą─╩Ūė╔ģRŠÄā×╗»Ų„üĒ×ķūį╝║įOČ©▀@ą®ą┼ŽóĪŻ

īæŠĆąįģRŠÄ┤·┤aĢrŻ¼ąĶę¬ų¬Ą└Ż║ģRŠÄā×╗»Ų„é╬ųĖ┴ŅĪóė░ĒæģRŠÄā×╗»Ų„ąą×ķĄ─▀xĒŚĪóTMS320C6000ųĖ┴ŅĪóŠĆąįģRŠÄį┤šZŠõšZĘ©ĪóųĖČ©╝─┤µŲ„╗“╝─┤µŲ„ĮMĪóųĖČ©╣”─▄å╬į¬Īóį┤┤·┤aūóßīĄ╚ĪŻ

3Ż«3Ż«2 ģRŠÄā×╗»Ų„ā×╗»

ģRŠÄā×╗»Ų„Ą─╚╬äšų„ę¬ėąŻ║

(1)ŠÄ┼┼ųĖ┴ŅŻ¼ūŅ┤¾Ž▐Č╚Ą─└¹ė├C6000Ą─▓óąą─▄┴”Ż╗

(2)┤_▒ŻųĖ┴ŅØMūŃC6000Ą─čė▀tę¬Ū¾(Latency Requirements)Ż╗

(3)×ķį┤┤·┤aĘų┼õ╝─┤µŲ„ĪŻ

4 ĮY šZ

C6000ŽĄ┴ąĄ─DSP CŻ»c++┤·┤aā×╗»▒╚é„ĮyĄ─┤·┤aā×╗»ę¬ĘĮ▒ŃĄ─ČÓŻ¼Ą½ę¬šµš²░lō]ŲõąŠŲ¼Ą─╣żū„ą¦┬╩▀Ć╩ŪąĶę¬ę╗Č©Ą─Įø“×║═╝╝Ū╔ĪŻ▀@▓╗āHę¬Ū¾ķ_░l╚╦åT╩ņŽżŲõė▓╝■¾wŽĄŻ¼▀Ćę¬Ū¾ī”ŠÄūgŲ„Ą─ŠÄūgįŁ└Ēėąę╗Č©Ą─└ĒĮŌĪŻ┴Ē═ŌŻ¼į┌CšZčįīė├µ╔Žę¬▀_ĄĮDSPąŠŲ¼Ą─ĘÕųĄ╝┤8ŚlųĖ┴Ņ▓óąą╩Ū║▄ļyĄ─Ż¼┤¾ČÓŪķørŽ┬Č╝ų╗─▄▀_ĄĮ6Ż«7ŚlųĖ┴Ņ▓óąąĪŻį┌īŹļHķ_░lųąŻ¼╚¶ā×╗»ĮY╣¹ęč▀_ĄĮ6Ż¼7ŚlųĖ┴Ņ▓óąąģs▀ĆļxīŹĢrĄ─ę¬Ū¾ŽÓ▓Ņ║▄▀hŻ¼į┘╗©┤¾┴┐Ą─╚╦┴”╚ź┴”Ū¾▀_ĄĮ8ŚlųĖ┴Ņ▓óąą╩Ū▓╗ĮøØ·Ą─Ż¼┤╦Ģræ¬įō┐╝æ]Ųõ╦¹Ą─╝╝ągĖ─▀M╗“▓▀┬į╔ŽĄ─š{š¹ęįŪ¾▀_ĄĮ─┐Ą─ĪŻ